#### **ADVANCE INFORMATION**

# DS90LV032 3V LVDS Quad CMOS Differential Line Receiver

### **General Description**

The DS90LV032 is a quad CMOS differential line receiver designed for applications requiring ultra low power dissipation and high data rates. The device is designed to support data rates in excess of 100 Mbps (50 MHz) utilizing Low Voltage Differential Signaling (LVDS) technology.

The DS90LV032 accepts low voltage (350 mV) differential input signals and translates them to 3V CMOS output levels. The receiver supports a TRI-STATE® function that may be used to multiplex outputs. The receiver also supports OPEN, shorted and terminated (1000) input Failsafe. Receiver output will be High for all failsafe conditions.

The DS90LV032 and companion line driver (DS90LV031) provide a new alternative to high power psuedo-ECL devices for high speed point to point interface applications.

#### **Features**

- 3.3V power supply design

- > 100 Mbps (50 MHz) switching rates

- Accepts small swing (350 mV) differential signal levels

- Ultra low power dissipation

- TBD ps maximum differential skew (3.3V, 25°C)

- TBD ns maximum propagation delay

- Industrial operating temperature range (-40°C to +85°C)

- Available in surface mount packaging (SOIC)

- Pin compatible with DS26C32A, MB570 (PECL), 41LF (PECL), and DS90C032

- Supports OPEN, short and terminated input failsafe

- Compatible with IEEE 1596.3 SCI LVDS standard

- Compatible with TIA/EIA-644 LVDS standard

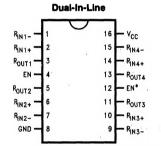

### **Connection Diagram**

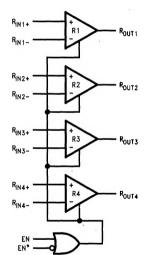

## **Functional Diagram and Truth Tables**

TL/F/12624-1

Order Number

DS90LV032TM

See NS Package Number M16A

TL/F/12624-2

#### RECEIVER

| ENABLES                                 |     | INPUTS                                       | OUTPUT |

|-----------------------------------------|-----|----------------------------------------------|--------|

| EN                                      | EN. | RIN+ - RIN-                                  | Rout   |

| L                                       | Н   | X                                            | Z      |

| All other combinations of ENABLE inputs |     | V <sub>ID</sub> ≥ 0.1V                       | Н      |

|                                         |     | $V_{ID} \le -0.1V$                           | L      |

|                                         |     | Full Failsafe<br>OPEN/SHORT<br>or Terminated | н      |