SNLS291 - APRIL 2008

# DS90CR483A / DS90CR484A 48-Bit LVDS Channel Link SER/DES – 33 - 112 MHz

Check for Samples: DS90CR483A, DS90CR484A

# **FEATURES**

- Up to 5.38 Gbits/sec Bandwidth

- 33 MHz to 112 MHz Input Clock Support

- LVDS SER/DES Reduces Cable and Connector Size

- **Pre-emphasis Reduces Cable Loading Effects**

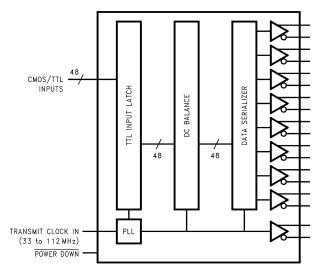

- DC Balance Data Transmission Provided by Transmitter Reduces ISI Distortion

- Cable Deskew of +/-1 LVDS Data Bit Time (up to 80 MHz Clock Rate)

- 5V Tolerant TxIN and Control Input Pins

- Flow Through Pinout for Easy PCB Design

- +3.3V Supply Voltage •

- Transmitter Rejects Cycle-to-cycle Jitter •

- Conforms to ANSI/TIA/EIA-644-1995 LVDS • Standard

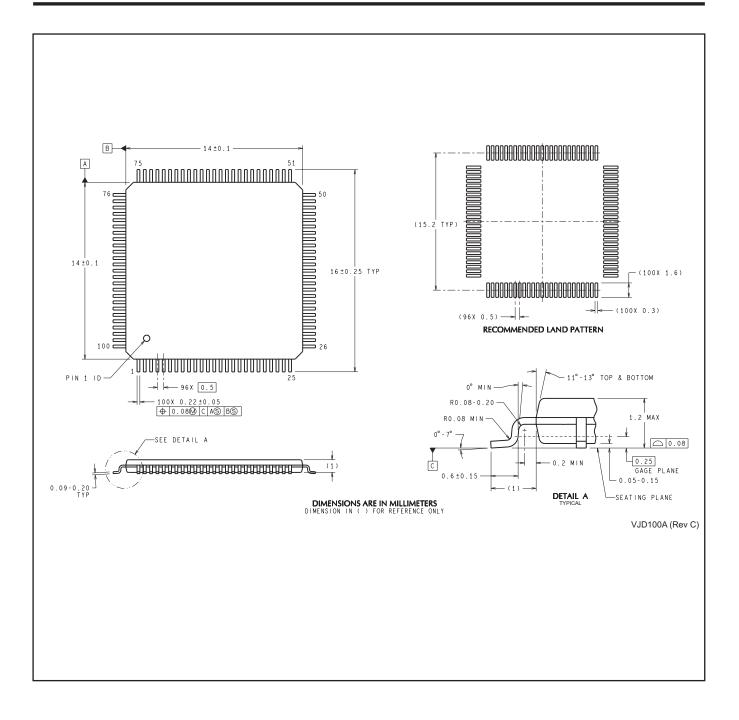

- Both Devices are Available in 100 Lead TQFP Package

# DESCRIPTION

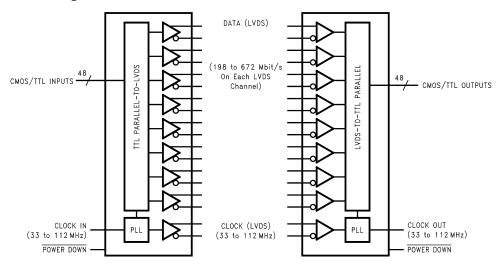

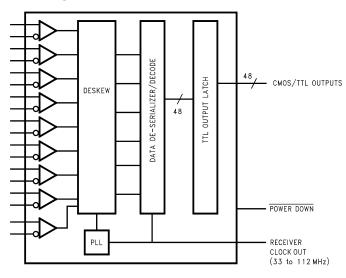

The DS90CR483A transmitter converts 48 bits of CMOS/TTL data into eight LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a ninth LVDS link. Every cycle of the transmit clock 48 bits of input data are sampled and transmitted. The DS90CR484A receiver converts the LVDS data streams back into 48 bits of CMOS/TTL data. At a transmit clock frequency of 112MHz, 48 bits of TTL data are transmitted at a rate of 672Mbps per LVDS data channel. Using a 112MHz clock, the data throughput is 5.38Gbit/s (672Mbytes/s).

The multiplexing of data lines provides a substantial cable reduction. Long distance parallel single-ended buses typically require a ground wire per active signal (and have very limited noise rejection capability). Thus, for a 48bit wide data and one clock, up to 98 conductors are required. With this Channel Link chipset as few as 19 conductors (8 data pairs, 1 clock pair and a minimum of one ground) are needed. This provides an 80% reduction in cable width, which provides a system cost savings, reduces connector physical size and cost, and reduces shielding requirements due to the cables' smaller form factor.

The 48 CMOS/TTL inputs can support a variety of signal combinations. For example, 6 8-bit words or 5 9-bit (byte + parity) and 3 controls.

The DS90CR483A/DS90CR484A chipset is improved over prior generations of Channel Link devices and offers higher bandwidth support and longer cable drive with three areas of enhancement. To increase bandwidth, the maximum clock rate is increased to 112 MHz and 8 serialized LVDS outputs are provided. Cable drive is enhanced with a user selectable pre-emphasis feature that provides additional output current during transitions to counteract cable loading effects. Optional DC balancing on a cycle-to-cycle basis, is also provided to reduce ISI (Inter-Symbol Interference). With pre-emphasis and DC balancing, a low distortion eye-pattern is provided at the receiver end of the cable. A cable deskew capability has been added to deskew long cables of pair-to-pair skew of up to +/-1 LVDS data bit time (up to 80 MHz Clock Rate). These three enhancements allow cables 5+ meters in length to be driven.

The chipset is an ideal means to solve EMI and cable size problems associated with wide, high speed TTL interfaces.

For more details, please refer to the APPLICATIONS INFORMATION section of this datasheet.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

#### **Generalized Block Diagrams**

#### **Generalized Transmitter Block Diagram**

## **Generalized Receiver Block Diagram**

SNLS291 – APRIL 2008

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### Absolute Maximum Ratings (1)(2)

| 5                                                 |                                   |

|---------------------------------------------------|-----------------------------------|

| Supply Voltage (V <sub>CC</sub> )                 | -0.3V to +4V                      |

| CMOS/TTL Input Voltage                            | -0.3V to +5.5V                    |

| LVCMOS/TTL Output Voltage                         | -0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Receiver Input Voltage                       | -0.3V to +3.6V                    |

| LVDS Driver Output Voltage                        | -0.3V to +3.6V                    |

| LVDS Output Short Circuit Duration                | Continuous                        |

| Junction Temperature                              | +150°C                            |

| Storage Temperature                               | −65°C to +150°C                   |

| Lead Temperature<br>(Soldering, 4 sec.)           |                                   |

| 100L TQFP                                         | +260°C                            |

| Maximum Package Power Dissipation Capacity @ 25°C |                                   |

| 100 TQFP Package:                                 |                                   |

| DS90CR483ANEZ                                     | 2.3W                              |

| DS90CR484ANEZ                                     | 2.3W                              |

| Package Derating:                                 |                                   |

| DS90CR483ANEZ                                     | 18.1mW/°C above +25°C             |

| DS90CR484ANEZ                                     | 18.1mW/°C above +25°C             |

| ESD Rating:                                       |                                   |

| DS90CR483A                                        |                                   |

| (HBM, 1.5kΩ, 100pF)                               | > 6 kV                            |

| (EIAJ, 0Ω, 200pF)                                 | > 300 V                           |

| DS90CR484A                                        |                                   |

| (HBM, 1.5kΩ, 100pF)                               | > 2 kV                            |

| (EIAJ, 0Ω, 200pF)                                 | > 200 V                           |

(1) "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. "Electrical Characteristics" specify conditions for device operation.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

## **Recommended Operating Conditions**

|                                                 | Min | Nom | Max | Units             |

|-------------------------------------------------|-----|-----|-----|-------------------|

| Supply Voltage (V <sub>CC</sub> )               | 3.0 | 3.3 | 3.6 | V                 |

| Operating Free Air Temperature (T <sub>A)</sub> | -10 | +25 | +70 | °C                |

| Receiver Input Range                            | 0   |     | 2.4 | V                 |

| Supply Noise Voltage                            |     |     | 100 | mV <sub>p-p</sub> |

| Input Clock (TX)                                | 33  |     | 112 | MHz               |

# Electrical Characteristics<sup>(1)</sup>

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter                  | Conditions | Min | Typ <sup>(2)</sup> | Max | Units |  |  |

|-----------------|----------------------------|------------|-----|--------------------|-----|-------|--|--|

| CMOS/TTL DO     | CMOS/TTL DC SPECIFICATIONS |            |     |                    |     |       |  |  |

| V <sub>IH</sub> | High Level Input Voltage   |            | 2.0 |                    |     | V     |  |  |

| V <sub>IL</sub> | Low Level Input Voltage    |            | GND |                    | 0.8 | V     |  |  |

Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except V<sub>TH</sub>, V<sub>TL</sub>, V<sub>OD</sub> and ΔV<sub>OD</sub>).

(2) Typical values are given for  $V_{CC} = 3.3V$  and  $T_A = +25^{\circ}C$ .

#### SNLS291 - APRIL 2008

# Electrical Characteristics<sup>(1)</sup> (continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                                                           | Conditio                                                       | ns          | Min   | Typ <sup>(2)</sup> | Max   | Units |

|------------------|---------------------------------------------------------------------|----------------------------------------------------------------|-------------|-------|--------------------|-------|-------|

| V <sub>OH</sub>  | High Level Output Voltage                                           | I <sub>OH</sub> = −0.4 mA                                      |             | 2.7   | 3.3                |       | V     |

|                  |                                                                     | I <sub>OH</sub> = −2mA                                         |             | 2.7   | 2.85               |       | V     |

| V <sub>OL</sub>  | Low Level Output Voltage                                            | I <sub>OL</sub> = 2 mA                                         |             |       | 0.1                | 0.3   | V     |

| V <sub>CL</sub>  | Input Clamp Voltage                                                 | I <sub>CL</sub> = −18 mA                                       |             |       | -0.79              | -1.5  | V     |

| I <sub>IN</sub>  | Input Current                                                       | $V_{IN} = 0.4V, 2.5V \text{ or } V_{CC}$                       |             |       | +1.8               | +15   | μA    |

|                  |                                                                     | V <sub>IN</sub> = GND                                          |             | -15   | 0                  |       | μA    |

| I <sub>OS</sub>  | Output Short Circuit<br>Current                                     | V <sub>OUT</sub> = 0V                                          |             |       |                    | -120  | mA    |

| LVDS DRIVE       | R DC SPECIFICATIONS                                                 |                                                                |             |       |                    |       |       |

| V <sub>OD</sub>  | Differential Output Voltage                                         | $R_L = 100\Omega$                                              |             | 250   | 345                | 450   | mV    |

| $\Delta V_{OD}$  | Change in V <sub>OD</sub> between<br>Complimentary Output<br>States |                                                                |             |       |                    | 35    | mV    |

| V <sub>OS</sub>  | Offset Voltage                                                      |                                                                |             | 1.125 | 1.25               | 1.375 | V     |

| ΔV <sub>OS</sub> | Change in V <sub>OS</sub> between<br>Complimentary Output<br>States |                                                                |             |       |                    | 35    | mV    |

| I <sub>OS</sub>  | Output Short Circuit<br>Current                                     | $V_{OUT} = 0V, R_L = 100\Omega$                                |             |       | -3.5               | -5    | mA    |

| I <sub>OZ</sub>  | Output TRI-STATE<br>Current                                         | $\overline{PD} = 0V, V_{OUT} = 0V \text{ or } V_{CC}$          |             |       | ±1                 | ±10   | μA    |

| LVDS RECE        | IVER DC SPECIFICATIONS                                              |                                                                |             |       |                    |       | 1     |

| V <sub>TH</sub>  | Differential Input High<br>Threshold                                | V <sub>CM</sub> = +1.2V                                        |             |       |                    | +100  | mV    |

| V <sub>TL</sub>  | Differential Input Low<br>Threshold                                 |                                                                |             | -100  |                    |       | mV    |

| I <sub>IN</sub>  | Input Current                                                       | $V_{IN} = +2.4V, V_{CC} = 3.6V$                                |             |       |                    | ±10   | μA    |

|                  |                                                                     | $V_{IN} = 0V, V_{CC} = 3.6V$                                   |             |       |                    | ±10   | μA    |

| TRANSMITT        | ER SUPPLY CURRENT                                                   |                                                                |             |       |                    |       |       |

| ICCTW            | Transmitter Supply                                                  | $R_L = 100\Omega, C_L = 5 \text{ pF},$                         | f = 33 MHz  |       | 91.4               | 140   | mA    |

|                  | Current<br>Worst Case                                               | BAL = High,<br>Worst Case Pattern                              | f = 66 MHz  |       | 106                | 160   | mA    |

|                  |                                                                     | (Figure 1 Figure 2)                                            | f = 112 MHz |       | 155                | 210   | mA    |

| ICCTZ            | Transmitter Supply<br>Current<br>Power Down                         | PD = Low<br>Driver Outputs in TRI-STATE during power down Mode |             |       | 5                  | 50    | μA    |

| RECEIVER S       | SUPPLY CURRENT                                                      |                                                                |             |       |                    |       |       |

| ICCRW            | Receiver Supply Current                                             | $C_L = 8 \text{ pF}, \text{ BAL} = \text{High},$               | f = 33 MHz  |       | 125                | 150   | mA    |

|                  | Worst Case                                                          | Worst Case Pattern                                             | f = 66 MHz  |       | 200                | 210   | mA    |

|                  |                                                                     | See (Figure 1 Figure 3) $f = 112 \text{ MHz}$                  |             |       | 250                | 280   | mA    |

| ICCRZ            | Receiver Supply Current<br>Power Down                               | PD = Low<br>Receiver Outputs stay low durir                    |             |       | 200                | 100   | μΑ    |

## **Recommended Transmitter Input Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol    | Parameter                                      | Min   | Тур  | Max   | Units |

|-----------|------------------------------------------------|-------|------|-------|-------|

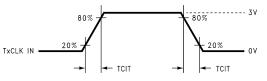

| TCIT      | TxCLK In Transition Time (Figure 4)            | 1.0   | 2.0  | 3.0   | ns    |

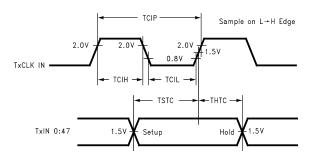

| TCIP High | TxCLK In Period, PLLSEL = High Gear (Figure 5) | 8.928 | Т    | 26.3  | ns    |

| TCIP Low  | TxCLK In Period, PLLSEL = Low Gear (Figure 5)  | 25    | Т    | 30.3  | ns    |

| TCIH      | TxCLK In High Time (Figure 5)                  | 0.35T | 0.5T | 0.65T | ns    |

| TCIL      | TxCLK In Low Time (Figure 5)                   | 0.35T | 0.5T | 0.65T | ns    |

www.ti.com

## **Recommended Transmitter Input Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter            | Min | Тур | Max | Units |

|--------|----------------------|-----|-----|-----|-------|

| TXIT   | TxIN Transition Time | 1.5 |     | 6.0 | ns    |

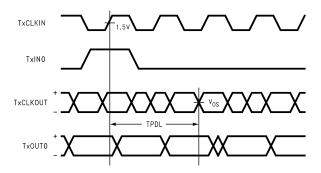

## **Transmitter Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                                                               |                      | Min            | Тур           | Max            | Units |

|--------|-------------------------------------------------------------------------|----------------------|----------------|---------------|----------------|-------|

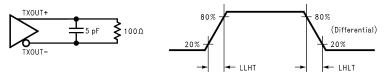

| LLHT   | LVDS Low-to-High Transition Time, (Figure<br>PRE = 0.75V (disabled)     | 2),                  |                | 0.14          | 0.7            | ns    |

|        | LVDS Low-to-High Transition Time, (Figure<br>PRE = Vcc (max)            | 2),                  |                | 0.11          | 0.6            | ns    |

| LHLT   | LVDS High-to-Low Transition Time, (Figure 2),<br>PRE = 0.75V (disabled) |                      |                | 0.16          | 0.8            | ns    |

|        | LVDS High-to-Low Transition Time, (Figure 2),<br>PRE = Vcc (max)        |                      |                | 0.11          | 0.7            | ns    |

| TBIT   | Transmitter Bit Width                                                   |                      |                | 1/7 TCIP      |                | ns    |

| TPPOS  | Transmitter Pulse Positions - Normalized                                | f = 33 to 70<br>MHz  | -250           | 0             | +250           | ps    |

|        |                                                                         | f = 70 to 112<br>MHz | -200           | 0             | +200           | ps    |

| TJCC   | Transmitter Jitter - Cycle-to-Cycle ( <sup>(1)</sup>                    |                      |                | 50            | 100            | ps    |

| TCCS   | TxOUT Channel to Channel Skew                                           |                      |                | 40            |                | ps    |

| TSTC   | TxIN Setup to TxCLK IN, (Figure 5)                                      |                      | 2.5            |               |                | ns    |

| THTC   | TxIN Hold to TxCLK IN, (Figure 5)                                       |                      | 0              |               |                | ns    |

| TPDL   | Transmitter Propagation Delay - Latency, (Figure 7)                     |                      | 1.5(TCIP)+3.72 | 1.5(TCIP)+4.4 | 1.5(TCIP)+6.24 | ns    |

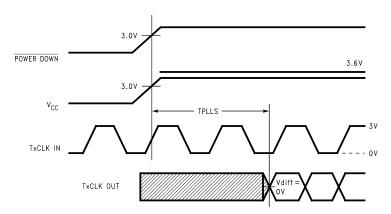

| TPLLS  | Transmitter Phase Lock Loop Set, (Figure S                              | 9)                   |                |               | 10             | ms    |

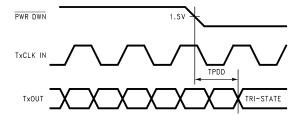

| TPDD   | Transmitter Powerdown Delay, (Figure 11)                                |                      |                |               | 100            | ns    |

(1) TJCC is a function of input clock quality and also PLLVCC noise. At 112MHz operation, with a +/-300ps input impulse at a 2us rate, TJCC has been measured to be in the 70-80ps range (<100ps). With a nominal input clock quality (no input impulse jitter, jitter < 500kHz), TJCC is typically 50ps or less. For RSKM/RSKMD calculations 100ps is typically used as the TJCC budget. See Clock Jitter discussion in the APPLICATIONS INFORMATION section of this datasheet for further information.</p>

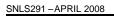

# **Receiver Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                                                                                                                             |             | Min   | Тур | Max  | Units |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-----|------|-------|

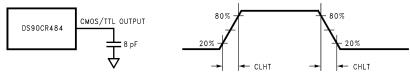

| CLHT   | CMOS/TTL Low-to-High Transition Time, (Figure 3), Rx<br>data out<br>CMOS/TTL Low-to-High Transition Time, (Figure 3), Rx<br>clock out |             |       |     | 2.0  | ns    |

|        |                                                                                                                                       |             |       |     | 1.0  | ns    |

| CHLT   | CMOS/TTL High-to-Low Transition Time, (Figure 3), Rx<br>data out<br>CMOS/TTL High-to-Low Transition Time, (Figure 3), Rx<br>clock out |             |       |     | 2.0  | ns    |

|        |                                                                                                                                       |             |       |     | 1.0  | ns    |

| RCOP   | RxCLK OUT Period, (Figure 6)                                                                                                          |             | 8.928 | Т   | 30.3 | ns    |

| RCOH   | RxCLK OUT High Time, (Figure 6), <sup>(1)</sup>                                                                                       | f = 112 MHz | 3.5   |     |      | ns    |

|        |                                                                                                                                       | f = 66 MHz  | 6.0   |     |      | ns    |

| RCOL   | RxCLK OUT Low Time, (Figure 6), <sup>(1)</sup>                                                                                        | f = 112 MHz | 3.5   |     |      | ns    |

|        |                                                                                                                                       | f = 66 MHz  | 6.0   |     |      | ns    |

(1) The Minimum and Maximum Limits are based on statistical analysis of the device performance over voltage and temperature ranges. This parameter is functionally tested on Automatic Test Equipment (ATE). ATE is limited to 85MHz. A sample of characterization parts have been bench tested to verify functional performance.

Copyright © 2008, Texas Instruments Incorporated

SNLS291 - APRIL 2008

# **Receiver Switching Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol                     | Parameter                                            |               | Min         | Тур         | Max         | Units |

|----------------------------|------------------------------------------------------|---------------|-------------|-------------|-------------|-------|

| RSRC                       | RxOUT Setup to RxCLK OUT, (Figure 6), <sup>(1)</sup> | f = 112 MHz   | 2.4         |             |             | ns    |

|                            | (Figure 6), <sup>(1)</sup>                           | f = 66 MHz    | 3.6         |             |             | ns    |

| RHRC                       |                                                      | f = 112 MHz   | 3.4         |             |             | ns    |

| (Figure 6), <sup>(1)</sup> | f = 66 MHz                                           | 7.0           |             |             | ns          |       |

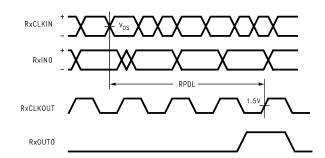

| RPDL                       | Receiver Propagation Delay - Latence                 | y, (Figure 8) | 3(TCIP)+4.0 | 3(TCIP)+4.8 | 3(TCIP)+6.5 | ns    |

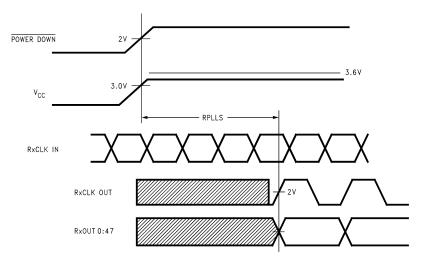

| RPLLS                      | Receiver Phase Lock Loop Set, (Figure 10)            |               |             |             | 10          | ms    |

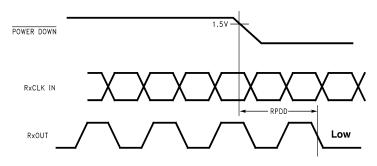

| RPDD                       | Receiver Powerdown Delay, (Figure 12)                |               |             |             | 1           | μs    |

# **Chipset RSKM Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.<sup>(1)</sup> <sup>(2)</sup>. See APPLICATIONS INFORMATION section for more details on this parameter and how to apply it.

| Symbol | Parameter                                                                       |                  | Min      | Тур     | Max | Units |

|--------|---------------------------------------------------------------------------------|------------------|----------|---------|-----|-------|

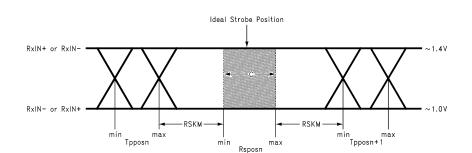

| RSKM   | Receiver Skew Margin without Deskew                                             | f = 112 MHz      | 170      |         |     | ps    |

|        | in non-DC Balance Mode, (Figure 13), See <sup>(3)</sup>                         | f = 100 MHz      | 170      | 240     |     | ps    |

|        |                                                                                 | f = 85MHz        | 300      | 350     |     | ps    |

|        |                                                                                 | f = 66MHz        | 300      | 350     |     | ps    |

| RSKM   | SKM Receiver Skew Margin without Deskew<br>in DC Balance Mode, (Figure 13), See | f = 112 MHz      | 170      |         |     | ps    |

|        |                                                                                 | f = 100 MHz      | 170      | 200     |     | ps    |

|        |                                                                                 | f = 85 MHz       | 250      | 300     |     | ps    |

|        |                                                                                 | f = 66 MHz       | 250      | 300     |     | ps    |

|        |                                                                                 | f = 50MHz        | 300      | 350     |     | ps    |

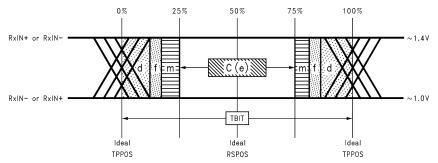

| RSKMD  | Receiver Skew Margin with Deskew in DC Balance, (Figure 14), See <sup>(4)</sup> | f = 33 to 80 MHz | 0.25TBIT |         |     | ps    |

| RDR    | Receiver Deskew Range                                                           | f = 80 MHz       | ±1       |         |     | TBIT  |

| RDSS   | Receiver Deskew Step Size                                                       | f = 80 MHz       |          | 0.3TBIT |     | ns    |

(1) The Minimum and Maximum Limits are based on statistical analysis of the device performance over voltage and temperature ranges. This parameter is functionally tested on Automatic Test Equipment (ATE). ATE is limited to 85MHz. A sample of characterization parts have been bench tested to verify functional performance.

(2) Typical values for RSKM and RSKMD are applicable for fixed  $V_{CC}$  and T A for the Transmitter and Receiver (both are assumed to be at the same  $V_{CC}$  and T A points).

(3) Receiver Skew Margin (RSKM) is defined as the valid data sampling region at the receiver inputs. This margin takes into account transmitter output pulse positions (min and max) and the receiver input setup and hold time (internal data sampling window - RSPOS). This margin allows for LVDS interconnect skew, inter-symbol interference (both dependent on type/length of cable) and clock jitter.RSKM ≥ cable skew (type, length) + source clock jitter (cycle to cycle, TJCC) + ISI (if any). See APPLICATIONS INFORMATION section for more details.

(4) Receiver Skew Margin with Deskew (RSKMD) is defined as the valid data sampling region at the receiver inputs. The DESKEW function will constrain the receiver's sampling strobes to the middle half of the LVDS bit and removes (adjusts for) fixed interconnect skew. This margin (RSKMD) allows for inter-symbol interference (dependent on type/length of cable), Transmitter Pulse Position (TPPOS) variance, and LVDS clock jitter (TJCC).RSKMD ≥ ISI + TPPOS(variance) + source clock jitter (cycle to cycle). See APPLICATIONS INFORMATION section for more details.

6

www.ti.com

AS

STRUMENTS

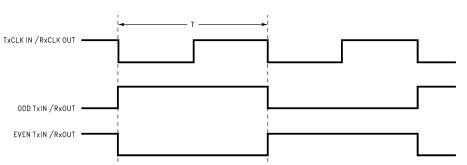

**AC Timing Diagrams**

The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and CMOS/TTL I/O.

Figure 1. "Worst Case" Test Pattern

Figure 2. DS90CR483A (Transmitter) LVDS Output Load and Transition Times

Figure 3. DS90CR484A (Receiver) CMOS/TTL Output Load and Transition Times

Figure 4. DS90CR483A (Transmitter) Input Clock Transition Time

Figure 5. DS90CR483A (Transmitter) Setup/Hold and High/Low Times

Figure 7. DS90CR483A (Transmitter) Propagation Delay - Latency

Figure 8. DS90CR484A (Receiver) Propagation Delay - Latency

Figure 9. DS90CR483A (Transmitter) Phase Lock Loop Set Time

8

XAS

**ISTRUMENTS**

Figure 10. DS90CR484A (Receiver) Phase Lock Loop Set Time

Figure 11. DS90CR483A (Transmitter) Power Down Delay

Figure 12. DS90CR484A (Receiver) Power Down Delay

SNLS291 - APRIL 2008

C — Setup and Hold Time (Internal data sampling window) defined by Rspos (receiver input strobe position) min and max

TPPOS — Transmitter output pulse position (min and max)

RSKM ≥ Cable Skew (type, length) + LVDS Source Clock Jitter (cycle to cycle) + ISI (Inter-symbol interference)

- Cable Skew typically 10 ps to 40 ps per foot, media dependent

- TJCC Cycle-to-cycle LVDS Output jitter (TJCC) is less than 100 ps (worse case estimate).

- ISI is dependent on interconnect length; may be zero

- See APPLICATIONS INFORMATION section for more details.

#### Figure 13. Receiver Skew Margin (RSKM) without DESKEW

C — Setup and Hold Time (Internal data sampling window) defined by Rspos (receiver input strobe position) min and max RSKMD  $\geq$  TPPOSvariance (d) + TJCC (output jitter)(f) + ISI (m)

- d = Tppos Transmitter output pulse position (min and max)

- f = TJCC Cycle-to-cycle LVDS Output jitter (TJCC) is less than 100 ps (worse case estimate).

- m = extra margin assigned to ISI in long cable applications

- See APPLICATIONS INFORMATION section for more details.

#### Figure 14. Receiver Skew Margin (RSKMD) with DESKEW

## **LVDS** Interface

www.ti.com

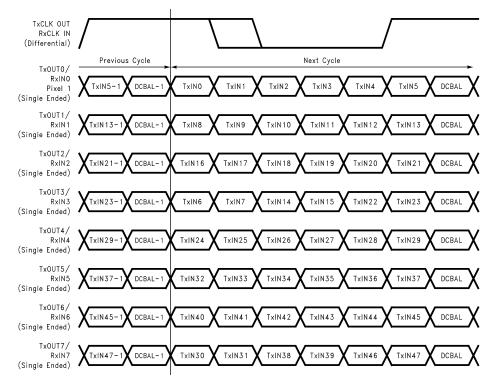

Figure 15. 48 Parallel TTL Data Bits Mapped to LVDS Outputs with DC Balance Enabled

Optional features supported: Pre-emphasis, and Deskew

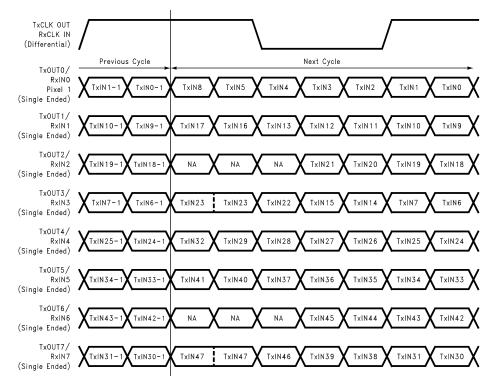

Figure 16. 48 Parallel TTL Data Bits Mapped to LVDS Outputs with DC Balance Disabled

Optional feature supported: Pre-emphasis

### **APPLICATIONS INFORMATION**

The DS90CR483A and DS90CR484A are upgrades to the DS90CR483 and DS90CR484. The DS90CR483A/DS90CR484A no longer have a PLL auto gear option selectable via the PLLSEL pin. The PLLSEL pin now allows for the PLL low gear only or high gear only to be selected. The DS90CR483A/DS90CR484A are fully compatible with older generation Channel Link devices. It should be noted that whenever devices with the auto gear feature are used, an unintentional gear shift caused by fluctuations in  $V_{CC}$  may cause bit errors. By removing the auto gear feature in the DS90CR483A/DS90CR484A, the potential for any gear shift related bit errors has been eliminated.

The DS90CR483A/DS90CR484A chipset is improved over prior generations of Channel Link devices and offers higher bandwidth support and longer cable drive with three areas of enhancement. To increase bandwidth, the maximum clock rate is increased to 112 MHz and 8 serialized LVDS outputs are provided. Cable drive is enhanced with a user selectable pre-emphasis feature that provides additional output current during transitions to counteract cable loading effects. This requires the use of one pull up resistor to Vcc; please refer to Table 1 to set the level needed. Optional DC balancing on a cycle-to-cycle basis, is also provided to reduce ISI (Inter-Symbol Interference). With pre-emphasis and DC balancing, a low distortion eye-pattern is provided at the receiver end of the cable. A cable deskew capability has been added to deskew long cables of pair-to-pair skew of up to  $\pm 1$  LVDS data bit time (up to 80 MHz clock rates). For details on deskew, refer to "Deskew" section below. These three enhancements allow cables 5+ meters in length to be driven depending upon media and clock rate.

The DS90CR483A/DS90CR484A chipset may also be used in a non-DC Balance mode. In this mode preemphasis is supported. In this mode, the chipset is also compatible with 21 and 28-bit Channel Link Receivers. See LVDS Interface for the LVDS mapping.

### NEW FEATURES DESCRIPTION

#### 1. Pre-emphasis

Pre-emphasis adds extra current during LVDS logic transition to reduce the cable loading effects. Pre-emphasis strength is set via a DC voltage level applied from min to max (0.75V to Vcc) at the "PRE" pin. A higher input voltage on the "PRE" pin increases the magnitude of dynamic current during data transition. The "PRE" pin requires one pull-up resistor (Rpre) to Vcc in order to set the DC level. There is an internal resistor network, which cause a voltage drop. Please refer to the tables below to set the voltage level.

The waveshape at the Receiver input should not exhibit over or undershoot with the proper amount of preemphasis set. Too much pre-emphasis generates excess noise and increases power dissipation. Cables less than 2 meters in length typically do not require pre-emphasis.

| Rpre      | Resulting PRE Voltage | Effect            |

|-----------|-----------------------|-------------------|

| 1MΩ or NC | 0.75V                 | Standard LVDS     |

| 50kΩ      | 1.0V                  |                   |

| 9kΩ       | 1.5V                  | 50% pre-emphasis  |

| 3kΩ       | 2.0V                  |                   |

| 1kΩ       | 2.6V                  |                   |

| 100Ω      | Vcc                   | 100% pre-emphasis |

#### Table 1. Pre-emphasis DC voltage level with (Rpre)

#### Table 2. Pre-emphasis needed per cable length<sup>(1)</sup>

| Frequency | PRE Voltage | Typical cable length |

|-----------|-------------|----------------------|

| 112MHz    | 1.0V        | 2 meters             |

| 112MHz    | 1.5V        | 5 meters             |

| 80MHz     | 1.0V        | 2 meters             |

(1) This is based on testing with standard shield twisted pair cable. The amount of pre-emphasis will vary depending on the type of cable, length and operating frequency.

www.ti.com

www.ti.com

| Table 2. Pre-emphasis needed per cable length <sup>(1)</sup> (continued) |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

| Frequency | PRE Voltage | Typical cable length |

|-----------|-------------|----------------------|

| 80MHz     | 1.2V        | 5+ meters            |

| 66MHz     | 1.5V        | 7 meters             |

#### 2. DC Balance

In addition to data information an additional bit is transmitted on every LVDS data signal line during each cycle as shown in LVDS Interface. This bit is the DC balance bit (DCBAL). The purpose of the DC Balance bit is to minimize the short- and long-term DC bias on the signal lines. This is achieved by selectively sending the data either unmodified or inverted.

The value of the DC balance bit is calculated from the running word disparity and the data disparity of the current word to be sent. The data disparity of the current word shall be calculated by subtracting the number of bits of value 0 from the number of bits value 1 in the current word. Initially, the running word disparity may be any value between +7 and -6. The running word disparity shall be calculated as a continuous sum of all the modified data disparity values, where the unmodified data disparity value is the calculated data disparity minus 1 if the data is sent unmodified and 1 plus the inverse of the calculated data disparity if the data is sent inverted. The value of the running word disparity shall saturate at +7 and -6.

The value of the DC balance bit (DCBAL) shall be 0 when the data is sent unmodified and 1 when the data is sent inverted. To determine whether to send data unmodified or inverted, the running word disparity and the current data disparity are used. If the running word disparity is positive and the current data disparity is positive, the data shall be sent inverted. If the running word disparity is positive and the current data disparity is zero or negative, the data shall be sent unmodified. If the running word disparity is negative and the current data disparity is positive, the data shall be sent unmodified. If the running word disparity is negative and the current data disparity is zero or negative, the data shall be sent unmodified. If the running word disparity is negative and the current data disparity is zero or negative, the data shall be sent unmodified. If the running word disparity is negative and the current data disparity is zero or negative, the data shall be sent unmodified. If the running word disparity is negative and the current data disparity is zero or negative, the data shall be sent unmodified. If the running word disparity is negative and the current data disparity is zero or negative, the data shall be sent inverted. If the running word disparity is zero, the data shall be sent inverted.

DC Balance mode is set when the BAL pin on the transmitter is tied HIGH - See the and Tables. DC Balancing is useful on long cable applications which are typically greater than 5 meters in length.

#### 3. Deskew

Deskew is supported in the DC Balance mode only (BAL = high on DS90CR483A). The "DESKEW" pin on the receiver when set high will deskew a minimum of  $\pm 1$  LVDS data bit time skew from the ideal strobe location between signals arriving on independent differential pairs (pair-to-pair skew). It is required that the "DS\_OPT" pin on the Transmitter must be applied low for a minimum of four clock cycles to complete the deskew operation. It is also required that this must be performed at least once at any time after the PLLs have locked to the input clock frequency. If power is lost, or if the cable has been switched, this procedure must be repeated or else the receiver may not sample the incoming LVDS data correctly. When the receiver is in the deskew mode, all receiver data outputs are set to a LOW state, but the receiver clock output is still active and switching. Setting the "DESKEW" pin to low will disable the deskew operation and allow the receiver to operation on a fixed data sampling strobe. In this case, the "DS\_OPT" pin on the transmitter must then be set high.

The DS\_OPT pin at the input of the transmitter (DS90CR483A) is used to initiate the deskew calibration pattern. It must be applied low for a minimum of four clock cycles in order for the receiver to complete the deskew operation. For this reason, the LVDS clock signal with DS\_OPT applied high (active data sampling) shall be 1111000 or 1110000 pattern. During the deskew operation with DS\_OPT applied low, the LVDS clock signal shall be 1111100 or 1100000 pattern. The transmitter will also output a series of 1111000 or 1110000 onto the LVDS data lines (TxOUT 0-7) during deskew so that the receiver can automatically calibrated the data sampling strobes at the receiver inputs. Each data channel is deskewed independently and is tuned with a step size of 1/3 of a bit time over a range of +/-1 TBIT from the ideal strobe location. The Deskew feature operates up to clock rates of 80 MHz only. If the Receiver is enabled in the deskew mode, then it must be trained before data transfer.

www.ti.com

# **CLOCK JITTER**

The transmitter is designed to reject cycle-to-cycle jitter which may be seen at the transmitter input clock. Very low cycle-to-cycle jitter is passed on to the transmitter outputs. Cycle-to-cycle jitter has been measured over frequency to be less than 100 ps with input step function jitter applied. This should be subtracted from the RSKM/RSKMD budget as shown and described inRSKM - RECEIVER SKEW MARGIN and RSKMD - RECEIVER SKEW MARGIN WITH DESKEW. This rejection capability significantly reduces the impact of jitter at the TXinput clock pin, and improves the accuracy of data sampling in the receiver. Transmitter output jitter is effected by PLLVCC noise and input clock jitter - minimize supply noise and use a low jitter clock source to limit output jitter. The falling edge of the input clock to the transmitter is the critical edge and is used by the PLL circuit.

## **RSKM - RECEIVER SKEW MARGIN**

RSKM is a chipset parameter and is explained in AN-1059 in detail. It is the difference between the transmitter's pulse position and the receiver's strobe window. RSKM must be greater than the summation of: Interconnect skew, LVDS Source Clock Jitter (TJCC), and ISI (if any). Interconnect skew includes PCB traces differences, connector skew and cable skew for a cable application. PCB trace and connector skew can be compensated for in the design of the system. Cable skew is media type and length dependant.

## **RSKMD - RECEIVER SKEW MARGIN WITH DESKEW**

RSKMD is a chipset parameter and is applicable when the DESKEW feature of the DS90CR484A is employed. It is the difference between the receiver's strobe window and the ideal pulse locations. The DESKEW feature adjusts for skew between each data channel and the clock channel. This feature is supported up to 80 MHz clock rate. RSKMD must be greater than the summation of: Transmitter's Pulse Position variance, LVDS Source Clock Jitter (TJCC), and ISI (if any). With Deskew, RSKMD is  $\geq 25\%$  of TBIT. Deskew compensates for interconnect skew which includes PCB traces differences, connector skew and cable skew (for a cable application). PCB trace and connector skew can be compensated for in the design of the system. Note, cable skew is media type and length dependant. Cable length may be limited by the RSKMD parameter prior to the interconnect skew reaching 1 TBIT in length due to ISI effects.

## POWER DOWN

Both transmitter and receiver provide a power down feature. When asserted current draw through the supply pins is minimized and the PLLs are shut down. The transmitter outputs are in TRI-STATE when in power down mode. The receiver outputs are forced to a active LOW state when in the power down mode. (See the and Tables). The PD pin should be driven HIGH to enable the device once  $V_{CC}$  is stable.

### CONFIGURATIONS

The transmitter is designed to be connected typically to a single receiver load. This is known as a point-to-point configuration. It is also possible to drive multiple receiver loads if certain restrictions are made. Only the final receiver at the end of the interconnect should provide termination across the pair. In this case, the driver still sees the intended DC load of 100 Ohms. Receivers connected to the cable between the transmitter and the final receiver must not load down the signal. To meet this system requirement, stub lengths from the line to the receiver inputs must be kept very short.

### CABLE TERMINATION

A termination resistor is required for proper operation to be obtained. The termination resistor should be equal to the differential impedance of the media being driven. This should be in the range of 90 to 132 Ohms. 100 Ohms is a typical value common used with standard 100 Ohm twisted pair cables. This resistor is required for control of reflections and also to complete the current loop. It should be placed as close to the receiver inputs to minimize the stub length from the resistor to the receiver input pins.

www.ti.com

#### HOW TO CONFIGURE FOR BACKPLANE APPLICATIONS

In a backplane application with differential line impedance of  $100\Omega$  the differential line pair-to-pair skew can controlled by trace layout. The transmitter-DS90CR483A "DS\_OPT" pin may be set high. In a backplane application with short PCB distance traces, pre-emphasis from the transmitter is typically not required. The "PRE" pin should be left open (do not tie to ground). A resistor pad provision for a pull up resistor to Vcc can be implemented in case pre-emphasis is needed to counteract heavy capacitive loading effects.

## HOW TO CONFIGURE FOR CABLE INTERCONNECT APPLICATIONS

In applications that require the long cable drive capability. The DS90CR483A/DS90CR484A chipset is improved over prior generations of Channel Link devices and offers higher bandwidth support and longer cable drive with the use of DC balanced data transmission, pre-emphasis. Cable drive is enhanced with a user selectable pre-emphasis feature that provides additional output current during transitions to counteract cable loading effects. This requires the use of one pull up resistor to Vcc; please refer to Electrical Characteristics<sup>(2)</sup>to set the level needed. Optional DC balancing on a cycle-to-cycle basis, is also provided to reduce ISI (Inter-Symbol Interference) for long cable applications. With pre-emphasis and DC balancing, a low distortion eye-pattern is provided at the receiver end of the cable. These enhancements allow cables 5+ meters in length to be driven. Depending upon clock rate and the media being driven, the cable Deskew feature may also be employed - see discussion on DESKEW, RSKM and RSKMD above.

### SUPPLY BYPASS RECOMMENDATIONS

Bypass capacitors must be used on the power supply pins. Different pins supply different portions of the circuit, therefore capacitors should be nearby all power supply pins except as noted in the pin description table. Use high frequency ceramic (surface mount recommended)  $0.1\mu$ F capacitors close to each supply pin. If space allows, a  $0.01\mu$ F capacitor should be used in parallel, with the smallest value closest to the device pin. Additional scattered capacitors over the printed circuit board will improve decoupling. Multiple (large) via should be used to connect the decoupling capacitors to the power plane. A 4.7 to  $10 \mu$ F bulk cap is recommended near the PLLVCC pins and also the LVDSVCC (pin #40) on the Transmitter. Connections between the caps and the pin should use wide traces.

## **INPUT SIGNAL QUALITY REQUIREMENTS - TRANSMITTER**

The input signal quality must comply to the datasheet requirements, please refer to the "Recommended Transmitter Input Characteristics" table for specifications. In addition undershoots in excess of the ABS MAX specifications are not recommended. If the line between the host device and the transmitter is long and acts as a transmission line, then termination should be employed. If the transmitter is being driven from a device with programmable drive strengths, data inputs are recommended to be set to a weak setting to prevent transmission line effects. The clock signal is typically set higher to provide a clean edge that is also low jitter.

### UNUSED LVDS OUTPUTS

Unused LVDS output channels should be terminated with 100 Ohm at the transmitter's output pin.

### **RECEIVER OUTPUT DRIVE STRENGTH**

The DS90CR484A output specify a 8pF load,  $V_{OH}$  and  $V_{OL}$  are tested at ± 2mA, which is intended for only 1 or maybe 2 loads. If high fan-out is required or long transmission line driving capability, buffering the receiver output is recommended. Receiver outputs do not support / provide a TRI-STATE function.

## LVDS INTERCONNECT GUIDELINES

See AN-1108 and AN-905 for full details.

- Use 100Ω coupled differential pairs

- Use the S/2S/3S rule in spacings

- S = space between the pair

- 2S = space between pairs

- 3S = space to TTL signal

- (2) Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except V<sub>TH</sub>, V<sub>TL</sub>, V<sub>OD</sub> and  $\Delta$ V<sub>OD</sub>).

www.ti.com

- Minimize the number of VIA

- Use differential connectors when operating above 500Mbps line speed

- Maintain balance of the traces

- · Minimize skew within the pair

- Minimize skew between pairs

- Terminate as close to the RXinputs as possible

#### FOR MORE INFORMATION

Channel Link Applications Notes currently available:

- AN-1041 Introduction to Channel Link

- AN-1059 RSKM Calculations

- AN-1108 PCB and Interconnect Guidelines

- AN-905 Differential Impedance

- National's LVDS Owner's Manual

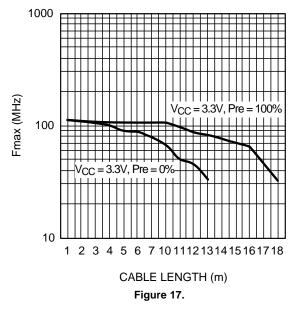

# Typical Data Rate vs Cable Length Curve

DATA RATE VS CABLE LENGTH TEST PROCEDURE

The Data Rate vs Cable Length graph was generated using National Semiconductor's CLINK3V48BT-112 Evaluation Kit and 3M's Mini D Ribbon (MDR) Cable under typical conditions (Vcc = 3.3V, Temp =  $+25^{\circ}$ C). A Tektronix MB100 Bit-Error-Rate Tester (BERT) was used to send a PRBS ( $2^{15}$ ) pattern to 32 of the 48 input channels on the transmitter (DS90CR483A). The BERT was also used to monitor the corresponding 32 receiver (DS90CR484A) output channels for bit errors. The frequency of the input signal were increased until bit errors were reported on the BERT. The frequency on the graph is the highest frequency without error.

#### **Results:**

The DS90CR483A/DS90CR484A link was error free at 100MHz over 10 meters of 3M cable using pre-emphasis and DC balance mode off.

| I/O | Description                             |

|-----|-----------------------------------------|

| Ι   | TTL level input. <sup>(1)</sup> .       |

| 0   | Positive LVDS differential data output. |

|     | I                                       |

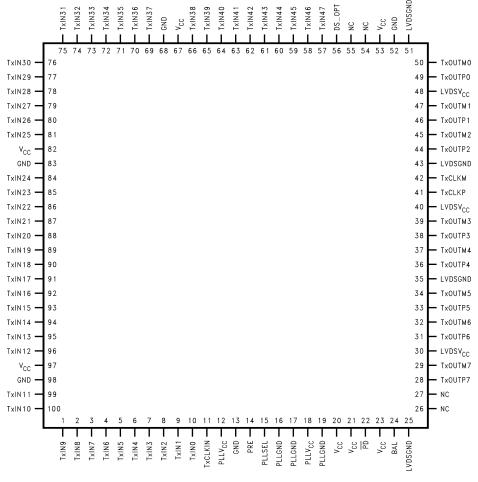

## DS90CR483A Pin Descriptions—Channel Link Transmitter

(1) Inputs default to "low" when left open due to internal pull-down resistor.

SNLS291 - APRIL 2008

| Pin Name            | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТхОИТМ              | 0   | Negative LVDS differential data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TxCLKIN             | 1   | TTL level clock input. The rising edge acts as data strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TxCLKP              | 0   | Positive LVDS differential clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TxCLKM              | 0   | Negative LVDS differential clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PD                  | 1   | TTL level input. Assertion (low input) tri-states the outputs, ensuring low current at power down.                                                                                                                                                                                                                                                                                                                                                                                         |

| PLLSEL              | I   | PLL range select. This pin should be tied to $V_{CC}$ for high-range. Tied to ground or NC will force the PLL to low range. Low range is 33 — 40 MHz. High range is 38 — 112 MHz. <sup>(1)</sup>                                                                                                                                                                                                                                                                                           |

| PRE                 | I   | Pre-emphasis "level" select. Pre-emphasis is active when input is tied to V <sub>CC</sub> through external pull-<br>up resistor. Resistor value determines Pre-emphasis level (See APPLICATIONS INFORMATION<br>Section). For normal LVDS drive level (No Pre-emphasis) leave this pin open (do not tie to<br>ground).                                                                                                                                                                      |

| DS_OPT              | I   | Cable Deskew performed when TTL level input is low. No TxIN data is sampled during Deskew.<br>To perform Deskew function, input must be held low for a minimum of 4 clock cycles. The Deskew operation is normally conducted after the TX and RX PLLs have locked. It should also be conducted after a system reset, or a reconfiguration event. It must be performed at least once when "DESKEW" is enabled. <sup>(1)</sup> Deskew is only supported in the DC Balance mode (BAL = High). |

| BAL                 | I   | TTL level input. This pin was previously labeled as $V_{CC}$ , which enabled the DC Balance function.<br>But when tied low or left open, the DC Balance function is disabled. Please refer to (Figure 15 Figure 16) for LVDS data bit mapping respectively. <sup>(2)</sup> , <sup>(3)</sup>                                                                                                                                                                                                |

| V <sub>CC</sub>     | I   | Power supply pins for TTL inputs and digital circuitry. Bypass not required on Pins 20 and 21.                                                                                                                                                                                                                                                                                                                                                                                             |

| GND                 | I   | Ground pins for TTL inputs and digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PLLV <sub>CC</sub>  | I   | Power supply pin for PLL circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PLLGND              | I   | Ground pins for PLL circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LVDSV <sub>CC</sub> | I   | Power supply pin for LVDS outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LVDSGND             | I   | Ground pins for LVDS outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NC                  |     | No Connect. Make NO Connection to these pins - leave open.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### DS90CR483A Pin Descriptions—Channel Link Transmitter (continued)

(2) Inputs default to "low" when left open due to internal pull-down resistor.

(3) The DS90CR484A is design to automatically detect the DC Balance or non-DC Balance transmitted data from the DS90CR483A and deserialize the LVDS data according to the define bit mapping.

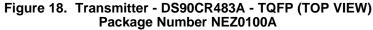

#### DS90CR484A Pin Descriptions—Channel Link Receiver<sup>(1)</sup>

| Pin Name           | I/O | Description                                                                                                                                                                                                                            |

|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxINP              | I   | Positive LVDS differential data inputs.                                                                                                                                                                                                |

| RxINM              | I   | Negative LVDS differential data inputs.                                                                                                                                                                                                |

| RxOUT              | 0   | TTL level data outputs. In PowerDown ( $\overline{PD}$ = Low) mode, receiver outputs are forced to a Low state.                                                                                                                        |

| RxCLKP             | I   | Positive LVDS differential clock input.                                                                                                                                                                                                |

| RxCLKM             | I   | Negative LVDS differential clock input.                                                                                                                                                                                                |

| RxCLKOUT           | 0   | TTL level clock output. The rising edge acts as data strobe.                                                                                                                                                                           |

| PLLSEL             | I   | PLL range select. This pin should be tied to V <sub>CC</sub> for high-range. Tied to ground or NC will force the PLL to low range only. Low range is 33 – 40 MHz. High range is 38 – 112 MHz. <sup>(2)</sup>                           |

| DESKEW             | I   | Deskew / Oversampling "on/off" select. When using the Deskew / Oversample feature this pin must be tied to $V_{CC}$ . Tieing this pin to ground disables this feature. <sup>(2)</sup> Deskew is only supported in the DC Balance mode. |

| PD                 | I   | TTL level input. When asserted (low input) the receiver outputs are Low. (2)                                                                                                                                                           |

| V <sub>CC</sub>    | I   | Power supply pins for TTL outputs and digital circuitry. Bypass not required on Pins 6 and 77.                                                                                                                                         |

| GND                | I   | Ground pins for TTL outputs and digital circuitry.                                                                                                                                                                                     |

| PLLV <sub>CC</sub> | I   | Power supply for PLL circuitry.                                                                                                                                                                                                        |

| PLLGND             | 1   | Ground pin for PLL circuitry.                                                                                                                                                                                                          |

(1) These receivers have input fail-safe bias circuitry to guarantee a stable receiver output for floating or terminated receiver inputs. Under test conditions receiver inputs will be in a HIGH state. If the cable interconnect (media) are disconnected which results in floating/terminated inputs, the outputs will remain in the last valid state.

(2) Inputs default to "low" when left open due to internal pull-down resistor.

Copyright © 2008, Texas Instruments Incorporated

TEXAS INSTRUMENTS

www.ti.com

## DS90CR484A Pin Descriptions—Channel Link Receiver<sup>(1)</sup> (continued)

| Pin Name            | I/O | Description                                                |

|---------------------|-----|------------------------------------------------------------|

| LVDSV <sub>CC</sub> | I   | Power supply pin for LVDS inputs.                          |

| LVDSGND             | I   | Ground pins for LVDS inputs.                               |

| NC                  |     | No Connect. Make NO Connection to these pins - leave open. |

## **Pin Diagram**

## Pin Diagram

Package Number NEZ0100A

SNLS291 - APRIL 2008

24-Jan-2013

# PACKAGING INFORMATION

| Orderable Device    | Status | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan                   | Lead/Ball Finish |                     | Op Temp (°C) |                     | Samples |

|---------------------|--------|--------------|--------------------|------|-------------|----------------------------|------------------|---------------------|--------------|---------------------|---------|

|                     | (1)    |              | Diawing            |      |             | (2)                        |                  | (3)                 |              | (4)                 |         |

| DS90CR483AVJD/NOPB  | ACTIVE | TQFP         | NEZ                | 100  | 90          | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-3-260C-168 HR | -10 to 70    | DS90CR483AVJD<br>>B | Samples |

| DS90CR483AVJDX/NOPB | ACTIVE | TQFP         | NEZ                | 100  | 1000        | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-3-260C-168 HR |              | DS90CR483AVJD<br>>B | Samples |

| DS90CR484AVJD/NOPB  | ACTIVE | TQFP         | NEZ                | 100  | 90          | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-3-260C-168 HR |              | DS90CR484AVJD<br>>B | Samples |

| DS90CR484AVJDX/NOPB | ACTIVE | TQFP         | NEZ                | 100  | 1000        | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-3-260C-168 HR | -10 to 70    | DS90CR484AVJD<br>>B | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

24-Jan-2013

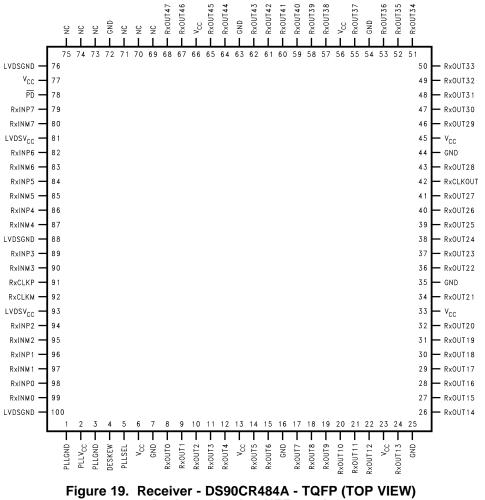

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

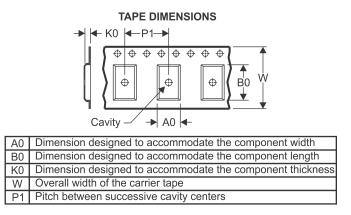

# TAPE AND REEL INFORMATION

\*All dimensions are nominal

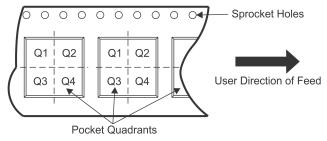

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device                  | Package<br>Type | Package<br>Drawing |     | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | · /  | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------------|-----------------|--------------------|-----|------|--------------------------|--------------------------|------|------------|------------|------------|-----------|------------------|

| DS90CR483AVJDX/NOP<br>B | TQFP            | NEZ                | 100 | 1000 | 330.0                    | 32.4                     | 18.0 | 18.0       | 1.6        | 24.0       | 32.0      | Q2               |

| DS90CR484AVJDX/NOP<br>B | TQFP            | NEZ                | 100 | 1000 | 330.0                    | 32.4                     | 18.0 | 18.0       | 1.6        | 24.0       | 32.0      | Q2               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

26-Mar-2013

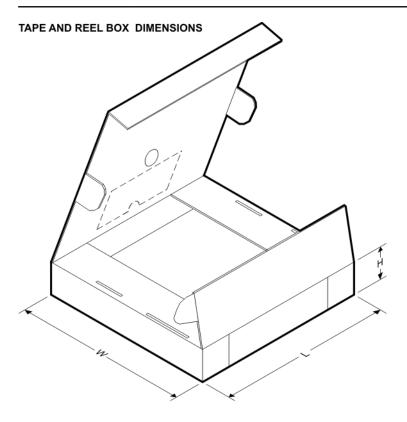

\*All dimensions are nominal

| Device              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS90CR483AVJDX/NOPB | TQFP         | NEZ             | 100  | 1000 | 367.0       | 367.0      | 55.0        |

| DS90CR484AVJDX/NOPB | TQFP         | NEZ             | 100  | 1000 | 367.0       | 367.0      | 55.0        |

# NEZ0100A

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated