# DS90C383,DS90CF384

DS90C383/DS90CF384 +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display (FPD) Link-65 MHz, +3.3V LVDS Receiver 24-Bit Flat Panel Display (FPD) Link-65 MHz

Literature Number: SNLS124

# DS90C383/DS90CF384

# +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display (FPD) Link—65 MHz, +3.3V LVDS Receiver 24-Bit Flat Panel Display (FPD) Link—65 MHz

# **General Description**

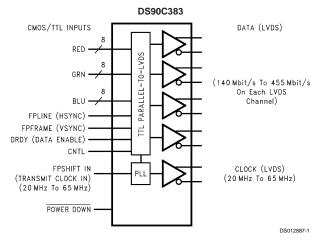

The DS90C383 transmitter converts 28 bits of CMOS/TTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. The DS90CF384 receiver converts the LVDS data streams back into 28 bits of CMOS/TTL data. At a transmit clock frequency of 65 MHz, 24 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 455 Mbps per LVDS data channel. Using a 65 MHz clock, the data throughputs is 227 Mbytes/sec. The transmitter is offered with programmable edge data strobes for convenient interface with a variety of graphics controllers. The transmitter can be programmed for Rising edge strobe or Falling edge strobe through a dedicated pin. A Rising edge transmitter will inter-operate with a Falling edge receiver (DS90CF384) without any translation logic. The DS90CF384 is also offered in 64 ball, 0.8mm fine pitch ball grid array(FBGA) package which provides a 44 % reduction in PCB footprint (available Q3, 1999).

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high speed TTL interfaces.

# **Features**

- 20 to 65 MHz shift clock support

- Programmable transmitter (DS90C383) strobe select (Rising or Falling edge strobe)

- Single 3.3V supply

- Chipset (Tx + Rx) power consumption < 250 mW (typ)

- Power-down mode (< 0.5 mW total)

- Single pixel per clock XGA (1024x768) ready

- Supports VGA, SVGA, XGA and higher addressability.

- Up to 227 Megabytes/sec bandwidth

- Up to 1.8 Gbps throughput

- Narrow bus reduces cable size and cost

- 290 mV swing LVDS devices for low EMI

- PLL requires no external components

- Low profile 56-lead TSSOP package.DS90CF384 also available in 64 ball, 0.8mm fine pitch

- ball grid array(FBGA) package

Falling edge data strobe Receiver

- Compatible with TIA/EIA-644 LVDS standard

- ESD rating >7 kV

- Operating Temperature: -40°C to +85°C

# **Block Diagrams**

# Application DATA (LVDS) HOST GRAPHICS CMOS/ CONTROLLER TIL CLOCK (LVDS) FPSHIFT IN (TxCLK IN) DATA (LVDS) CMOS/ TIL CONTROLLER CNOS/ TIL CNOS/ T

TRI-STATE® is a registered trademark of National Semiconductor Corporation

# **Block Diagrams** (Continued)

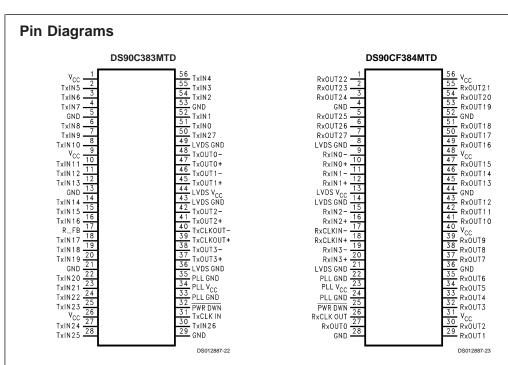

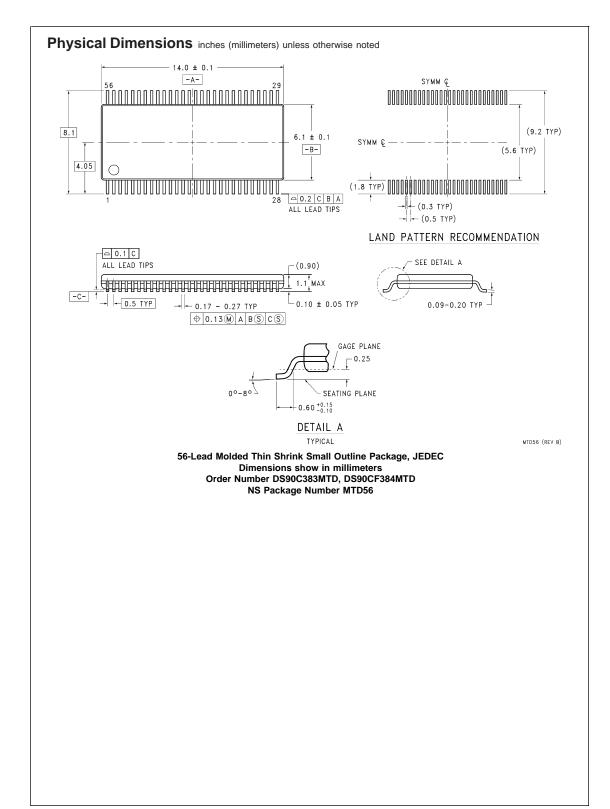

# Order Number DS90C383MTD See NS Package Number MTD56

#

Order Number DS90CF384MTD or DS90CF384SLC See NS Package Number MTD56 or SLC64A

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) -0.3V to +4V–0.3V to ( $V_{\rm CC}$  + 0.3V) CMOS/TTL Input Voltage -0.3V to ( $V_{\rm CC}$  + 0.3V) CMOS/TTL Output Voltage LVDS Receiver Input Voltage -0.3V to  $(V_{CC} + 0.3V)$ -0.3V to  $(V_{CC} + 0.3V)$ LVDS Driver Output Voltage LVDS Output Short Circuit

Continuous Duration Junction Temperature +150°C -65°C to +150°C Storage Temperature Lead Temperature

(Soldering, 4 sec for TSSOP) +260°C Solder Reflow Temperature (20 sec for FBGA) +220°C

Maximum Package Power Dissipation Capacity 25°C

MTD56 (TSSOP) Package: DS90C383MTD

1.63 W DS90CF384MTD 1.61 W

Package Derating:

DS90C383MTD 12.5 mW/°C above +25°C DS90CF384MTD 12.4 mW/°C above +25°C Maximum Package Power Dissipation Capacity 25°C SLC64A Package:

DS90CF384SLC Package Derating:

DS90CF384SLC 10.2 mW/°C above +25°C

2.0 W

ESD Rating (HBM, 1.5 k $\Omega$ , 100 pF) > 7 kV

# **Recommended Operating Conditions**

|                                   | Min | Nom | Max | Units   |

|-----------------------------------|-----|-----|-----|---------|

| Supply Voltage (V <sub>CC</sub> ) | 3.0 | 3.3 | 3.6 | V       |

| Operating Free Air                |     |     |     |         |

| Temperature (T <sub>A</sub> )     | -40 | +25 | +85 | °C      |

| Receiver Input Range              | 0   |     | 2.4 | V       |

| Supply Noise Voltage ( $V_{CC}$ ) |     |     | 100 | $mV_PP$ |

# **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                         | Condition                                       | ons                        | Min  | Тур   | Max             | Units |

|------------------|-----------------------------------|-------------------------------------------------|----------------------------|------|-------|-----------------|-------|

| CMOS/            | TTL DC SPECIFICATIONS             |                                                 |                            | •    | •     | •               |       |

| V <sub>IH</sub>  | High Level Input Voltage          |                                                 |                            | 2.0  |       | V <sub>cc</sub> | V     |

| V <sub>IL</sub>  | Low Level Input Voltage           |                                                 |                            | GND  |       | 0.8             | V     |

| V <sub>OH</sub>  | High Level Output Voltage         | $I_{OH} = -0.4 \text{ mA}$                      | $I_{OH} = -0.4 \text{ mA}$ |      |       |                 | V     |

| V <sub>OL</sub>  | Low Level Output Voltage          | I <sub>OL</sub> = 2 mA                          |                            |      | 0.06  | 0.3             | V     |

| V <sub>CL</sub>  | Input Clamp Voltage               | I <sub>CL</sub> = -18 mA                        |                            |      | -0.79 | -1.5            | V     |

| I <sub>IN</sub>  | Input Current                     | $V_{IN} = V_{CC}$ , GND, 2.5V                   | or 0.4V                    |      | ±5.1  | ±10             | μA    |

| I <sub>os</sub>  | Output Short Circuit Current      | V <sub>OUT</sub> = 0V                           |                            | -60  | -120  | mA              |       |

| LVDS D           | OC SPECIFICATIONS                 |                                                 |                            | •    | •     | •               |       |

| V <sub>OD</sub>  | Differential Output Voltage       | $R_L = 100\Omega$                               | 250                        | 345  | 450   | mV              |       |

| $\Delta V_{OD}$  | Change in V <sub>OD</sub> between |                                                 |                            |      |       | 35              | mV    |

|                  | complimentary output states       |                                                 |                            |      |       |                 |       |

| Vos              | Offset Voltage (Note 4)           |                                                 | 1.125                      | 1.25 | 1.375 | V               |       |

| ΔV <sub>os</sub> | Change in V <sub>OS</sub> between |                                                 |                            |      |       | 35              | mV    |

|                  | complimentary output states       |                                                 |                            |      |       |                 |       |

| Ios              | Output Short Circuit Current      | $V_{OUT} = 0V, R_L = 100\Omega$                 |                            |      | -3.5  | -5              | mA    |

| l <sub>oz</sub>  | Output TRI-STATE® Current         | Power Down = 0V,                                |                            |      | ±1    | ±10             | μA    |

|                  |                                   | $V_{OUT} = 0V \text{ or } V_{CC}$               |                            |      |       |                 |       |

| V <sub>TH</sub>  | Differential Input High Threshold | V <sub>CM</sub> = +1.2V                         |                            |      |       | +100            | mV    |

| V <sub>TL</sub>  | Differential Input Low Threshold  |                                                 |                            | -100 |       |                 | mV    |

| I <sub>IN</sub>  | Input Current                     | $V_{IN} = +2.4V, V_{CC} = 3.6$                  | V                          |      |       | ±10             | μA    |

|                  |                                   | $V_{IN} = 0V, V_{CC} = 3.6V$                    |                            |      |       | ±10             | μA    |

| TRANS            | MITTER SUPPLY CURRENT             |                                                 |                            |      | •     | •               |       |

| ICCTW            | Transmitter Supply Current        | $R_L = 100\Omega$ ,                             | f = 32.5 MHz               |      | 31    | 45              | mA    |

|                  |                                   | $C_L = 5 pF$ ,                                  |                            |      |       |                 |       |

|                  | Worst Case                        | Worst Case Pattern                              | f = 37.5 MHz               |      | 32    | 50              | mA    |

|                  |                                   | (Figures 1, 3), T <sub>A</sub> = -40°C to +85°C | f = 65 MHz                 |      | 42    | 55              | mA    |

# **Electrical Characteristics** (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                  | Condition                                              | ns               | Min | Тур | Max | Units |

|--------|----------------------------|--------------------------------------------------------|------------------|-----|-----|-----|-------|

| TRANSI | MITTER SUPPLY CURRENT      |                                                        |                  |     | •   | •   | •     |

| ICCTG  | Transmitter Supply Current | $R_{L} = 100\Omega,$ $C_{L} = 5 \text{ pF},$           | f = 32.5 MHz     |     | 23  | 35  | mA    |

|        | 16 Grayscale               | 16 Grayscale Pattern                                   | f = 37.5 MHz     |     | 28  | 40  | mA    |

|        |                            | (Figures 2, 3), $T_A = -40^{\circ}C$ to $+85^{\circ}C$ | f = 65 MHz       |     | 31  | 45  | mA    |

| ICCTZ  | Transmitter Supply Current | Power Down = Low                                       | Power Down = Low |     |     | 55  | μΑ    |

|        | Power Down                 | Driver Outputs in TRI-STATE® under                     |                  |     |     |     |       |

|        |                            | Power Down Mode                                        |                  |     |     |     |       |

| RECEIV | ER SUPPLY CURRENT          |                                                        |                  |     |     |     |       |

| ICCRW  | Receiver Supply Current    | C <sub>L</sub> = 8 pF,                                 | f = 32.5 MHz     |     | 49  | 65  | mA    |

|        | Worst Case                 | Worst Case Pattern                                     | f = 37.5 MHz     |     | 53  | 70  | mA    |

|        |                            | (Figures 1, 4), T <sub>A</sub> = -40°C to +85°C        | f = 65 MHz       |     | 78  | 105 | mA    |

| ICCRG  | Receiver Supply Current,   | C <sub>L</sub> = 8 pF,                                 | f = 32.5 MHz     |     | 28  | 45  | mA    |

|        | 16 Grayscale               | 16 Grayscale Pattern                                   | f = 37.5 MHz     |     | 30  | 47  | mA    |

|        |                            | (Figures 2, 4), T <sub>A</sub> = -40°C to +85°C        | f = 65 MHz       |     | 43  | 60  | mA    |

| ICCRZ  | Receiver Supply Current    | Power Down = Low                                       |                  |     | 10  | 55  | μΑ    |

|        | Power Down                 | Receiver Outputs Stay L                                | ow during        |     |     |     |       |

|        |                            | Power Down Mode                                        |                  |     |     |     |       |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except  $V_{\mbox{\scriptsize OD}}$  and  $\Delta V_{\mbox{\scriptsize OD}}).$

Note 4:  $V_{OS}$  previously referred as  $V_{CM}$ .

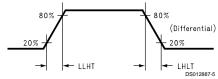

**Transmitter Switching Characteristics**Over recommended operating supply and -40°C to +85°C ranges unless otherwise specified

| Symbol | Parameter                                                           | Min        | Тур   | Max  | Units |    |

|--------|---------------------------------------------------------------------|------------|-------|------|-------|----|

| LLHT   | LVDS Low-to-High Transition Time (Figure 3)                         |            | 0.75  | 1.5  | ns    |    |

| LHLT   | LVDS High-to-Low Transition Time (Figure 3)                         |            |       | 0.75 | 1.5   | ns |

| TCIT   | TxCLK IN Transition Time (Figure 5)                                 |            |       |      | 5     | ns |

| TCCS   | TxOUT Channel-to-Channel Skew (Figure 6)                            |            |       | 250  |       | ps |

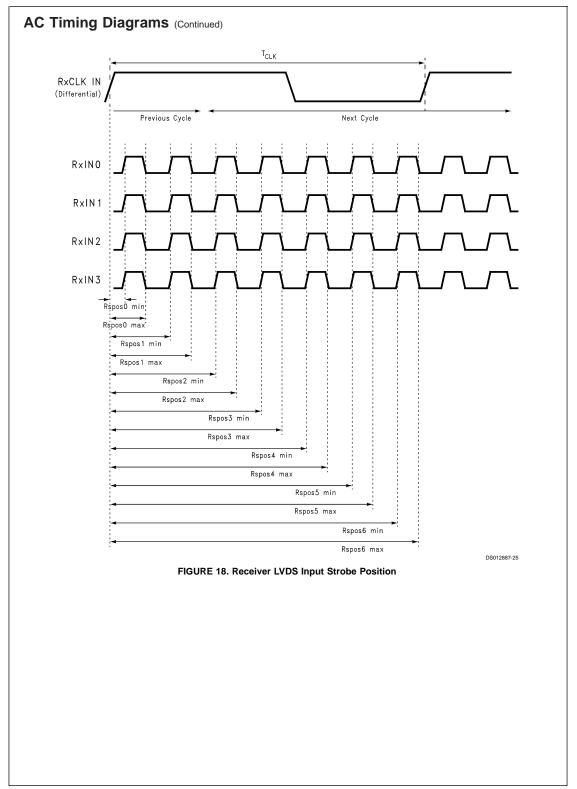

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figure 17)             | f = 65 MHz | -0.4  | 0    | 0.3   | ns |

| TPPos1 | Transmitter Output Pulse Position for Bit 1                         |            | 1.8   | 2.2  | 2.5   | ns |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                         | ]          | 4.0   | 4.4  | 4.7   | ns |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                         |            | 6.2   | 6.6  | 6.9   | ns |

| TPPos4 | Transmitter Output Pulse Position for Bit 4                         | 8.4        | 8.8   | 9.1  | ns    |    |

| TPPos5 | Transmitter Output Pulse Position for Bit 5                         |            |       |      | 11.3  | ns |

| TPPos6 | Transmitter Output Pulse Position for Bit 6                         | ]          | 12.8  | 13.2 | 13.5  | ns |

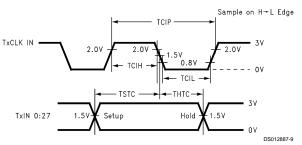

| TCIP   | TxCLK IN Period (Figure 7)                                          |            | 15    | Т    | 50    | ns |

| TCIH   | TxCLK IN High Time (Figure 7)                                       |            | 0.35T | 0.5T | 0.65T | ns |

| TCIL   | TxCLK IN Low Time (Figure 7)                                        |            | 0.35T | 0.5T | 0.65T | ns |

| TSTC   | TxIN Setup to TxCLK IN (Figure 7)                                   | f = 65 MHz | 2.5   |      |       | ns |

| THTC   | TxIN Hold to TxCLK IN (Figure 7)                                    | 0          |       |      | ns    |    |

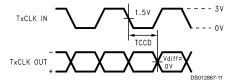

| TCCD   | TxCLK IN to TxCLK OUT Delay 25°C, V <sub>CC</sub> = 3.3V (Figure 9) | 3.0        | 3.7   | 5.5  | ns    |    |

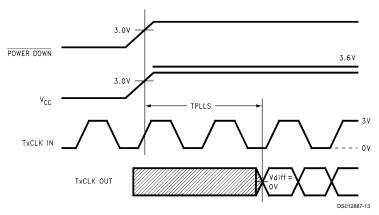

| TPLLS  | Transmitter Phase Lock Loop Set (Figure 11)                         |            |       | 10   | ms    |    |

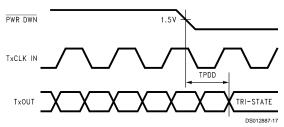

| TPDD   | Transmitter Power Down Delay (Figure 15)                            |            |       |      | 100   | ns |

|        |                                                                     |            |       |      |       |    |

Note 2: Typical values are given for  $V_{CC}$  = 3.3V and  $T_A$  = +25C.

Receiver Switching Characteristics

Over recommended operating supply and -40°C to +85°C ranges unless otherwise specified

| Symbol | Parameter                                                            |            | Min  | Тур  | Max  | Units |

|--------|----------------------------------------------------------------------|------------|------|------|------|-------|

| CLHT   | CMOS/TTL Low-to-High Transition Time (Figure 4)                      |            |      | 2.2  | 5.0  | ns    |

| CHLT   | CMOS/TTL High-to-Low Transition Time (Figure 4)                      |            | 2.2  | 5.0  | ns   |       |

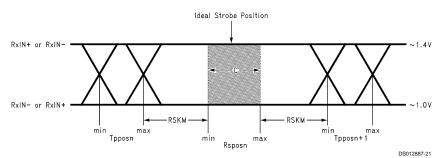

| RSPos0 | Receiver Input Strobe Position for Bit 0 (Figure 18)                 | f = 65 MHz | 0.7  | 1.1  | 1.4  | ns    |

| RSPos1 | Receiver Input Strobe Position for Bit 1                             |            | 2.9  | 3.3  | 3.6  | ns    |

| RSPos2 | Receiver Input Strobe Position for Bit 2                             |            | 5.1  | 5.5  | 5.8  | ns    |

| RSPos3 | Receiver Input Strobe Position for Bit 3                             |            | 7.3  | 7.7  | 8.0  | ns    |

| RSPos4 | Receiver Input Strobe Position for Bit 4                             | 9.5        | 9.9  | 10.2 | ns   |       |

| RSPos5 | Receiver Input Strobe Position for Bit 5                             | 11.7       | 12.1 | 12.4 | ns   |       |

| RSPos6 | Receiver Input Strobe Position for Bit 6                             |            | 13.9 | 14.3 | 14.6 | ns    |

| RSKM   | RxIN Skew Margin (Note 5) (Figure 19)                                | f = 65 MHz | 400  |      |      | ps    |

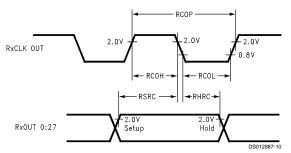

| RCOP   | RxCLK OUT Period (Figure 8)                                          |            | 15   | Т    | 50   | ns    |

| RCOH   | RxCLK OUT High Time (Figure 8)                                       | f = 65 MHz | 7.3  | 8.6  |      | ns    |

| RCOL   | RxCLK OUT Low Time (Figure 8)                                        |            | 3.45 | 4.9  |      | ns    |

| RSRC   | RxOUT Setup to RxCLK OUT (Figure 8)                                  |            | 2.5  | 6.9  |      | ns    |

| RHRC   | RxOUT Hold to RxCLK OUT (Figure 8)                                   |            | 2.5  | 5.7  |      | ns    |

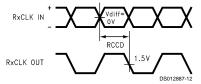

| RCCD   | RxCLK IN to RxCLK OUT Delay 25°C, V <sub>CC</sub> = 3.3V (Figure 10) | 5.0        | 7.1  | 9.0  | ns   |       |

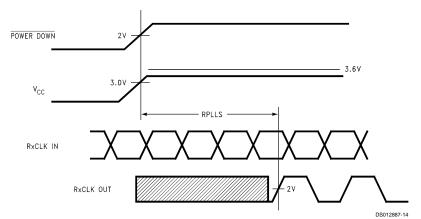

| RPLLS  | Receiver Phase Lock Loop Set (Figure 12)                             |            |      | 10   | ms   |       |

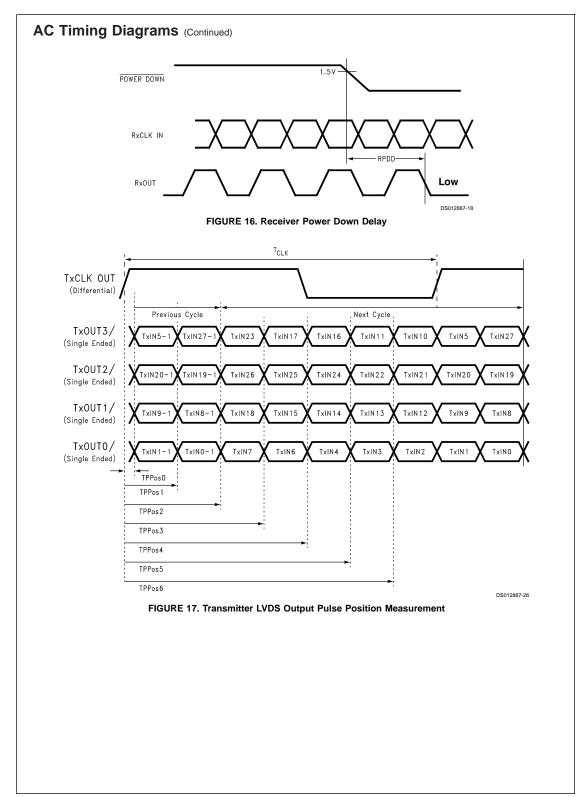

| RPDD   | Receiver Power Down Delay (Figure 16 )                               |            |      | 1    | μs   |       |

|        |                                                                      |            | •    |      |      |       |

Note 5: Receiver Skew Margin is defined as the valid data sampling region at the receiver inputs. This margin takes into account the transmitter pulse positions (min and max) and the receiver input setup and hold time (internal data sampling window-RSPOS). This margin allows for LVDS interconnect skew, inter-symbol interference (both dependent on type/length of cable), and clock jitter (less than 250 ps).

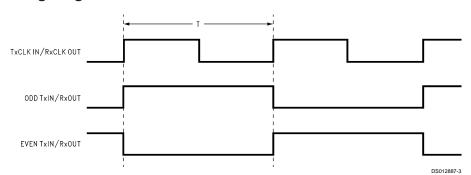

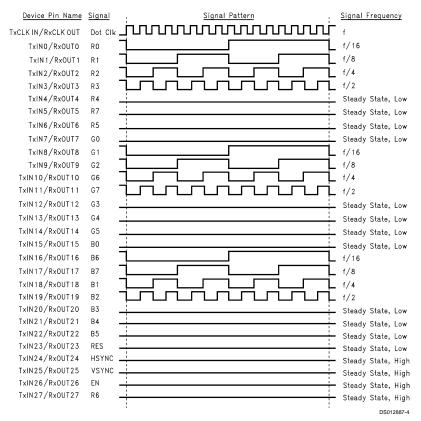

# **AC Timing Diagrams**

FIGURE 1. "Worst Case" Test Pattern

FIGURE 2. "16 Grayscale" Test Pattern (Notes 6, 7, 8, 9)

Note 6: The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and CMOS/TTL I/O.

Note 7: The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

Note 8: Figures 1, 2 show a falling edge data strobe (TxCLK IN/RxCLK OUT).

Note 9: Recommended pin to signal mapping. Customer may choose to define differently.

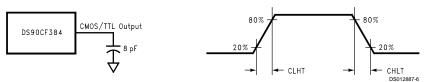

FIGURE 3. DS90C383 (Transmitter) LVDS Output Load and Transition Times

FIGURE 4. DS90CF384 (Receiver) CMOS/TTL Output Load and Transition Times

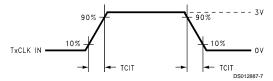

FIGURE 5. DS90C383 (Transmitter) Input Clock Transition Time

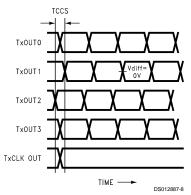

Measurements at  $V_{\rm diff}$  = 0V TCCS measured between earliest and latest LVDS edges. TxCLK Differential Low High Edge

FIGURE 6. DS90C383 (Transmitter) Channel-to-Channel Skew

FIGURE 7. DS90C383 (Transmitter) Setup/Hold and High/Low Times (Falling Edge Strobe)

FIGURE 8. DS90CF384 (Receiver) Setup/Hold and High/Low Times

FIGURE 9. DS90C383 (Transmitter) Clock In to Clock Out Delay (Falling Edge Strobe)

FIGURE 10. DS90CF384 (Receiver) Clock In to Clock Out Delay

FIGURE 11. DS90C383 (Transmitter) Phase Lock Loop Set Time

FIGURE 12. DS90CF384 (Receiver) Phase Lock Loop Set Time

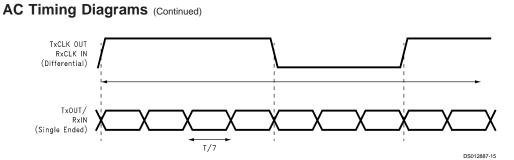

FIGURE 13. Seven Bits of LVDS in Once Clock Cycle

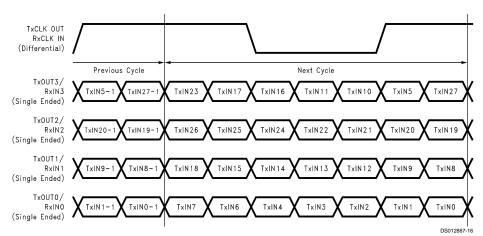

FIGURE 14. 21 Parallel TTL Data Inputs Mapped to LVDS Outputs

FIGURE 15. Transmitter Power Down Delay

C — Setup and Hold Time (Internal data sampling window) defined by Rspos (receiver input strobe position) min and max Tppos — Transmitter output pulse position (min and max)

RSKM = Cable Skew (type, length) + Source Clock Jitter (cycle to cycle) (Note 10) + ISI (Inter-symbol interference) (Note 11)

Cable Skew — typically 10 ps-40 ps per foot, media dependent Note 10: Cycle-to-cycle jitter is less than 250 ps at 65 MHZ

Note 11: ISI is dependent on interconnect length; may be zero

FIGURE 19. Receiver LVDS Input Skew Margin

# DS90C383 Pin Description—FPD Link Transmitter

| Pin Name             | I/O | No. | Description                                                                                                                                           |

|----------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxIN                 | I   | 28  | TTL level input. This includes: 8 Red, 8 Green, 8 Blue, and 4 control lines—FPLINE, FPFRAME and DRDY (also referred to as HSYNC, VSYNC, Data Enable). |

| TxOUT+               | 0   | 4   | Positive LVDS differential data output.                                                                                                               |

| TxOUT-               | 0   | 4   | Negative LVDS differential data output.                                                                                                               |

| FPSHIFT IN           | I   | 1   | TTL level clock input. The falling edge acts as data strobe. Pin name TxCLK IN.                                                                       |

| R_FB                 | ı   | 1   | Programmable strobe select.                                                                                                                           |

| RTxCLK OUT+          | 0   | 1   | Positive LVDS differential clock output.                                                                                                              |

| TxCLK OUT-           | 0   | 1   | Negative LVDS differential clock output.                                                                                                              |

| PWR DOWN             | I   | 1   | TTL level input. When asserted (low input) TRI-STATES the outputs, ensuring low current at power down.                                                |

| V <sub>cc</sub>      | 1   | 3   | Power supply pins for TTL inputs.                                                                                                                     |

| GND                  | I   | 4   | Ground pins for TTL inputs.                                                                                                                           |

| PLL V <sub>CC</sub>  | - 1 | 1   | Power supply pin for PLL.                                                                                                                             |

| PLL GND              | I   | 2   | Ground pins for PLL.                                                                                                                                  |

| LVDS V <sub>CC</sub> | I   | 1   | Power supply pin for LVDS outputs.                                                                                                                    |

| LVDS GND             | I   | 3   | Ground pins for LVDS outputs.                                                                                                                         |

| Pin Name             | I/O | No. | Description                                                                                                                                                 |

|----------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxIN+                | - 1 | 4   | Positive LVDS differential data inputs.                                                                                                                     |

| RxIN-                | 1   | 4   | Negative LVDS differential data inputs.                                                                                                                     |

| RxOUT                | 0   | 28  | TTL level data outputs. This includes: 8 Red, 8 Green, 8 Blue, and 4 control lines — FPLINE, FPFRAME, DRDY (also referred to as HSYNC, VSYNC, Data Enable). |

| RxCLK IN+            | 1   | 1   | Positive LVDS differential clock input.                                                                                                                     |

| RxCLK IN-            | ı   | 1   | Negative LVDS differential clock input.                                                                                                                     |

| FPSHIFT OUT          | 0   | 1   | TTL level clock output. The falling edge acts as data strobe. Pin name RxCLK OUT.                                                                           |

| PWR DOWN             | I   | 1   | TTL level input. When asserted (low input) the receiver outputs are low.                                                                                    |

| V <sub>CC</sub>      | 1   | 4   | Power supply pins for TTL outputs.                                                                                                                          |

| GND                  | I   | 5   | Ground pins for TTL outputs.                                                                                                                                |

| PLL V <sub>CC</sub>  | 1   | 1   | Power supply for PLL.                                                                                                                                       |

| PLL GND              | 1   | 2   | Ground pin for PLL.                                                                                                                                         |

| LVDS V <sub>CC</sub> | I   | 1   | Power supply pin for LVDS inputs.                                                                                                                           |

| LVDS GND             | 1   | 3   | Ground pins for LVDS inputs.                                                                                                                                |

| DS90CF384 64 ball FBGA package Pin Description—FPD Link Receiver |     |     |                                                                                                                                                             |  |  |  |

|------------------------------------------------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                         | I/O | No. | Description                                                                                                                                                 |  |  |  |

| RxIN+                                                            | I   | 4   | Positive LVDS differential data inputs.                                                                                                                     |  |  |  |

| RxIN-                                                            | I   | 4   | Negative LVDS differential data inputs.                                                                                                                     |  |  |  |

| RxOUT                                                            | 0   | 28  | TTL level data outputs. This includes: 8 Red, 8 Green, 8 Blue, and 4 control lines — FPLINE, FPFRAME, DRDY (also referred to as HSYNC, VSYNC, Data Enable). |  |  |  |

| RxCLK IN+                                                        | I   | 1   | Positive LVDS differential clock input.                                                                                                                     |  |  |  |

| RxCLK IN-                                                        | I   | 1   | Negative LVDS differential clock input.                                                                                                                     |  |  |  |

| FPSHIFT OUT                                                      | 0   | 1   | TTL level clock output. The falling edge acts as data strobe. Pin name RxCLK OUT.                                                                           |  |  |  |

| PWR DOWN                                                         | I   | 1   | TTL level input. When asserted (low input) the receiver outputs are low.                                                                                    |  |  |  |

| V <sub>CC</sub>                                                  | I   | 4   | Power supply pins for TTL outputs.                                                                                                                          |  |  |  |

| GND                                                              | I   | 5   | Ground pins for TTL outputs.                                                                                                                                |  |  |  |

| PLL V <sub>CC</sub>                                              | - 1 | 1   | Power supply for PLL.                                                                                                                                       |  |  |  |

| PLL GND                                                          | I   | 2   | Ground pin for PLL.                                                                                                                                         |  |  |  |

| LVDS V <sub>CC</sub>                                             | I   | 1   | Power supply pin for LVDS inputs.                                                                                                                           |  |  |  |

| LVDS GND                                                         | I   | 3   | Ground pins for LVDS inputs.                                                                                                                                |  |  |  |

| NC                                                               |     | 6   | Pins not connected.                                                                                                                                         |  |  |  |

# **Applications Information**

The DS90C383 and DS90CF384 are backward compatible with the existing 5V FPD Link transmitter/receiver pair (DS90CR583, DS90CR584, DS90CF583 and DS90CF584). To upgrade from a 5V to a 3.3V system the following must be addressed:

- 1. Change 5V power supply to 3.3V. Provide this supply to the  $\rm V_{CC}, LVDS~V_{CC}$  and PLL  $\rm V_{CC}$  of both the transmitter and receiver devices. This change may enable the removal of a 5V supply from the system, and power may be supplied from an existing 3V power source.

- 2. The DS90C383 (transmitter) incorporates a rise/fall strobe select pin. This select function is on pin 17, formerly a V<sub>CC</sub> connection on the 5V products. When the rise/fall strobe select pin is connected to V<sub>CC</sub>, the part is configured with a rising edge strobe. In a system currently using a 5V rising edge strobe transmitter (DS90CR583), no layout changes are required to accommodate the new rise/fall select pin on the 3.3V transmitter. The V<sub>CC</sub> signal may remain at pin 17, and the device will be configured with a rising edge strobe.

When converting from a 5V falling edge transmitter (DS90CF583) to the 3V transmitter a minimal board layout change is necessary. The 3.3V transmitter will not be configured with a falling edge strobe if  $V_{\rm CC}$  remains connected to the select pin. To guarantee the 3.3V transmitter functions with a falling edge strobe pin 17 should be connected to ground OR left unconnected. When not connected (left open) and internal pull-down resistor ties pin 17 to ground, thus configuring the transmitter with a falling edge strobe.

The DS90C383 transmitter input and control inputs accept 3.3V TTL/CMOS levels. They are not 5V tolerant.

**TABLE 1. Programmable Transmitter**

| Pin  | Condition       | Strobe Status       |

|------|-----------------|---------------------|

| R_FB | $R_FB = V_{CC}$ | Rising edge strobe  |

| R_FB | R_FB = GND      | Falling edge strobe |

|          | By Pin   |          |     | By Pin Type      |                                                  |

|----------|----------|----------|-----|------------------|--------------------------------------------------|

| in       | Pin Name | Туре     | Pin | Pin Name         | Тур                                              |

| .1       | RxOUT17  | 0        | A4  | GND              | G                                                |

| 2        | VCC      | Р        | B1  | GND              | G                                                |

| 3        | RxOUT15  | 0        | B6  | GND              | G                                                |

|          | GND      | G        | D8  | GND              | G                                                |

|          | RxOUT12  | 0        | E3  | GND              | G                                                |

| 3        | RxOUT8   | 0        | E5  | LVDS GND         | G                                                |

| ,        | RxOUT7   | 0        | G3  | LVDS GND         | G                                                |

| 3        | RxOUT6   | 0        | G7  | LVDS GND         | G                                                |

|          | GND      | G        | H5  | LVDS GND         | G                                                |

| <u> </u> | NC       |          | F6  | PLL GND          | G                                                |

| }        | RxOUT16  | 0        | G8  | PLL GND          | G                                                |

| <u>'</u> | RxOUT11  | 0        | E6  | PWR DWN          | 1                                                |

| 5        | VCC      | P        | H6  | RxCLKIN-         | + i                                              |

| 3<br>6   | GND      | G        | H7  | RxCLKIN+         | <del>                                     </del> |

| 7        | RxOUT5   | 0        | H2  | RxIN0-           | <u>'</u>                                         |

| ,<br>3   | RxOUT3   | 0        | H3  | RxIN0+           |                                                  |

| 1        | RxOUT21  | 0        | F4  | RxIN1-           | 1                                                |

| 2        | NC NC    |          | G4  |                  | 1                                                |

|          |          | 0        | G5  | RxIN1+<br>RxIN2- |                                                  |

| 3        | RxOUT18  | 0        |     |                  | 1                                                |

| 4        | RxOUT14  | 0        | F5  | RxIN2+           | 1                                                |

| 5        | RxOUT9   | 0        | G6  | RxIN3-           |                                                  |

| 6        | RxOUT4   | 0        | H8  | RxIN3+           |                                                  |

| 7        | NC       |          | E7  | RxCLKOUT         | 0                                                |

| 3        | RxOUT1   | 0        | E8  | RxOUT0           | 0                                                |

| 1        | VCC      | Р        | C8  | RxOUT1           | 0                                                |

| 2        | RxOUT20  | 0        | D5  | RxOUT10          | 0                                                |

| 3        | RxOUT19  | 0        | B4  | RxOUT11          | 0                                                |

| 1        | RxOUT13  | 0        | A5  | RxOUT12          | 0                                                |

| 5        | RxOUT10  | 0        | D4  | RxOUT13          | 0                                                |

| 6        | VCC      | Р        | C4  | RxOUT14          | 0                                                |

| 7        | RxOUT2   | 0        | A3  | RxOUT15          | 0                                                |

| 8        | GND      | G        | B3  | RxOUT16          | 0                                                |

| 1        | RxOUT22  | 0        | A1  | RxOUT17          | 0                                                |

| 2        | RxOUT24  | 0        | C3  | RxOUT18          | 0                                                |

| 3        | GND      | G        | D3  | RxOUT19          | 0                                                |

| 4        | LVDS VCC | Р        | D7  | RxOUT2           | 0                                                |

| ;        | LVDS GND | G        | D2  | RxOUT20          | 0                                                |

| 6        | PWR DWN  | I        | C1  | RxOUT21          | 0                                                |

| 7        | RxCLKOUT | 0        | E1  | RxOUT22          | 0                                                |

| 3        | RxOUT0   | 0        | F1  | RxOUT23          | 0                                                |

| 1        | RxOUT23  | 0        | E2  | RxOUT24          | 0                                                |

|          | RxOUT26  | 0        | G1  | RxOUT25          | 0                                                |

| 3        | NC       |          | F2  | RxOUT26          | 0                                                |

| 4        | RxIN1-   | I        | H1  | RxOUT27          | 0                                                |

| 5        | RxIN2+   | <u>·</u> | B8  | RxOUT3           | 0                                                |

| 5<br>5   | PLL GND  | G        | C6  | RxOUT4           | 0                                                |

| 7        | PLL VCC  | P        | B7  | RxOUT5           | 0                                                |

| 3        | NC NC    | •        | A8  | RxOUT6           | 0                                                |

# DS90CF384 64 ball, FBGA package pin definition—FPD Link Receiver (Continued)

|    | By Pin   |   | By Pin Type |          |   |  |

|----|----------|---|-------------|----------|---|--|

| G1 | RxOUT25  | 0 | A7          | RxOUT7   | 0 |  |

| G2 | NC       |   | A6          | RxOUT8   | 0 |  |

| G3 | LVDS GND | G | C5          | RxOUT9   | 0 |  |

| G4 | RxIN1+   | I | E4          | LVDS VCC | Р |  |

| G5 | RxIN2-   | I | H4          | LVDS VCC | Р |  |

| G6 | RxIN3-   | I | F7          | PLL VCC  | Р |  |

| G7 | LVDS GND | G | A2          | VCC      | Р |  |

| G8 | PLL GND  | G | B5          | VCC      | Р |  |

| H1 | RxOUT27  | 0 | D1          | VCC      | Р |  |

| H2 | RxIN0-   | I | D6          | VCC      | Р |  |

| H3 | RxIN0+   | I | B2          | NC       |   |  |

| H4 | LVDS VCC | Р | C2          | NC       |   |  |

| H5 | LVDS GND | G | C7          | NC       |   |  |

| H6 | RxCLKIN- | I | F3          | NC       |   |  |

| H7 | RxCLKIN+ | I | F8          | NC       |   |  |

| H8 | RxIN3+   | I | G2          | NC       |   |  |

G:Ground I: Input O:Output P:Power NC:Not connectted

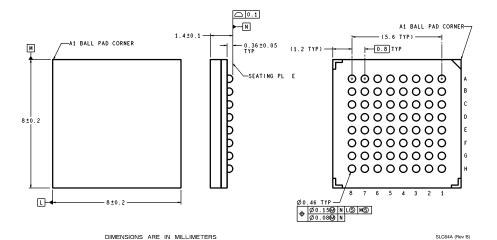

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

64 ball, 0.8mm fine pitch ball grid array(FBGA) Package

Dimensions show in millimeters

Order Number DS90CF384SLC

NS Package Number SLC64A

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

# National Semiconductor

Fax: 449 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: 449 (0) 1 80-530 85 85

English Tel: 449 (0) 1 80-532 78 32

Français Tel: 449 (0) 1 80-532 93 58

Italiano Tel: 449 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com

emiconductor National Semiconductor c Customer Japan Ltd.

Group Tel: 81-3-5639-7560

4466 Fax: 81-3-5639-7507

## IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

# Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

TI E2E Community Home Page <u>e2e.ti.com</u>

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated