# National Semiconductor

## DS8924 Quad TRI-STATE® Differential Line Driver

## **General Description**

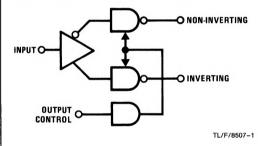

The DS8924 is a guad differential line driver designed for digital data transmission over balanced lines. The outputs are TRI-STATE® structures which are forced to a high impedance state when the appropriate output control pin reaches a logic zero condition. All input pins are PNP buffered to minimize input loading for either logic one or logic zero inputs. In addition, internal circuitry assures a high impedance output state during the transition between power up and power down.

The DS8924 is pin and functionally compatible with DS3487. It features improved performance over 3487-type circuit as outputs can source and sink 48 mA. In addition. outputs are not significantly affected by negative line reflections that can occur when the transmission line is unterminated at the receiver end.

#### **Features**

- Four independent driver chains

- TRI-STATE outputs

- PNP high impedance inputs

- Power up/down protection

- Fast propagation times (typ 12 ns)

- TTL compatible

- Single 5V supply voltage

- Output rise and fall times less than 20 ns (typ 10 ns)

- Pin compatible with DS3487 and MC3487

- Output skew--2 ns typ

GND

## **Block and Connection Diagrams**

# 16 VCC INPUT A INPUT D **OUTPUTS A OUTPUTS D** A/B CONTROL C/D CONTROL **OUTPUTS B** OUTPUTS C INPUT B

**Dual-In-Line Package**

**Top View**

INPUT C

TL/F/8507-2

Order Number DS8924J or N See NS Package J16A or N16A

### **Truth Table**

| Input | Control<br>Input | Non-Inverter<br>Output | Inverter<br>Output |

|-------|------------------|------------------------|--------------------|

| Н     | Н                | Н                      | L                  |

| L     | Н                | L                      | н                  |

| Х     | L                | Z                      | Z                  |

- L = Low logic state

- H = High logic state

- X = Irrelevant

- Z = TRI-STATE (high impedance)