# DS8921/DS8921A Differential Line Driver and Receiver Pair

### **General Description**

The DS8921, DS8921A are Differential Line Driver and Receiver pairs designed specifically for applications meeting the ST506, ST412 and ESDI Disk Drive Standards. In addition, these devices meet the requirements of the EIA Standard RS-422.

The DS8921A receiver offers an input sensitivity of 200 mV over a  $\pm$ 7V common mode operating range. Hysteresis is incorporated (typically 70 mV) to improve noise margin for slowly changing input waveforms. An input fail-safe circuit is provided such that if the receiver inputs are open the output assumes the logical one state.

The DS8921A driver is designed to provide unipolar differential drive to twisted pair or parallel wire transmission lines. Complementary outputs are logically ANDed and provide an output skew of 0.5 ns (typ.) with propagation delays of 12 ns.

Power up/down circuitry is featured which will TRI-STATE® the outputs and prevent erroneous glitches on the trans-

mission lines during system power up or power down opera-

The DS8921A is designed to be compatible with TTL and CMOS.

#### **Features**

- 12 ns typical propagation delay

- Output skew 0.5 ns typical

- Meet the requirements of EIA Standard RS-422

- Complementary Driver Outputs

- High differential or common-mode input voltage ranges of ±7V

- ±0.2V receiver sensitivity over the input voltage range

- Receiver input fail-safe circuitry

- Receiver input hysteresis-70 mV typical

- Glitch free power up/down

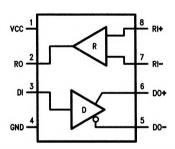

## **Connection Diagram**

TL/F/8512-1

Order Number DS8921M, DS8921AM, DS8921AN, DS8921AJ or DS8921AJ See NS Package Number J08A, M08A or N08E

## **Truth Table**

| Receiver                   |                  | Driver |      |      |

|----------------------------|------------------|--------|------|------|

| Input                      | V <sub>OUT</sub> | Input  | Vout | Vout |

| $V_{ID} \ge V_{TH} (MAX)$  | 1                | 1      | 1    | 0    |

| $V_{ID} \leq V_{TH} (MIN)$ | 0                | 0      | 0    | 1    |

For complete specifications see the Interface Databook.