# DS8906 AM/FM Digital Phase-Locked Loop Synthesizer

#### **General Description**

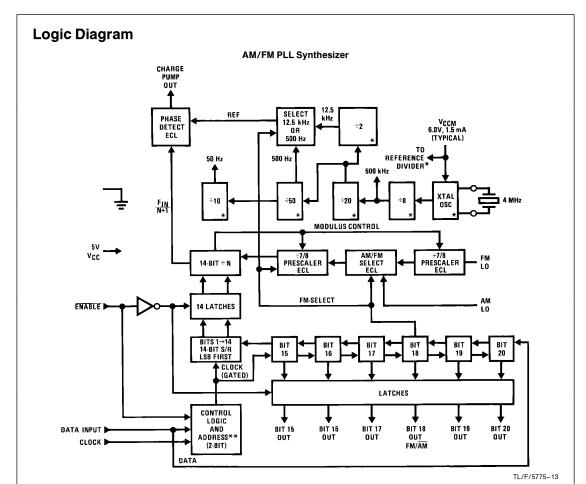

The DS8906 is a PLL synthesizer designed specifically for use in AM/FM radios. It contains the reference oscillator, a phase comparator, a charge pump, a 120 MHz ECL/I²L dual modulus programmable divider, and a 20-bit shift register/latch for serial data entry. The device is designed to operate with a serial data controller generating the necesary division codes for each frequency, and logic state information for radio function inputs/outputs.

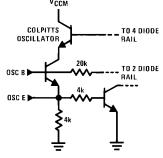

The Colpitts reference oscillator for the PLL operates at 4 MHz. A chain of dividers is used to generate a 500 kHz clock signal for the external controller. Additional dividers generate a 12.5 kHz reference signal for FM and a 500 Hz reference signal for AM/SW. One of these reference signals is selected by the data from the controller for use by the phase comparator. Additional dividers are used to generate a 50 Hz timing signal used by the controller for "time-of-dav".

Data is transferred between the frequency synthesizer and the controller via a 3 wire bus system. This consists of a data input line, an enable line and a clock line. When the enable line is low, data can be shifted from the controller into the frequency synthesizer. When the enable line is transitioned from low to high, data entry is disabled and data present in the shift register is latched.

From the controller 22-bit data stream, the first 2 bits address the device permitting other devices to share the same bus. Of the remaining 20-bit data word, the next 14-bits are used for the PLL divide code. The remaining 6 bits are connected via latches to output pins. These 6 bits can be used to drive radio functions such as gain, mute, FM, AM, LW and SW only. These outputs are open collector. Bit 18 is used internally to select the AM or FM local oscillator input and to select between the 500 Hz and 12.5 kHz reference. A high level at bit 18 indicates FM and a low level indicates AM.

The PLL consists of a 14-bit programmable I²L divider, an ECL phase comparator, an ECL dual modulus (p/p  $\pm$  1) prescaler, and a high speed charge pump. The programmable divider divides by (N+1), N being the number loaded into the shift register (bits 1–14 after address). It is clocked by the AM input via an ECL  $\pm$  7/8 prescaler, or through a  $\pm$  63/64 prescaler from the FM input. The AM input will work at frequencies up to 8 MHz, while the FM input works up to 120 MHz. The AM band is tuned with a frequency resolution of 500 Hz and the FM band is tuned with a resolution of 12.5 kHz. The buffered AM and FM inputs are self-biased and can be driven directly by the VCO thru a capacitor. The ECL phase comparator produces very accurate resolution of the phase difference between the input signal and the reference oscillator.

The high speed charge pump consists of a switchable constant current source (-0.3 mA) and a switchable constant current sink (+0.3 mA). If the VCO frequency is low, the charge pump will source current, and sink current if the VCO frequency is high.

A separate V<sub>CCM</sub> pin (typically drawing 1.5 mA) powers the oscillator and reference chain to provide controller clocking frequencies when the balance of the PLL is powered down.

#### **Features**

- Uses inexpensive 4 MHz reference crystal

- F<sub>IN</sub> capability greater than 120 MHz allows direct synthesis at FM frequencies

- FM resolution of 12.5 kHz allows usage of 10.7 MHz ceramic filter distribution

- Serial data entry for simplified control

- 50 Hz output for "time-of-day" reference with separate low power supply (V<sub>CCM</sub>)

- 6-open collector buffered outputs for band switching and other radio functions

- Separate AM and FM inputs. AM input has 15 mV (typical) hysteresis

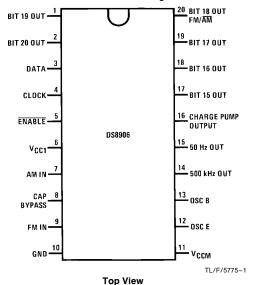

### **Connection Diagram**

#### **Dual-In-Line Package**

Order Number DS8906N See NS Package Number N20A

TRI-STATE® is a registered trademark of National Semiconductor Corp

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage 7V 7V (V<sub>CC1</sub>)  $(V_{CCM})$ Input Voltage 7V Output Voltage 7V Storage Temperature Range – Lead Temperature (Soldering, 4 seconds)  $-65^{\circ}$ C to  $+150^{\circ}$ C

**Operating Conditions**

|                                 | Min  | Max  | Units |

|---------------------------------|------|------|-------|

| Supply Voltage, V <sub>CC</sub> |      |      |       |

| V <sub>CC1</sub>                | 4.75 | 5.25 | V     |

| $V_{CCM}$                       | 4.5  | 6.0  | V     |

| Temperature, T <sub>A</sub>     | 0    | 70   | °C    |

# DC Electrical Characteristics (Notes 2 and 3)

| Symbol                     | Parameter                                                   | Conditions                                                              |            |       | Тур   | Max  | Units |

|----------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------|------------|-------|-------|------|-------|

| V <sub>IH</sub>            | Logical "1" Input Voltage                                   |                                                                         |            | 2.1   |       |      | ٧     |

| I <sub>IH</sub>            | Logical "1" Input Current                                   | V <sub>IN</sub> =V <sub>CC1</sub>                                       |            |       | 0     | 10   | μΑ    |

| V <sub>IL</sub>            | Logical "0" Input Voltage                                   |                                                                         |            |       |       | 0.7  | ٧     |

| I <sub>IL</sub>            | Logical "0" Input Current                                   | Data, Clock and ENABLE INPUTS, VIN = 0V                                 |            |       | -5    | -25  | μΑ    |

| ГОН                        | Logical "1" Output Current<br>All Bit Outputs, 50 Hz Output | V <sub>OH</sub> =5.25V                                                  |            |       | 50    | μА   |       |

|                            | 500 kHz Output                                              | V <sub>OH</sub> =2.4V, V <sub>CCM</sub> =4.5V                           |            |       |       | -250 | μΑ    |

| V <sub>OL</sub>            | Logical "0" Output Voltage<br>All Bit Outputs               | I <sub>OL</sub> =5 mA                                                   |            |       | 0.5   | V    |       |

|                            | 50 Hz Output, 500 kHz Output                                | I <sub>OL</sub> =250 μA                                                 |            |       | -0.5  | ٧    |       |

| I <sub>CC1</sub>           | Supply Current (V <sub>CC1</sub> )                          | All Bit Outputs High                                                    |            |       | 90    | 160  | mA    |

| ICCM(STANDBY)              | V <sub>CCM</sub> Supply Current                             | V <sub>CCM</sub> =6.0V, All Other Pins Open                             |            |       | 1.5   | 4.0  | mA    |

| lout                       | Charge Pump Output Current                                  | V <sub>CCM</sub> ≤6.0V                                                  | Pump Up    | -0.10 | -0.30 | -0.6 | mA    |

|                            |                                                             |                                                                         | Pump Down  | 0.10  | 0.30  | 0.6  | mA    |

|                            |                                                             |                                                                         | TRI-STATE® |       | 0     | ±100 | nA    |

| I <sub>CCM</sub> (OPERATE) | V <sub>CCM</sub> Supply Current                             | V <sub>CCM</sub> =6.0V, V <sub>CC1</sub> =5.25V,<br>All Other Pins Open |            |       | 2.5   | 6.0  | mA    |

# AC Electrical Characteristics $v_{CC}=5V, T_A=25^{\circ}C, t_f \leq 10 \text{ ns}, t_f \leq 10 \text{ ns}$

| Symbol                       | Parameter                                                                          | Conditions                                                                                                                                                                                                                              | Min       | Тур  | Max      | Units      |

|------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|----------|------------|

| V <sub>IN(MIN)(F)</sub>      | F <sub>IN</sub> Minimum Signal Input                                               | AM and FM Inputs, $0^{\circ}C \le T_A \le 70^{\circ}C$                                                                                                                                                                                  |           | 20   | 100      | mV (rms)   |

| V <sub>IN(MAX)(F)</sub>      | F <sub>IN</sub> Maximum Signal Input                                               | AM and FM Inputs, $0^{\circ}C \le T_A \le 70^{\circ}C$                                                                                                                                                                                  | 1000      | 1500 |          | mV (rms)   |

| FOPERATE                     | Operating Frequency Range (Sine Wave Input)                                        | $ \begin{array}{c} V_{\mbox{\footnotesize{IN}}} = 100 \mbox{ mV rms} & \mbox{AM} \\ 0^{\circ} \mbox{\footnotesize{C}} \leq T_{\mbox{\footnotesize{A}}} \leq 70^{\circ} \mbox{\footnotesize{C}} & \mbox{\footnotesize{FM}} \end{array} $ | 0.4<br>60 |      | 8<br>120 | MHz<br>MHz |

| R <sub>IN</sub> (FM)         | AC Input Resistance, FM                                                            | 120 MHz, V <sub>IN</sub> = 100 mV rms                                                                                                                                                                                                   | 300       |      |          | Ω          |

| R <sub>IN</sub> (AM)         | AC Input Resistance, AM                                                            | 2 MHz, V <sub>IN</sub> = 100 mV rms                                                                                                                                                                                                     | 1000      |      |          | Ω          |

| C <sub>IN</sub>              | Input Capacitance, FM and AM                                                       | V <sub>IN</sub> = 120 MHz                                                                                                                                                                                                               | 3         | 6    | 10       | pF         |

| t <sub>EN1</sub>             | Minimum ENABLE High<br>Pulse Width                                                 |                                                                                                                                                                                                                                         |           | 625  | 1250     | ns         |

| t <sub>EN0</sub>             | Minimum ENABLE Low Pulse Width                                                     |                                                                                                                                                                                                                                         |           | 375  | 750      | ns         |

| t <sub>CLKEN0</sub>          | Minimum Time before ENABLE<br>Goes Low that CLOCK must<br>be Low                   |                                                                                                                                                                                                                                         |           | -50  | 0        | ns         |

| t <u>EN</u> 0CLK             | Minimum Time after ENABLE<br>Goes Low that CLOCK must<br>Remain Low                |                                                                                                                                                                                                                                         |           | 275  | 550      | ns         |

| <sup>†</sup> CLK <u>EN</u> 1 | Minimum Time before ENABLE<br>Goes High that Last Positive<br>CLOCK Edge May Occur |                                                                                                                                                                                                                                         |           | 300  | 600      | ns         |

# AC Electrical Characteristics $V_{CC}=5V, T_A=25^{\circ}C, t_f \leq 10 \text{ ns, } t_f \leq 10 \text{ ns (Continued)}$

| Symbol              | Parameter                                                                                | Conditions | Min | Тур | Max | Units |

|---------------------|------------------------------------------------------------------------------------------|------------|-----|-----|-----|-------|

| <sup>t</sup> EN1CLK | Minimum Time After ENABLE<br>Goes High Before an Unused<br>Positive CLOCK Edge May Occur |            |     | 175 | 350 | ns    |

| <sup>t</sup> CLKH   | Minimum CLOCK High<br>Pulse Width                                                        |            |     | 275 | 550 | ns    |

| <sup>t</sup> CLKL   | Minimum CLOCK Low<br>Pulse Width                                                         |            |     | 400 | 800 | ns    |

| t <sub>DS</sub>     | Minimum DATA Setup Time,<br>Minimum Time Before CLOCK<br>that DATA Must be Valid         |            |     | 150 | 300 | ns    |

| <sup>t</sup> DH     | Minimum DATA Hold Time,<br>Minimum Time After CLOCK<br>that DATA Must Remain Valid       |            |     | 400 | 800 | ns    |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified min/max limits apply across the  $0^{\circ}$ C to  $+70^{\circ}$ C temperature range for the DS8906.

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as may or min on absolute value basis

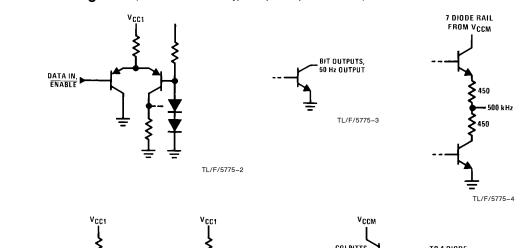

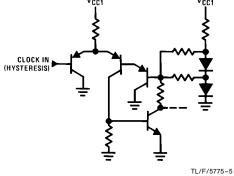

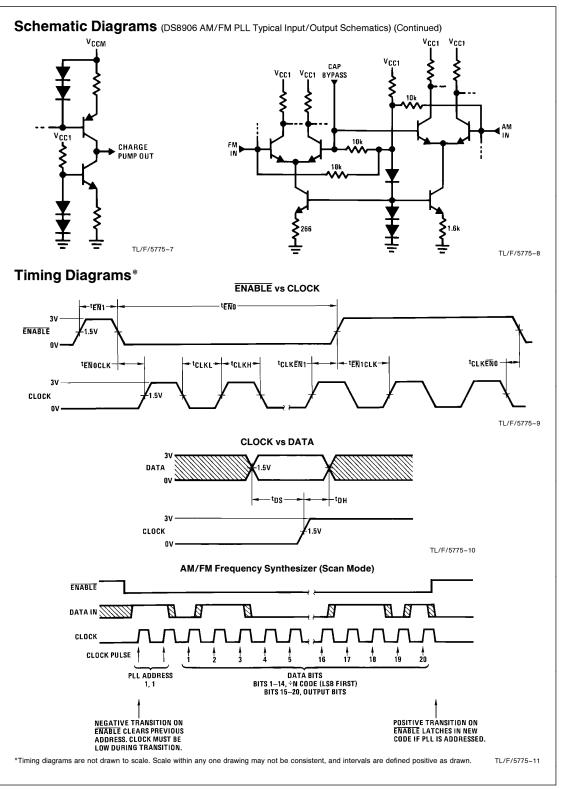

## Schematic Diagrams (DS8906 AM/FM PLL Typical Input/Output Schematics)

TL/F/5775-6

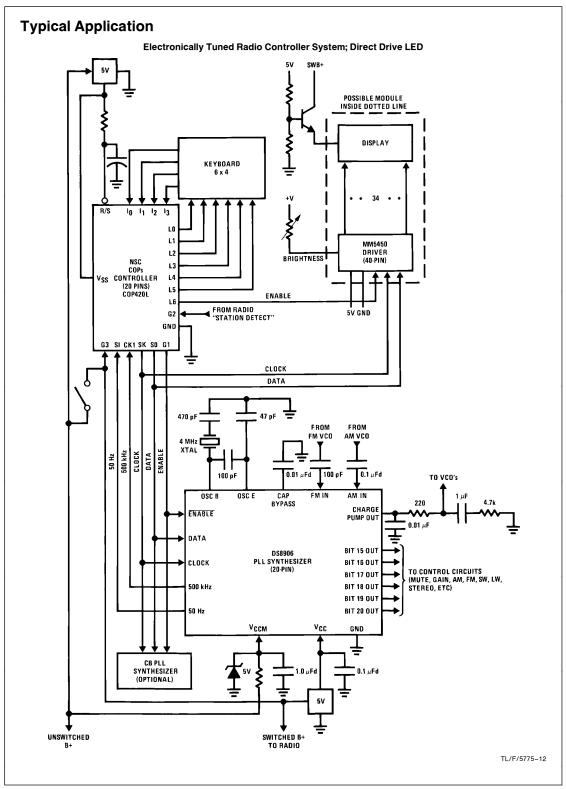

### **Applications Information**

### SERIAL DATA ENTRY INTO THE DS8906

Serial information entry into the DS8906 is enabled by a low level on the <code>ENABLE</code> input. One binary bit is then accepted from the DATA input with each positive transition of the CLOCK input. The CLOCK input must be low for the specified time preceding and following the negative transition of the <code>ENABLE</code> input.

The first 2 bits accepted following the negative transition of the  $\overline{\text{ENABLE}}$  input are interpreted as address. If these address bits are not 1,1, no further information will be accepted from the DATA inputs, and the internal data latches will not be changed when  $\overline{\text{ENABLE}}$  returns high.

If these first 2 bits *are* 1,1, then all succeeding bits are *accepted* as data, and are shifted successively into the internal shift register as long as ENABLE remains low.

Any data bits preceding the 20th to last bit will be shifted out, and are thus irrelevant. Data bits are counted as any bits following 2 valid (1,1) address bits with the  $\overline{\text{ENABLE}}$  low.

When the <code>\overline{ENABLE}</code> input returns high, any further serial data input is inhibited. Upon this positive transition of the <code>\overline{ENABLE}</code>, the data in the internal shift register is transferred into the internal data latches.

Note that until this time, the states of the internal data latches have remained unchanged.

These data bits are interpreted as follows:

| DATA BIT POSITION | DATA INTERPRETATION            |

|-------------------|--------------------------------|

| Last              | Bit 20 Output (Pin 2)          |

| 2nd to Last       | Bit 19 Output (Pin 1)          |

| 3rd to Last       | Bit 18 Output (FM/AM) (Pin 20) |

| 4th to Last       | Bit 17 Output (Pin 19)         |

| 5th to Last       | Bit 16 Output (Pin 18)         |

| 6th to Last       | Bit 15 Output (Pin 17)         |

| 7th to Last       | MSB of N (2 <sup>13</sup> )    |

| 8th to Last       | (2 <sup>12</sup> )             |

| 9th to Last       | (2 <sup>11</sup> )             |

| 10th to Last      | (2 <sup>10</sup> )             |

| 11th to Last      | (2 <sup>9</sup> )              |

| 12th to Last      | (28)                           |

| 13th to Last      | $(2^7)$ $\rightarrow N$        |

| 14th to Last      | (2 <sup>6</sup> )              |

| 15th to Last      | (2 <sup>5</sup> )              |

| 16th to Last      | (24)                           |

| 17th to Last      | (2 <sup>3</sup> )              |

| 18th to Last      | (2 <sup>2</sup> )              |

| 19th to Last      | (2 <sup>1</sup> )              |

| 20th to Last      | LSB of N (2 <sup>0</sup> ) J   |

Note. The actual divide code is N+1, i.e., the number loaded plus 1.

\*Sections operating from  $V_{\mbox{\footnotesize{CCM}}}$  supply

\*\*Address (1, 1)

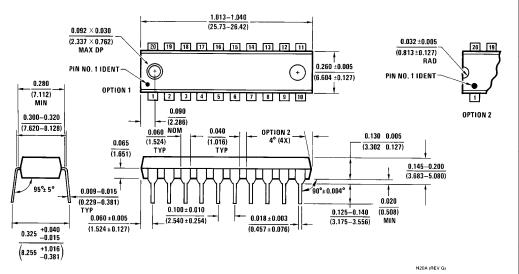

## Physical Dimensions inches (millimeters)

Molded Dual-In-Line Package (N) Order Number DS8906N NS Package Number N20A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408