# DS75325 Memory Drivers

# **General Description**

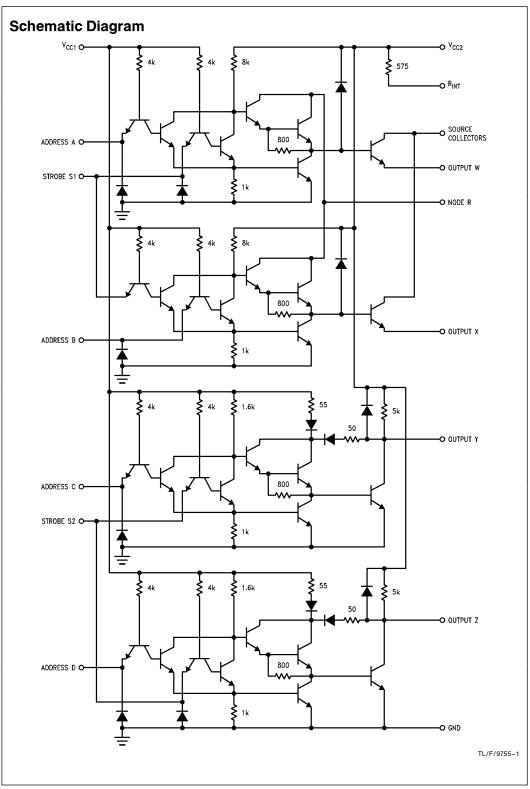

The DS75325 is a monolithic memory driver which features high current outputs as well as internal decoding of logic inputs. This circuit is designed for use with magnetic memories

The circuit contains two 600 mA sink-switch pairs and two 600 mA source-switch pairs. Inputs A and B determine source selection while the source strobe (S1) allows the selected source turn on. In the same manner, inputs C and D determine sink selection while the sink strobe (S2) allows the selected sink turn on.

Sink-output collectors feature an internal pull-up resistor in parallel with a clamping diode connected to  $V_{\rm CC2}$ . This protects the outputs from voltage surges associated with switching inductive loads.

The source stage features Node R which allows extreme flexibility in source current selection by controlling the amount of base drive to each source transistor. This method of setting the base drive brings the power associated with the resistor outside the package thereby allowing the circuit

to operate at higher source currents for a given junction temperature. If this method of source current setting is not desired, then Nodes R and R $_{\rm INT}$  can be shorted externally, activating an internal resistor connected from V $_{\rm CC2}$  to Node R. This provides adequate base drive for source currents up to 375 mA with V $_{\rm CC2}=15{\rm V}$  or 600 mA with V $_{\rm CC2}=24{\rm V}$ .

### **Features**

- 600 mA output capability

- 24V output capability

- Dual sink and dual source outputs

- Fast switching times

- Source base drive externally adjustable

- Input clamping diodes

- TTL compatible

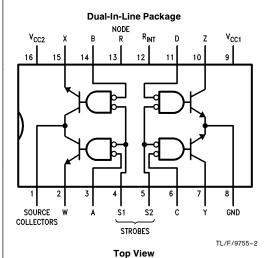

# **Connection Diagram**

Order Number DS75325N See NS Package Number N14A

### **Truth Table**

| Add | Address Inputs Strobe Inputs Outputs |   |    |        |                   |     |      |      |     |

|-----|--------------------------------------|---|----|--------|-------------------|-----|------|------|-----|

| Sou | Source Sink                          |   | nk | Source | Source Sink Sourc |     | ırce | Sink |     |

| Α   | В                                    | С | D  | S1     | S2                | W   | Χ    | Υ    | Z   |

| L   | Н                                    | Х | Χ  | L      | Н                 | ON  | OFF  | OFF  | OFF |

| Н   | L                                    | Х | Χ  | L      | Н                 | OFF | ON   | OFF  | OFF |

| X   | Χ                                    | L | Н  | Н      | L                 | OFF | OFF  | ON   | OFF |

| X   | Χ                                    | Н | L  | Н      | L                 | OFF | OFF  | OFF  | ON  |

| Х   | Χ                                    | Х | Χ  | Н      | Н                 | OFF | OFF  | OFF  | OFF |

| Н   | Н                                    | Н | Н  | X      | X                 | OFF | OFF  | OFF  | OFF |

H = High Level, L = Low Level, X = Irrelevant

Note: Not more than one output is to be on at any one time.

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage  $V_{CC1}$  (Note 5) 7V Supply Voltage  $V_{CC2}$  (Note 5) 25V Input Voltage (Any Address or Strobe Input) 5.5V Maximum Power Dissipation\* at 25°C

Cavity Package 1509 mW Molded Package 1476 mW

# Storage Temperature Range $-65^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ Lead Temperature (Soldering, 10 seconds) $300^{\circ}\text{C}$

# **Operating Conditions**

| IVIIN | wax | Units |

|-------|-----|-------|

|       |     |       |

| 0     | +70 | °C    |

|       |     |       |

# Electrical Characteristics (Notes 2 and 3)

| Symbol              | Parameter                                                            | Conditi                                                                                                 | ons                   |         | Min | Тур  | Max  | Units |

|---------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|---------|-----|------|------|-------|

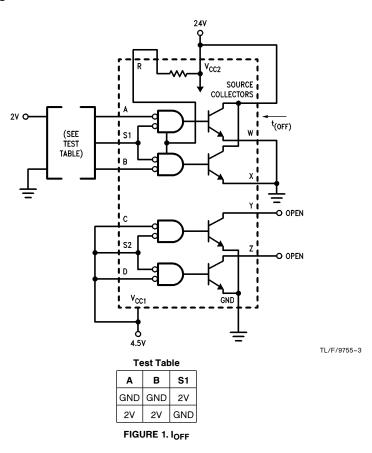

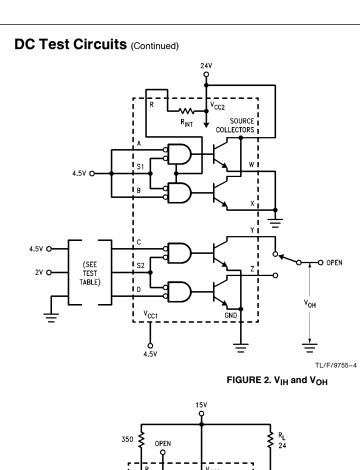

| V <sub>IH</sub>     | High Level Input Voltage                                             | (Figures 1 and 2)                                                                                       |                       |         | 2   |      |      | ٧     |

| V <sub>IL</sub>     | Low Level Input Voltage                                              | (Figures 3 and 4)                                                                                       |                       |         |     |      | 0.8  | ٧     |

| VI                  | Input Clamp Voltage                                                  | $V_{CC1} = 4.5V$ , $V_{CC2} = 24V$ , $I_{IN} = -12 \text{ mA}$<br>$T_A = 25^{\circ}\text{C}$ (Figure 5) |                       |         |     | -1.3 | -1.7 | ٧     |

| loff                | Source Collectors Terminal V <sub>CC1</sub> = 4.5V, V <sub>CC2</sub> |                                                                                                         | Full Range            | DS55325 |     |      | 500  | μΑ    |

|                     | "Off" State Current                                                  | (Figure 1)                                                                                              |                       | DS75325 |     |      | 200  | μΑ    |

|                     |                                                                      | $T_A = 25^{\circ}C$                                                                                     | DS55325               |         | 3   | 150  | μΑ   |       |

|                     |                                                                      |                                                                                                         |                       | DS75325 |     | 3    | 200  | μΑ    |

| V <sub>OH</sub>     | High Level Sink Output Voltage                                       | V <sub>CC1</sub> = 4.5V, V <sub>CC2</sub> = 24V, I                                                      | OUT = 0 mA (Figure 2) |         | 19  | 23   |      | ٧     |

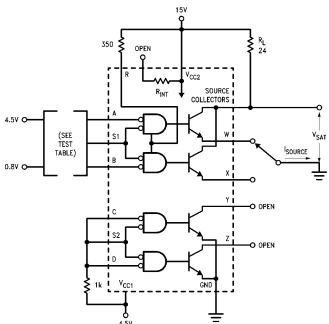

| V <sub>SAT</sub>    | Saturation Voltage Source<br>Outputs                                 | $V_{CC1} = 4.5V, V_{CC2} = 15V,$ $R_L = 24\Omega,$                                                      | Full Range            |         |     |      | 0.9  | ٧     |

|                     |                                                                      | $I_{\text{SOURCE}} \approx -600 \text{mA}$                                                              | $T_A = 25^{\circ}C$   | DS55325 |     | 0.43 | 0.7  | V     |

|                     |                                                                      | (Figure 3) (Notes 4 and 6)                                                                              |                       | DS75325 |     | 0.43 | 0.75 | ٧     |

| V <sub>SAT</sub>    | Saturation Voltage<br>Sink Outputs                                   | $V_{CC1} = 4.5V, V_{CC2} = 15V, Full Range R_L = 24\Omega,$                                             |                       |         |     |      | 0.9  | ٧     |

|                     |                                                                      | I <sub>SINK</sub> ≈ 600 mA (Figure 4)                                                                   | $T_A = 25^{\circ}C$   | DS55325 |     | 0.43 | 0.7  | ٧     |

|                     |                                                                      | (Notes 4 and 6)                                                                                         |                       | DS75325 |     | 0.43 | 0.75 | ٧     |

| II                  | Input Current at Maximum                                             | $V_{CC1} = 5.5V, V_{CC2} = 24V,$                                                                        | Address Inputs        |         |     |      | 1    | mA    |

|                     | Input Voltage                                                        | V <sub>I</sub> = 5.5V <i>(Figure 5)</i>                                                                 | Strobe Input          | s       |     |      | 2    | mA    |

| I <sub>IH</sub>     | High Level Input Current                                             | $V_{CC1} = 5.5V, V_{CC2} = 24V,$                                                                        | Address Inpo          | uts     |     | 3    | 40   | μΑ    |

|                     |                                                                      | $V_1 = 2.4V$ (Figure 5)                                                                                 | Strobe Input          | s       |     | 6    | 80   | μΑ    |

| I <sub>IL</sub>     | Low Level Input Current                                              | $V_{CC1} = 5.5V, V_{CC2} = 24V,$                                                                        | Address Inpo          | uts     |     | -1   | -1.6 | mA    |

|                     |                                                                      | V <sub>I</sub> = 0.4V <i>(Figure 5)</i>                                                                 | gure 5) Strobe Inputs |         |     | -2   | -3.2 | mA    |

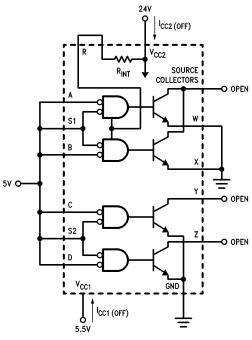

| I <sub>CC OFF</sub> | Supply Current, All Sources                                          | V <sub>CC1</sub> = 5.5V, V <sub>CC2</sub> = 24V, V <sub>CC1</sub>                                       |                       |         | 14  | 22   | mA   |       |

|                     | and Sinks "Off"                                                      | T <sub>A</sub> = 25°C (Figure 6)                                                                        |                       |         |     | 7.5  | 20   | mA    |

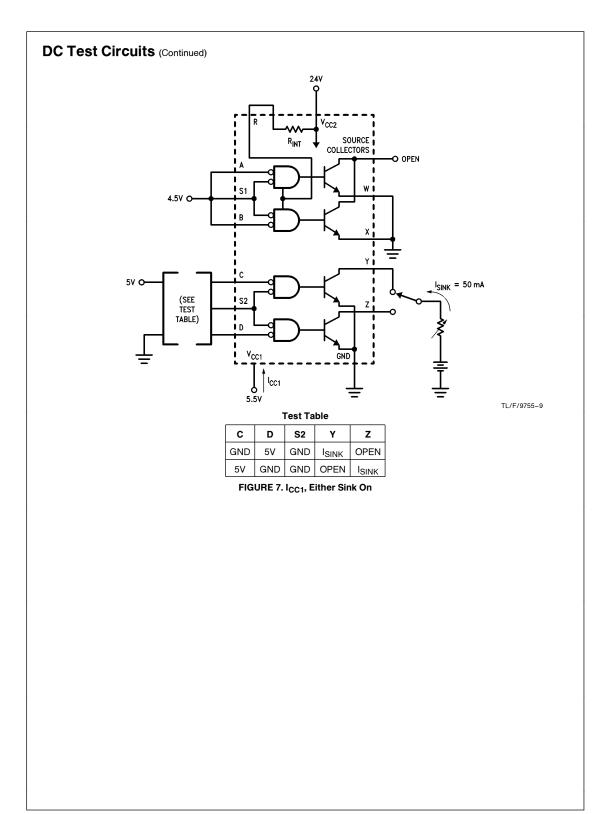

| I <sub>CC1</sub>    | Supply Current from V <sub>CC1</sub> ,<br>Either Sink "On"           | $V_{CC1} = 5.5V$ , $V_{CC2} = 24V$ , $I_{SINK} = 50$ mA,<br>$T_A = 25$ °C (Figure 7)                    |                       |         |     | 55   | 70   | mA    |

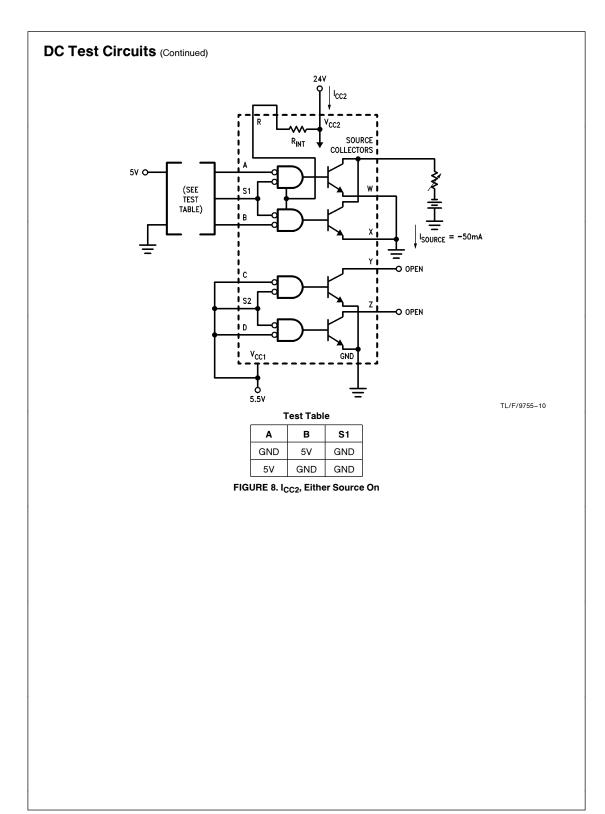

| I <sub>CC2</sub>    | Supply Current from V <sub>CC2</sub> ,<br>Either Source "On"         | $V_{CC1} = 5.5V, V_{CC2} = 24V, I_{A} = 25^{\circ}C $ (Figure 8)                                        | SOURCE = -            | 50 mA   |     | 32   | 50   | mA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified min/max limits apply across the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range for the DS55325 and across the  $0^{\circ}$ C to  $+70^{\circ}$ C range for the DS75325. All typical values are at  $T_{A}=25^{\circ}$ C.

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as max or min on absolute value basis.

Note 4: Only one output at a time should be shorted.

Note 5: Voltage values are with respect to network ground terminal.

Note 6: These parameters must be measured using pulse techniques.  $t_W=$  200  $\mu s$ , duty cycle  $\leq$  2%.

<sup>\*</sup>Derate Cavity Package 10.1 mW/°C above 25°C; derate molded package 11.8 mW/°C above 25°C.

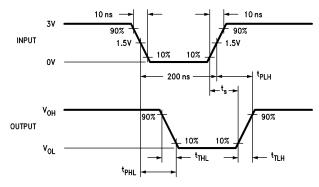

| Symbol               | Parameter                                                | Conditions                                                                          |                                                                         |  | Тур | Max | Units |

|----------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|-----|-----|-------|

| t <sub>PLH</sub>     | Propagation Delay Time, $V_{CC2} = 15V, R_L = 24\Omega,$ |                                                                                     | Source Collectors                                                       |  | 25  | 50  | ns    |

|                      | Low-to-High Level Output                                 | C <sub>L</sub> = 25 pF <i>(Figure 9)</i>                                            | Sink Outputs                                                            |  | 20  | 45  | ns    |

| t <sub>PHL</sub>     | Propagation Delay Time,                                  | $V_{CC2} = 15V, R_L = 24\Omega,$                                                    | Source Collectors                                                       |  | 25  | 50  | ns    |

| High-to-Low Level Ou | High-to-Low Level Output                                 | C <sub>L</sub> = 25 pF <i>(Figure 9)</i>                                            | Sink Outputs                                                            |  | 20  | 45  | ns    |

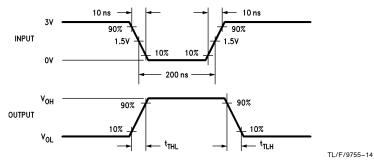

| t <sub>TLH</sub>     | Transition Time,<br>Low-to-High Level Output             | C <sub>L</sub> = 25 pF                                                              | Source Outputs, $V_{CC2} = 20V$ , $R_L = 1 \text{ k}\Omega$ (Figure 10) |  | 55  |     | ns    |

|                      |                                                          |                                                                                     | Sink Outputs, $V_{CC2} = 15V$ , $R_L = 24\Omega$ (Figure 9)             |  | 7   | 15  | ns    |

| t <sub>THL</sub>     | Transition Time,<br>High-to-Low Level Output             | C <sub>L</sub> = 25 pF                                                              | Source Outputs, $V_{CC2} = 20V$ , $R_L = 1 \text{ k}\Omega$ (Figure 10) |  | 7   |     | ns    |

|                      |                                                          |                                                                                     | Sink Outputs, $V_{CC2} = 15V$ , $R_L = 24\Omega$ (Figure 9)             |  | 9   | 20  | ns    |

| ts                   | Storage Time, Sink Outputs                               | Sink Outputs $V_{CC2} = 15V$ , $R_L = 24\Omega$ , $C_L = 25$ pF (Figure 9) 15 30 ns |                                                                         |  |     |     |       |

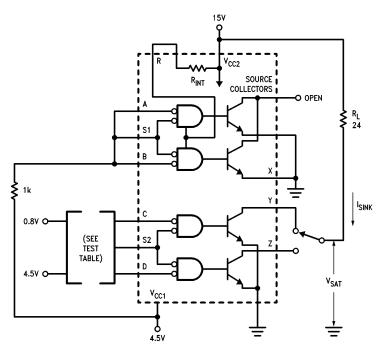

# **DC Test Circuits**

**Test Table**

| C    | D    | S2  | Υ               | Z               |

|------|------|-----|-----------------|-----------------|

| 2V   | 4.5V | GND | V <sub>OH</sub> | OPEN            |

| GND  | 4.5V | 2V  | V <sub>OH</sub> | OPEN            |

| 4.5V | 2V   | GND | OPEN            | V <sub>OH</sub> |

| 4.5V | GND  | 2V  | OPEN            | V <sub>OH</sub> |

Test Table

| Α    | В    | S1   | W    | Х    |

|------|------|------|------|------|

| 0.8V | 4.5V | 0.8V | GND  | OPEN |

| 4.5V | 0.8V | 0.8V | OPEN | GND  |

Note 1: Figure 3 and 4 parameters must be measured using pulse techniques,  $t_W=200~\mu s$ , duty cycle  $\leq 2\%$ .

FIGURE 3.  $V_{IL}$  and Source  $V_{SAT}$

Note 1: Figure 3 and 4 parameters must be measured using pulse techniques,  $t_W=200~\mu s$ , duty cycle  $\leq 2\%$ .

**Test Table**

| С    | D    | S2   | Υ    | z    |

|------|------|------|------|------|

| 0.8V | 4.5V | 0.8V | RL   | OPEN |

| 4.5V | 0.8V | 0.8V | OPEN | Rı   |

FIGURE 4.  $\ensuremath{\text{V}_{\text{IL}}}$  and Sink  $\ensuremath{\text{V}_{\text{SAT}}}$

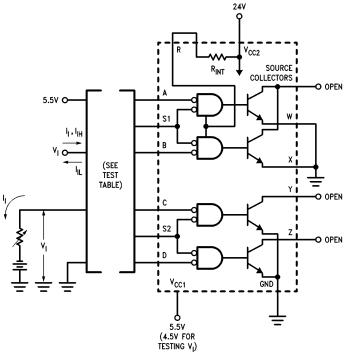

**Test Tables**

TL/F/9755-7

| ١. | Ιн |  |

|----|----|--|

|    |    |  |

|                                                        | -17 -111 |              |  |

|--------------------------------------------------------|----------|--------------|--|

| Apply V <sub>I</sub> = 5.5V<br>Measure I <sub>I</sub>  | Ground   | Apply 5.5V   |  |

| Apply V <sub>I</sub> = 2.4V<br>Measure I <sub>IH</sub> | around   | rippiy old r |  |

| А                                                      | S1       | B, C, S2, D  |  |

| S1                                                     | A, B     | C, S2, D     |  |

| В                                                      | S1       | A, C, S2, D  |  |

| С                                                      | S2       | A, S1, B, D  |  |

| S2                                                     | C, D     | A, S1, B     |  |

| D                                                      | S2       | A, S1, B, C  |  |

$V_{I}, I_{IL}$

| ▼I)·IL                                                 |                 |  |  |  |

|--------------------------------------------------------|-----------------|--|--|--|

| Apply V <sub>I</sub> = 0.4V<br>Measure I <sub>IL</sub> | Apply 5.5V      |  |  |  |

| Apply $I_I = -10 \text{ mA}$<br>Measure $V_I$          |                 |  |  |  |

| А                                                      | S1, B, C, S2, D |  |  |  |

| S1                                                     | A, B, C, S2, D  |  |  |  |

| В                                                      | A, S1, C, S2, D |  |  |  |

| С                                                      | A, S1, B, S2, D |  |  |  |

| S2                                                     | A, S1, B, C, D  |  |  |  |

| D                                                      | A, S1, B, C, S2 |  |  |  |

FIGURE 5.  $V_{l}$ ,  $I_{l}$ ,  $I_{lH}$  and  $I_{lL}$

FIGURE 6. I<sub>CC1 (OFF)</sub> and I<sub>CC2 (OFF)</sub>

TL/F/9755-11

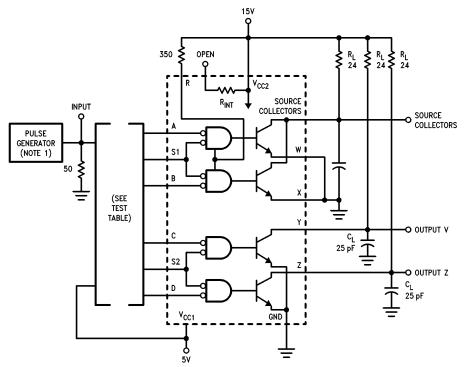

Note 1: The pulse generator has the following characteristics:  $Z_{OUT}=50\Omega,$  duty cycle  $\leq 1\%.$

Note 2: C<sub>L</sub> includes probe and jig capacitance.

# **Voltage Waveforms**

Test Table

| Parameter                             | Output Under Test | Input    | Connect to 5V  |

|---------------------------------------|-------------------|----------|----------------|

| t <sub>PLH</sub> and t <sub>PHL</sub> | Source Collectors | A and S1 | B, C, D and S2 |

|                                       |                   | B and S1 | A, C, D and S2 |

| t <sub>PLH</sub> , t <sub>PHL</sub> , | Sink Output Y     | C and S2 | A, B, D and S1 |

| $t_{TLH}$ , $t_{THL}$ and $t_{S}$     | Sink Output Z     | D and S2 | A. B. C and S1 |

FIGURE 9. Switching Times

# DC Test Circuits (Continued) 20V VCC2 SOURCE COLLECTORS VCC2 SOURCE TEST TABLE) VCC1 SOURCE TEST TABLE) VCC1 SOURCE TEST TABLE) VCC1 SOURCE TEST TABLE) VCC1 SOURCE TEST TABLE) VCC2 SOURCE TEST TABLE) VCC1 SOURCE TEST TABLE) VCC2 SOURCE TEST TABLE) VCC1 SOURCE TEST TABLE TEST TAB

Note 1: The pulse generator has the following characteristics:  $Z_{OUT}=50\Omega$ , duty cycle  $\leq$  1%. Note 2:  $C_L$  includes probe and jig capacitance.

# **Voltage Waveforms**

**Test Table**

| Parameter                             | Output Under Test | Input    | Connect to 5V  |

|---------------------------------------|-------------------|----------|----------------|

| t <sub>TLH</sub> and t <sub>THL</sub> | Source Output W   | A and S1 | B, C, D and S2 |

|                                       | Source Output X   | B and S1 | A, C, D and S2 |

FIGURE 10. Transition Times of Source Outputs

# **Applications**

### **EXTERNAL RESISTOR CALCULATION**

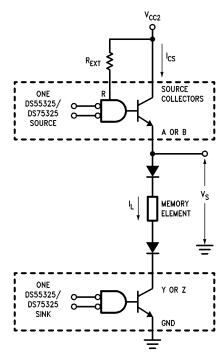

A typical magnetic-memory word drive requirement is shown in *Figure 11*. A source-output transistor of one DS75325 delivers load current ( $I_L$ ). The sink-output transistor of another DS75325 sinks this current.

The value of the external pull-up resistor ( $R_{\text{ext}}$ ) for a particular memory application may be determined using the following equation:

$$R_{ext} = \frac{16 \left[ V_{CC2(Min)} - V_S - 2.2 \right]}{I_L - 1.6 \left[ V_{CC2(Min)} - V_S - 2.9 \right]} \tag{1}$$

where:  $\textbf{R}_{\text{ext}}$  is in  $\textbf{k}\Omega,$

$V_{CC2(Min)}$  is the lowest expected value of  $V_{CC2}$  in volts,  $V_S$  is the source output voltage in volts with respect to ground,  $I_L$  is in mA.

The power dissipated in resistor  $R_{\text{ext}}$  during the load current pulse duration is calculated using Equation 2.

$$P_{\text{Rext}} \approx \frac{I_{\text{L}}}{16} \left[ V_{\text{CC2(Min)}} - V_{\text{S}} - 2 \right]$$

(2)

where: P<sub>Rext</sub> is in mW.

After solving for  $\rm R_{\rm ext},$  the magnitude of the source collector current (I\_CS) is determined from Equation 3.

$$I_{CS} \approx 0.94 I_{L}$$

(3)

where:  $I_{CS}$  is in mA.

As an example, let  $V_{CC2(Min)}=20V$  and  $V_L=3V$  while  $I_L$  of 500 mA flows. Using Equation 1:

$$R_{ext} = \frac{16 \left(20 - 3 - 2.2\right)}{500 - 1.6 \left(20 - 3 - 2.9\right)} = 0.5 \, k\Omega$$

and from Equation 2:

$$P_{\text{Rext}} \approx \frac{500}{16} [20 - 3 - 2] \approx 470 \text{ mW}$$

The amount of the memory system current source (I $_{\mbox{\footnotesize{CS}}})$  from Equation 3 is:

$$I_{\text{CS}} \approx 0.94 \, \text{(500)} \approx 470 \, \text{mA}$$

In this example the regulated source-output transistor base current through the external pull-up resistor (R<sub>ext</sub>) and the source gate is approximately 30 mA. This current and I<sub>CS</sub> comprise I<sub>L</sub>.

TL/F/9755-15

Note 1: For clarity, partial logic diagrams of two DS55325s are shown.

Note 2: Source and sink shown are in different packages.

FIGURE 11. Typical Application Data

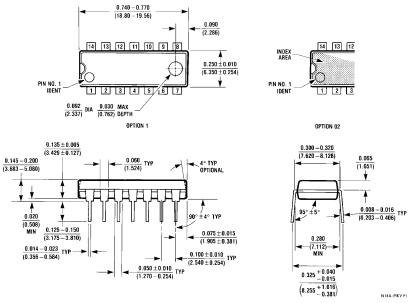

# Physical Dimensions inches (millimeters) (Continued)

### Molded Dual-In-Line Package (N) Order Number DS75325N NS Package Number N14A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408