## Contents

| Page | Section | Title                                   |

|------|---------|-----------------------------------------|

| 4    | 1.      | Introduction                            |

| 4    | 1.1.    | Features                                |

| 4    | 1.2.    | Applications                            |

| 5    | 1.3.    | DVB-T Front-End Application             |

| 6    | 2.      | Functional Description                  |

| 6    | 2.1.    | Analog input                            |

| 6    | 2.2.    | AGC                                     |

| 6    | 2.3.    | Crystal                                 |

| 8    | 2.4.    | Manufacturing Guidelines                |

| 8    | 2.5.    | Lock Indication                         |

| 9    | 2.5.1.  | Host Interface                          |

| 10   | 2.6.    | MPEG2 Output                            |

| 11   | 3.      | Application Programming Interface (API) |

| 11   | 3.1.    | Initialize System Settings              |

| 11   | 3.1.1.  | SP7_LoadMicrocode                       |

| 11   | 3.1.2.  | SP7_LoadImage                           |

| 12   | 3.1.3.  | SP7_SetSamplingMode                     |

| 13   | 3.1.4.  | SP7_SetAGCParams                        |

| 14   | 3.1.5.  | SP7_SetOutputEnable                     |

| 14   | 3.1.6.  | SP7_GetOutputEnable                     |

| 15   | 3.1.7.  | SP7_TSOutput                            |

| 15   | 3.1.8.  | SP7_LCKMode                             |

| 16   | 3.2.    | Setup Signal Parameters                 |

| 16   | 3.2.1.  | SP7_SetChannelParams                    |

| 17   | 3.2.2.  | SP7_GetChannelParams                    |

| 18   | 3.2.3.  | SP7_SetOfdmParams                       |

| 20   | 3.2.4.  | SP7_GetOfdmParams                       |

| 21   | 3.2.5.  | SP7_Start                               |

| 21   | 3.3.    | Selecting Channels                      |

| 21   | 3.3.1.  | SP7_Tune_init                           |

| 22   | 3.3.2.  | SP7_Tune_properties                     |

| 22   | 3.3.3.  | SP7_Tune_program                        |

| 22   | 3.3.4.  | SP7_Tune_error                          |

| 23   | 3.3.5.  | SP7_Tune_get_freq                       |

| 23   | 3.3.6.  | SP7_EnableTunerAccess                   |

| 23   | 3.3.7.  | SP7_LockingStatus                       |

| 24   | 3.4.    | Monitor Channel Quality                 |

| 24   | 3.4.1.  | SP7_GetSN                               |

| 24   | 3.4.2.  | SP7_GetConstellationDiagram             |

| 24   | 3.4.3.  | SP7_GetBer                              |

| 25   | 3.4.4.  | SP7_GetTpsInfo                          |

| 26   | 3.5.    | Commands and other Useful Functions     |

| 26   | 3.5.1.  | SP7_Reboot                              |

| 26   | 3.5.2.  | SP7_Reset                               |

| 26   | 3.5.3.  | SP7_SysReset                            |

## Contents, continued

| Page | Section  | Title                                             |

|------|----------|---------------------------------------------------|

| 26   | 3.5.4.   | SP7_Restart                                       |

| 26   | 3.5.5.   | SP7_Halt                                          |

| 26   | 3.5.6.   | SP7_Nop                                           |

| 26   | 3.5.7.   | SP7_Wreg                                          |

| 26   | 3.5.8.   | SP7_Rreg                                          |

| 27   | 3.5.9.   | SP7_Wvar                                          |

| 27   | 3.5.10.  | SP7_Rvar                                          |

| 27   | 3.6.     | Interrupts and Events                             |

| 27   | 3.6.1.   | SP7_ReadIrq                                       |

| 28   | 3.6.2.   | SP7_PollEvent                                     |

| 29   | 4.       | Specifications                                    |

| 29   | 4.1.     | Outline Dimensions                                |

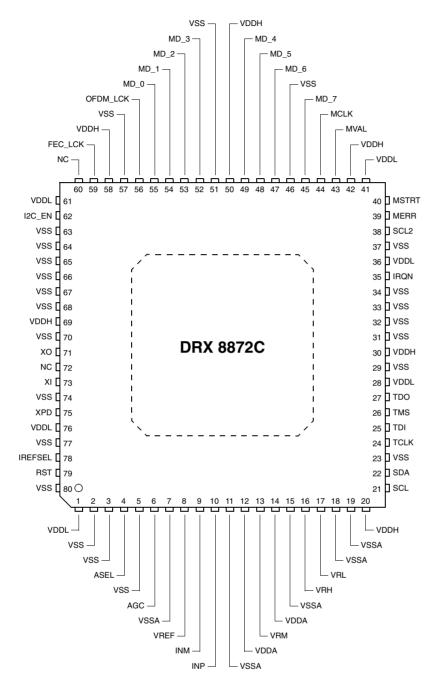

| 30   | 4.2.     | Pin Connections and Short Descriptions            |

| 33   | 4.3.     | Pin Configurations                                |

| 34   | 4.4.     | Electrical Characteristics                        |

| 34   | 4.4.1.   | Absolute Maximum Ratings                          |

| 35   | 4.4.2.   | Recommended Operating Conditions                  |

| 35   | 4.4.2.1. | General Recommended Operating Conditions          |

| 36   | 4.4.3.   | Characteristics                                   |

| 36   | 4.4.3.1. | DC Electrical Characteristics                     |

| 36   | 4.4.3.2. | Temperature Ratings                               |

| 36   | 4.4.3.3. | ADC Parameters                                    |

| 37   | 5.       | Appendix A – API Data Types                       |

| 37   | 5.1.     | Basic Data Types                                  |

| 38   | 5.2.     | Chip-specific Data Types                          |

| 39   | 6.       | Appendix B – API Required Platform Functions      |

| 39   | 6.1.     | PC Platforms Running Windows 98, NT, 2000, and XP |

| 39   | 6.2.     | Other platforms                                   |

| 40   | 6.2.1.   | SP7_I2C_Write                                     |

| 40   | 6.2.2.   | SP7_I2C_Read                                      |

| 41   | 6.2.3.   | l2ctest.c                                         |

| 44   | 7.       | Data Sheet History                                |

## **COFDM Demodulator/FEC**

#### 1. Introduction

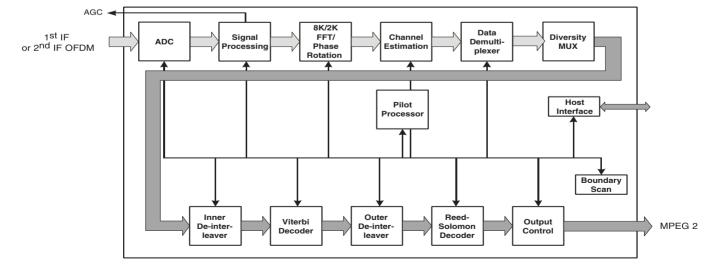

The DRX 8872C is an ETS 300 744-compliant integrated demodulator and forward error corrector (FEC) for DVB-T receivers.

The IC accepts 1<sup>st</sup> and 2<sup>nd</sup> IF COFDM signals as input data. The 1<sup>st</sup> IF sampling option further decreases system cost. The incoming signal is sampled by a highperformance 10-bit A/D converter. The internal microprocessor performs the detection of the COFDM parameters and configuration of the demodulator automatically, without any interaction with the host processor. The error correction unit corrects remaining errors and outputs a DVB-compliant MPEG-2 transport stream.

The DRX 8872C can cope with very severe channel distortions due to its state-of-the-art channel estimation unit.

#### 1.1. Features

- Excellent performance in presence of echoes, cochannel and AWGN

- Integrated microprocessor to perform autonomous operation

- Flexible concept by "micro-coded" algorithms

- Detection of channel type (echoes, co-channel, gaussian noise ...) via channel classificator function

- Very suitable for SFN operation

- Complete software API for smooth integration

- Integrated 10-bit ADC

- 1<sup>st</sup> and 2<sup>nd</sup> IF COFDM supported

- No VCXO required because of digital resampling techniques

- Quick synchronization after channel switch (<70 ms)</li>

- 6 MHz, 7 MHz, and 8 MHz channelcompliant with only one crystal

- Supports all DVB-T modes including hierarchical modulation

- Digital AFC

- BER, S/N, packet error, constellation diagram, lock indication readout

- Serial or parallel MPEG-2 transport stream output

- Supply voltage: 2.5 V (core); 3.3V (I/O)

- Control: via serial bus

- Package: 80-pin PTQFP

- Ambient operating temperature: 0 °C to +70 °C

- IEEE 1149.1 boundary scan

#### 1.2. Applications

- IDTV receivers

- Set-top boxes

- Network Interface Modules (NIMs)

- PC-TV cards

Fig. 1-1: Block diagram of the DRX 8872C

## **1.3. DVB-T Front-End Application**

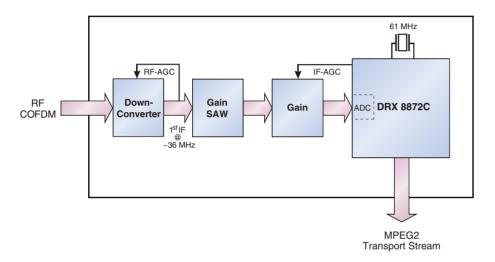

Fig. 1–2 shows a block diagram of a typical DVB-T front-end using the DRX 8872C at the first intermediate frequency. The tuner converts the COFDM signal to a first intermediate frequency of about 36 MHz which is then band-pass-filtered by a SAW filter stage. The SAW filter is followed by a differential-in / differential-out IF amplifier.

This chapter describes in detail how to connect the DRX 8872C in such an application.

Fig. 1-2: Front-end block diagram for the DRX 8872C

## 2. Functional Description

## 2.1. Analog input

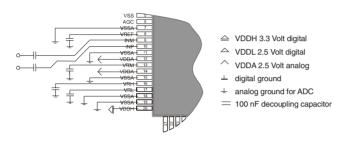

The input signal of the DRX 8872C consists of a  $1^{st}$  or  $2^{nd}$  IF COFDM signal with a bandwidth of 6, 7, or 8 MHz. The input of the demodulator is differential for optimal noise performance. The reference voltages that are needed for the ADC are generated internally. The reference voltages are connected to pins for decoupling reasons.

Fig. 2–1: Input stage application diagram.

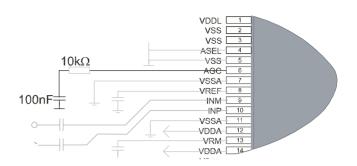

## 2.2. AGC

The DRX 8872C delivers a control signal for an amplifier in the tuner part of the system. The system controller controls a register that is used for a pulse train using a Pulse Width Modulator (PWM) circuit. 256 values can be distinguished. The SP7 SetAGCParams function of the API determines the way this register is controlled. By default, the maximum level is represented by all '1's and the minimum level is represented by all '0's. A low-pass RC filter connected to the AGC pin will filter the PWM signal, generating a stable analog signal for controlling the amplifier of the tuner. The bandwidth of this filter should be small enough to minimize the PWM-jitter on the control signal. The external AGC control is slow compared to the fast internal AGC. A filter bandwidth of 1 kHz is recommended for filtering the PWM-jitter.

Fig. 2-2: AGC application diagram.

For tuners that need voltages other than 0 to 3.3 Volt a buffer connected to 5 Volt could be inserted for generating a higher control voltage.

## 2.3. Crystal

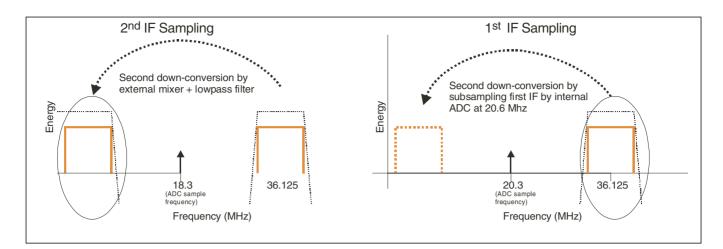

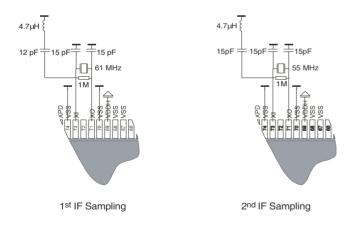

A single crystal operates the DRX 8872C. Sample rate mismatches are corrected completely in the digital domain. The clock generated by the crystal is used as the system clock. A 'divide by three'-block generates the sample clock for the ADC. There are two possible frequencies that can be used by the DRX 8872C. When using the 1<sup>st</sup> IF sampling technique, a 61 MHz crystal should be used. For 2<sup>nd</sup> IF sampling one should select a 55 MHz crystal. The next figure shows why.

Fig. 2–3: 1<sup>st</sup> or 2<sup>nd</sup> IF sampling

The API function SP7\_SetSamplingMode has been defined to set the mode. Default  $1^{st}$  IF sampling is assumed. To generate 55 or 61 MHz, a third overtone crystal must be used. The fundamental tone must be filtered out using an LC network with a time constant defined by:

$$\omega = \frac{1}{\sqrt{LC}}$$

, where  $\omega = \frac{1}{2\pi f}$

with f=61 MHz for 1<sup>st</sup> IF sampling and f=55 MHz for baseband sampling. The application diagram shows the complete crystal circuitry, for example:

# Fig. 2–4: Clocking circuitry for 1<sup>st</sup> IF or baseband sampling

A frequency mismatch of  $\pm 100$  ppm is allowed for the described crystals.

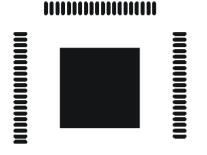

## 2.4. Manufacturing Guidelines

To maximize both the removal of heat from the package and the electrical performance, a land pattern must be incorporated on the PCB within the footprint of the package corresponding to the exposed metal pad on the package, as shown in Fig. 2–5.

##

Fig. 2–5: Top layer solder mask

The dimensions of the PCB pad may be larger or smaller or even a different shape than the exposed metal pad but should have a clearance of at least 0.25 mm between the outer edges of the land pattern and the inner edges of pad pattern for the leads to avoid any shorts.

To improve the thermal dissipation, a thermal via array should be made within the PCB pad area. The vias should be 0.3 mm in diameter at a pitch of between 1.0 and 1.2 mm and preferably with 1 oz copper via barrel plating.

####

####

Fig. 2–6: Thermal via array

For further information regarding the optimal usage of the Micronas exposed-pad QFP please refer to the Application Note "Surface Mount Assembly of Exposed-Pad QFP packages".

## 2.5. Lock Indication

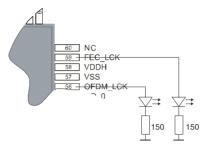

Two hardware lock indicators are available. They can be used for LED control as shown in Fig. 2–7.

Fig. 2–7: Lock indication LEDs

The lock indicator pins FEC\_LCK and OFDM\_LCK can also be put in two other modes:

### SAW filter select

In this mode the two lock signal indicate whether the input signal has a 6, 7, or 8 MHz bandwidth. These pins can than be used directly to switch SAW filters in the tuner accordingly.

#### **User defined**

In this mode the value of the pins can be programmed via software by the host of the system.

The API function SP7\_LCKMode takes care of these settings.

## 2.5.1. Host Interface

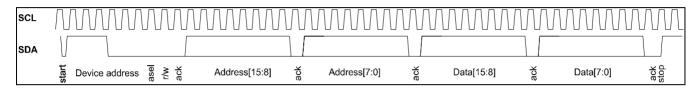

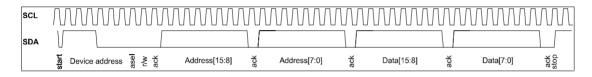

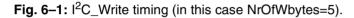

The DRX 8872C communicates via a serial protocol. The DRX 8872C only acts as a slave device. A write access consists of a 'start' followed by the DRX 8872C device address, then the internal register address (2 bytes) and finally the data that needs to be written. During a read-access a repeated start should follow the internal register address definition, after which the data can be read.

**Fig. 2–8:** I2C\_Write timing (NrOfBytes = 2)

Fig. 2-9: I2C\_Read timing (NrOfBytes = 2)

The device address is either "1110000x" if the ASEL pin is tied low or "1110001x" if the ASEL pin is tied high.

## 2.6. MPEG2 Output

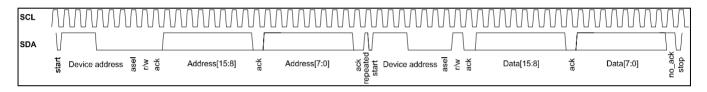

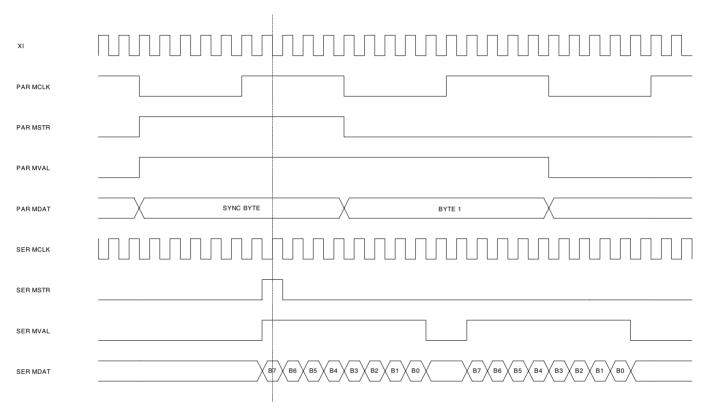

The DRX 8872C has a parallel or serial transport stream output. The system controller adjusts the MPEG2 clock (MCLK) in order to minimize the jitter on the gaps in between packets. The maximum jitter is limited to 20  $\mu$ s. There are several combinations of clock and data formats possible allowing flexible interfacing to MPEG2 decoders. The following figure shows the behavior of the MPEG2 output pins in parallel and serial mode.

The DRX 8872C can output the parity bytes in between two transport stream packages or one can choose to have the transport stream packets output without parity bytes. The API function SP7\_TSOutput lets the user control this. Furthermore, this function can be used to put the MPEG output pins in tristate mode. This can be useful in multistandard STBs where both satellite and terrestrial front-ends are connected to one common interface. No external multiplexer is needed.

Fig. 2–10: MPEG2 TS output timing

## 3. Application Programming Interface (API)

For a description of the types used in the API prototypes, refer to Appendix A in Section 5. on page 37. Most functions in the API return a status (of type Status\_t) that indicates whether the function completed successfully.

The API assumes availability of low-level serial interface functions, as described in Appendix B.

### 3.1. Initialize System Settings

The DRX 8872C integrates a processor. This processor performs the algorithms to synchronize and track the COFDM signal. The algorithms are described in microcode.

There are two versions of the microcode available: A basic version including only the code that will actually be uploaded to the chip and another version including a so-called symbol-table. The basic version is 16 kB and the extended code is about 20 kB. The symbol table includes a memory map of internal processor variables. When monitoring these variables, the symbol table tells the application which address to use. Most applications don't need to monitor the internal processor variables and then one only needs the basic code. In the API distribution, the source code for a tool called "SP7Strip" is included. This tool can strip the symbol table from the microcode as distributed.

After start of the software application, uploading the microcode to the internal processors memory must be the first action. When uploading the originally distributed microcode, one should use the following function.

#### 3.1.1. SP7\_LoadMicrocode

Status\_t SP7\_LoadMicrocode (

);

pu32\_t

pul6 t

mc\_addr, version

| Variable | Туре   | Description                                                                             |  |

|----------|--------|-----------------------------------------------------------------------------------------|--|

| mc_addr  | pu16_t | Memory address of the binary file containing the algorithms for the internal processor. |  |

| version  | pu32_t | Returns version of microcode uploaded.                                                  |  |

For uploading the 'stripped' version, the following function is available.

#### 3.1.2. SP7\_LoadImage

| Status_t | SP7_LoadImage | (  | u16_t  | image_size, |

|----------|---------------|----|--------|-------------|

|          |               |    | pu8_t  | image_addr, |

|          |               |    | pu32_t | version     |

|          |               | ). |        |             |

|          |               | ,, |        |             |

| Variable   | Туре   | Description                                                                                            |

|------------|--------|--------------------------------------------------------------------------------------------------------|

| image_size | u16_t  | Number of bytes to load (typically 16384).                                                             |

| image_addr | pu8_t  | Memory address of the 16 kB stripped binary file containing the algorithms for the internal processor. |

| version    | pu32_t | Returns version of microcode uploaded.                                                                 |

The processor inside the DRX 8872C needs to be given some basic information about the application in order to be able to automatically acquire lock. The first parameter is the sampling mode. The DRX 8872C supports 1st IF sampling as well as base-band sampling. All one needs to do is tell the processor which system clock frequency (crystal) and which input signal frequency - generally 36.125 MHz for 1st IF or 4.57 MHz for baseband sampling - is used. In combination with knowledge about whether the signal is mirrored or not, the chip will automatically calculate the correct settings for the internal sample-rate correction filters. The digital timing recovery enables the system to acquire lock when the system clock is within 500 ppm of the preprogrammed value.

#### 3.1.3. SP7\_SetSamplingMode

SP7\_SetSamplingMode ( Status\_t

);

u16\_t

u16\_t

SystemClockFrequency, SigInputFrequency, Mirror\_t SigInputMirror

| Variable             | Туре     | Description                                                                                                                                                                                                                                     |

|----------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SystemClockFrequency | u16_t    | Frequency of the crystal applied to the DRX 8872C, in kHz (e.g. set to 61000 when using a 61-MHz crystal).                                                                                                                                      |

| SigInputFrequency    | u16_t    | 16 bit integer number representing the center frequency of the COFDM signal that is applied to the DRX 8872C, in kHz (e.g. set to 36125 for 1 <sup>st</sup> IF sampling).                                                                       |

| SigInputMirror       | Mirror_t | In case the input signal to the DRX 8872C is mirrored, depending on the number of down-conversion stages in the system, this can be indicated using this flag. The DRX 8872C will adjust automatic frequency correction algorithms accordingly. |

Depending on the tuner one uses, it is either preferred to have a slow AGC control or a fast feedback to changes on the incoming energy level. The type of control can be selected using the AGC control variable in the next API function.

When not controlled by the internal processor, it is possible to adjust the level of the amplifier stages by changing the AGC-level variables as described in the next function.

## 3.1.4. SP7\_SetAGCParams

| Status_t | SP7_SetAGCParams | (  | AGC_t  | AGC_ctrl,       |

|----------|------------------|----|--------|-----------------|

|          |                  |    | Bool_t | AGC_SelectPin2, |

|          |                  |    | u16_t  | AGC_level1,     |

|          |                  |    | u16_t  | AGC_level2,     |

|          |                  |    | u16_t  | AGC_level3      |

|          |                  | ); |        |                 |

| Variable       | Туре   | Description                                                                                                                                                                                                                                                                                |

|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGC_ctrl       | AGC_t  | Variable indicating type of control.                                                                                                                                                                                                                                                       |

|                |        | AGC_OFF<br>No control, the default levels will be applied.                                                                                                                                                                                                                                 |

|                |        | AGC_FAST<br>Fast reaction to changes in energy level. In this mode the chip uses a hardwired AGC<br>control function.                                                                                                                                                                      |

|                |        | AGC_SLOW<br>Instead of the hardwired AGC functionality the internal processor controls the incoming<br>energy level on symbol basis.                                                                                                                                                       |

|                |        | AGC_INV<br>By default, a positive control is used. With this setting this can be changed into a negative<br>control. This is only possible in combination with AGC_SLOW. If one wants to negate the<br>control in combination with AGC_FAST, one must use an external inverting component. |

| AGC_SelectPin2 | Bool_t | If TRUE, AGC is applied to the secondary PWM output (only DRX8872P).                                                                                                                                                                                                                       |

| AGC_level1     | u16_t  | Unsigned integer indicating the default level of AGC1 when no control is applied to it.                                                                                                                                                                                                    |

| AGC_level2     | u16_t  | Unsigned integer indicating the default level of AGC2 when no control is applied to it.                                                                                                                                                                                                    |

| AGC_level3     | u16_t  | Unsigned integer indicating the default level of AGC3 when no control is applied to it.                                                                                                                                                                                                    |

Upon power-on reset, all output pins are tri-stated to allow other demodulators (e.g. satellite or cable) to drive the TS signals. The output pins must be put in output mode using the following API function. The monitor-bus with real-time channel information is only available with the professional version.

#### 3.1.5. SP7\_SetOutputEnable

Status\_t SP7\_SetOutputEnable (

);

Bool\_t

Bool\_t

Bool\_t

MpegTS, MonitorBus, InterfacePins

| Variable      | Туре   | Description                                                                                        |

|---------------|--------|----------------------------------------------------------------------------------------------------|

| MpegTS        | Bool_t | Boolean indicating MPEG TS pin driver state.                                                       |

|               |        | FALSE<br>MPEG TS pins are tristated (default).                                                     |

|               |        | TRUE<br>MPEG TS pins are put in output mode.                                                       |

| MonitorBus    | Bool_t | Boolean indicating Monitor bus pin driver state (MT8872P only).                                    |

|               |        | FALSE<br>Monitor bus pins are tristated (default).                                                 |

|               |        | TRUE<br>Monitor bus pins are put in output mode.                                                   |

| InterfacePins | Bool_t | Boolean indicating pin driver state of OFDM_LCK, FEC_LCK, I2C2_EN, IRQN and SCL2 (DRX 8872C only). |

|               |        | FALSE<br>Pins are tristated.                                                                       |

|               |        | TRUE<br>Pins are put in output mode.                                                               |

The actual mode of the pins can be obtained using the following function.

#### 3.1.6. SP7\_GetOutputEnable

Status\_t SP7\_GetOutputEnable (

ole ( p p p );

pBool\_t MpegTS, pBool\_t MonitorBus, pBool\_t InterfacePins

| Variable      | Туре    | Description                                                                                        |

|---------------|---------|----------------------------------------------------------------------------------------------------|

| MpegTS        | pBool_t | Boolean indicating MPEG TS pin driver state.                                                       |

|               |         | FALSE<br>MPEG TS pins are tristated (default).                                                     |

|               |         | TRUE<br>MPEG TS pins are in output mode.                                                           |

| MonitorBus    | pBool_t | Boolean indicating Monitor bus pin driver state (MT8872P only).                                    |

|               |         | FALSE<br>Monitor bus pins are tristated (default).                                                 |

|               |         | TRUE<br>Monitor bus pins are in output mode.                                                       |

| InterfacePins | pBool_t | Boolean indicating pin driver state of OFDM_LCK, FEC_LCK, I2C2_EN, IRQN and SCL2 (DRX 8872C only). |

|               |         | FALSE<br>Pins are tristated.                                                                       |

|               |         | TRUE<br>Pins are in output mode.                                                                   |

The MPEG Transport Stream interface clocking can be configured. When no valid data bytes are output (the parity bytes in between two packets or during the remaining gap in the guard interval) the MCLK pin can either be disabled or a continuous clock can be chosen. When using the continuous clock the MVAL signal can be used to indicate non-valid data.

#### 3.1.7. SP7\_TSOutput

| <br>SP7_TSOutput | (  | Bool_t<br>Bool_t | Parity,<br>SuppressClock |  |

|------------------|----|------------------|--------------------------|--|

|                  | ); |                  |                          |  |

| Variable      | Туре   | Description                                                                                                                        |

|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------|

| Parity        | Bool_t | If TRUE, The Reed Solomon parity bytes will be output in between two transport stream packets.                                     |

| SuppressClock | Bool_t | If TRUE, the MCLK pin is suppressed when no valid data is output (parity bytes and gaps between packets or during guard interval). |

The last pins that can be configured are the OFDM\_LCK and the FEC\_LCK pins.

#### 3.1.8. SP7\_LCKMode

Status\_t SP7\_LCKMode

#### ( LCK\_t LCK\_t );

OFDM\_LCK\_Ctrl, FEC\_LCK\_Ctrl

| Variable      | Туре  | Description                                                                                                                                  |

|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| OFDM_LCK_Ctrl | LCK_t | Parameter indicating use of the OFDM LCK pin.                                                                                                |

|               |       | LCK_INDICATOR<br>The OFDM_LCK pin reflects the locking state of the COFDM demodulator part of<br>the chip.                                   |

|               |       | LCK_SAW_8<br>The OFDM_LCK pin will go high if an 8 MHz SAW filter must be selected, otherwise<br>(for 7 or 6 MHz bandwidths) it will be low. |

|               |       | LCK_SAW_7<br>The OFDM_LCK pin will go high if an 7 or 8 MHz SAW filter must be selected,<br>otherwise (for 6 MHz bandwidths) it will be low. |

|               |       | LCK_UIO_0<br>The OFDM_LCK pin will be always low.                                                                                            |

|               |       | LCK_UIO_1<br>The OFDM_LCK pin will be always high.                                                                                           |

| FEC_LCK_Ctrl  | LCK_t | Parameter indicating use of the FEC LCK pin.                                                                                                 |

|               |       | LCK_INDICATOR<br>The FEC_LCK pin reflects the locking state of the FEC error correction part of the<br>chip.                                 |

|               |       | LCK_SAW_8<br>The FEC_LCK pin will be high if an 8 MHz SAW filter must be selected, otherwise<br>(for 7 or 6 MHz bandwidths) it will be low.  |

|               |       | LCK_SAW_7<br>The FEC_LCK pin will go high if an 7 or 8 MHz SAW filter must be selected,<br>otherwise (for 6 MHz bandwidths) it will be low.  |

|               |       | LCK_UIO_0<br>The FEC_LCK pin will be always low.                                                                                             |

|               |       | LCK_UIO_1<br>The FEC_LCK pin will be always high.                                                                                            |

For function *SP7\_LCKMode* to work correctly, the OFDM\_LCK and FEC\_LCK pins must have been configured for output, by using the function *SP7\_SetOutputEnable*.

and

SP7\_GetChannelParams

SP7 SetChannelParams relate to channel parameters

like frequency offsets and signal bandwidth. The

SP7\_GetOfdmParams and SP7\_SetOfdmParams

functions relate to the COFDM symbol parameters like

code rate, FFT size etc. The parameters that are set

up with these functions are not programmed until the

chip is started using the SP7\_Start function.

## 3.2. Setup Signal Parameters

All hardware related parameters have been set now. The next step is to configure the system for the incoming signal. In the application one can either let the DRX 8872C detect all settings automatically or one can choose to pre-program some parameters in case they are known. This can improve locking speed. The

3.2.1. SP7\_SetChannelParams

Status\_t SP7\_SetC

SP7\_SetChannelParams ( s16

);

| s16_t       | SysFrequencyOffset |

|-------------|--------------------|

| s16_t       | SigFrequencyOffset |

| Bandwidth_t | SigBandwidth,      |

| Mirror_t    | SigMirror,         |

| Cls_t       | SigClass           |

|             |                    |

functions

| Variable           | Туре        | Description                                                                                                                                                                                                                                                                            |

|--------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SysFrequencyOffset | s16_t       | Signed integer number indicating the known system clock frequency mismatch in kHz, relative to the value that was set with <i>SP7_SetSamplingMode</i> .                                                                                                                                |

| SigFrequencyOffset | s16_t       | Signed integer number indicating the known signal frequency mismatch in kHz. If unknown, set to zero.                                                                                                                                                                                  |

| SigBandwidth       | Bandwidth_t | The bandwidth can be programmed.<br>BANDWIDTH_6MHZ<br>6 MHz Channel.<br>BANDWIDTH_7MHZ<br>7 MHz Channel.<br>BANDWIDTH_8MHZ<br>8 MHz Channel (default).                                                                                                                                 |

| SigMirror          | Mirror_t    | This parameter indicates whether the spectrum is mirrored.<br>MIRRORED<br>Spectrum is mirrored.<br>NORMAL<br>Spectrum is normal.<br>AUTO<br>Detect automatically.                                                                                                                      |

| SigClass           | Cls_t       | This parameter sets the channel classification.<br>CLS_GAUSS<br>Gaussian noise.<br>CLS_HEAVYGAUSS<br>Heavy Gaussian noise.<br>CLS_COCHANNEL<br>Co-channel.<br>CLS_STATIC<br>Static echo.<br>CLS_MOVING<br>Moving echo.<br>CLS_ZERODB<br>Zero dB echo.<br>AUTO<br>Detect automatically. |

Next to programming the values, the measured values can be obtained from the system.

## 3.2.2. SP7\_GetChannelParams

| Status_t | SP7_GetChannelParams(        |

|----------|------------------------------|

| bcacab_c | bi /_decentarineri ar anab ( |

);

| ps16_t     | SysFrequencyOffset, |

|------------|---------------------|

| ps16_t     | SigFrequencyOffset, |

| pBandwidth | _tSigBandwidth,     |

| pMirror_t  | SigMirror,          |

| pCls_t     | SigClass            |

|            |                     |

| Variable           | Туре         | Description                                                                                                                                                 |

|--------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SysFrequencyOffset | ps16_t       | Signed integer number indicating the system clock frequency mismatch in kHz, relative to the value that was set with <i>SP7_SetSamplingMode</i> .           |

| FrequencyOffset    | ps16_t       | Signed integer number indicating the signal frequency mismatch in kHz. Depending on the step-size of the tuner, the mismatch can be minimized by re-tuning. |

| SigBandwidth       | pBandwidth_t | The bandwidth is reported. This returns either a default value or the value that was set by a previous call of SP7_SetChannelParams.                        |

|                    |              | BANDWIDTH_6MHZ<br>6 MHz Channel.                                                                                                                            |

|                    |              | BANDWIDTH_7MHZ<br>7 MHz Channel.                                                                                                                            |

|                    |              | BANDWIDTH_8MHZ<br>8 MHz Channel.                                                                                                                            |

| SigMirror          | pMirror_t    | This parameter indicates whether the spectrum is mirrored.                                                                                                  |

|                    |              | MIRRORED<br>Spectrum is mirrored.                                                                                                                           |

|                    |              | NORMAL<br>Spectrum is normal.                                                                                                                               |

| SigClass           | pCls_t       | The channel classification is reported.                                                                                                                     |

|                    |              | CLS_GAUSS<br>Gaussian noise.                                                                                                                                |

|                    |              | CLS_HEAVYGAUSS<br>Heavy Gaussian noise.                                                                                                                     |

|                    |              | CLS_COCHANNEL<br>Co-channel.                                                                                                                                |

|                    |              | CLS_STATIC<br>Static echo.                                                                                                                                  |

|                    |              | CLS_MOVING<br>Moving echo.                                                                                                                                  |

|                    |              | CLS_ZERODB<br>Zero dB echo.                                                                                                                                 |

The mode of the COFDM signal path is being transmitted using the TPS carriers can be detected automatically. The information can be obtained by using the *SP7\_GetOfdmParams* function and the system can be told to use a specific mode using the *SP7\_SetOfdmParams* API function.

(

);

#### 3.2.3. SP7\_SetOfdmParams

Status\_t SP7\_SetOfdmParams

| Mode_t  | Mode,          |

|---------|----------------|

| Guard_t | Guard,         |

| Const_t | Constellation, |

| Hier_t  | Hierarchy,     |

| Prior_t | Priority,      |

| Rate_t  | CodeRate       |

|         |                |

| Variable      | Туре    | Description                                                  |

|---------------|---------|--------------------------------------------------------------|

| Mode          | Mode_t  | MODE_2K<br>8k Mode.<br>MODE_8K<br>2k Mode.<br>AUTO           |

|               |         | Detect automatically.                                        |

| Guard         | Guard_t | GUARD_32<br>1/32nd Guard interval.                           |

|               |         | GUARD_16<br>1/16th Guard interval.                           |

|               |         | GUARD_8<br>1/8th Guard interval.                             |

|               |         | GUARD_4<br>1/4th Guard interval.                             |

|               |         | AUTO<br>Detect automatically.                                |

| Constellation | Const_t | CONST_QPSK<br>QPSK constellation.                            |

|               |         | CONST_QAM16<br>QAM16 constellation.                          |

|               |         | CONST_QAM64<br>QAM64 constellation.                          |

|               |         | AUTO<br>Detect automatically.                                |

| Hierarchy     | Hier_t  | HIER_NONHIER<br>No hierarchical transmission.                |

|               |         | HIER_ALPHA_1<br>Hierarchical transmission, $\alpha$ is one.  |

|               |         | HIER_ALPHA_2<br>Hierarchical transmission, $\alpha$ is two.  |

|               |         | HIER_ALPHA_4<br>Hierarchical transmission, $\alpha$ is four. |

|               |         | AUTO<br>Detect automatically.                                |

| Variable | Туре    | Description                                                         |

|----------|---------|---------------------------------------------------------------------|

| Priority | Prior_t | In case of hierarchical transmission:<br>PRIOR_LOW<br>Low priority. |

|          |         | PRIOR_HIGH<br>High priority.                                        |

| CodeRate | Rate_t  | RATE_1_2<br>Code rate 1/2nd.                                        |

|          |         | RATE_2_3<br>Code rate 2/3rd.                                        |

|          |         | RATE_3_4<br>Code rate 3/4th.                                        |

|          |         | RATE_5_6<br>Code rate 5/6th.                                        |

|          |         | RATE_7_8<br>Code rate 7/8th.                                        |

|          |         | AUTO<br>Detect automatically.                                       |

## 3.2.4. SP7\_GetOfdmParams

| Status_t | SP7_GetOfdmParams | ( |

|----------|-------------------|---|

| (  | pMode_t  | Mode,          |

|----|----------|----------------|

|    | pGuard_t | Guard,         |

|    | pConst_t | Constellation, |

|    | pHier_t  | Hierarchy,     |

|    | pPrior_t | Priority,      |

|    | pRate_t  | CodeRate       |

| ); |          |                |

| Variable      | Туре     | Description                                                 |

|---------------|----------|-------------------------------------------------------------|

| Mode          | pMode_t  | MODE_2K<br>8k Mode.                                         |

|               |          | MODE_8K<br>2k Mode.                                         |

| Guard         | pGuard_t | GUARD_32<br>1/32nd Guard interval.                          |

|               |          | GUARD_16<br>1/16th Guard interval.                          |

|               |          | GUARD_8<br>1/8th Guard interval.                            |

|               |          | GUARD_4<br>1/4th Guard interval.                            |

| Constellation | pConst_t | CONST_QPSK<br>QPSK constellation.                           |

|               |          | CONST_QAM16<br>QAM16 constellation.                         |

|               |          | CONST_QAM64<br>QAM64 constellation.                         |

| Hierarchy     | pHier_t  | HIER_NONHIER<br>No hierarchical transmission.               |

|               |          | HIER_ALPHA_1<br>Hierarchical transmission, $\alpha$ is one. |

|               |          | HIER_ALPHA_2<br>Hierarchical transmission, $\alpha$ is two. |

|               |          | HIER_ALPHA_4 Hierarchical transmission, $\alpha$ is four.   |

| Priority      | pPrior_t | In case of hierarchical transmission:                       |

|               |          | PRIOR_LOW<br>Low priority.                                  |

|               |          | PRIOR_HIGH<br>High priority.                                |

| CodeRate      | pRate_t  | RATE_1_2<br>Code rate 1/2nd.                                |

|               |          | RATE_2_3<br>Code rate 2/3rd.                                |

|               |          | RATE_3_4<br>Code rate 3/4th.                                |

|               |          | RATE_5_6<br>Code rate 5/6th.                                |

|               |          | RATE_7_8<br>Code rate 7/8th.                                |

The processor now knows all it needs to know and one can start to acquire lock.

The *SP7\_Start* function will start the internal processor and the demodulation process will start, making use of the settings that were applied using the previously described API functions.

#### 3.2.5. SP7\_Start

Status\_t SP7\_Start ( void );

If an COFDM signal is applied to the input of the DRX 8872C, the system will start to acquire lock.

#### 3.3. Selecting Channels

In order to get a correct COFDM signal, the tuner in front of the demodulator must be programmed to the right frequency. The DRX 8872C has been tested in combination with many tuners. Each tuner has its own specifications. The frequency range, step-size and charge pump settings vary per tuner. Also the optimal AGC setting can be different per tuner type. To ease the work of the customers some API functions have been made available. When using one of the tested tuner types the optimal settings will automatically be chosen.

To initialize the API with the settings of the tuner that is currently in use, first the *SP7\_Tune\_init* function should be called.

## 3.3.1. SP7\_Tune\_init

Status\_t SP7\_Tune\_init ( u16\_t tune\_type );

| Variable  | Туре  | Description                                                                                 |

|-----------|-------|---------------------------------------------------------------------------------------------|

| tune_type | u16_t | Variable indicating which tuner is used. Refer to source code for list of tuners supported. |

The function *SP7\_Tune\_properties* can be called to retrieve the parameters of the tuner that is used (if known by the API). The output of this function can be used when setting up the system. In this case the user

does not have to worry about whether the tuner outputs its signal at 1<sup>st</sup> or 2<sup>nd</sup> IF, whether the signal is mirrored or not and what the preferred AGC settings should be.

#### 3.3.2. SP7\_Tune\_properties

| Status_t | SP7_Tune_properties | ( | pu8_t*    | Name,            |

|----------|---------------------|---|-----------|------------------|

|          |                     |   | pu32_t    | FrequencyMin,    |

|          |                     |   | pu32_t    | FrequencyMax,    |

|          |                     |   | pu16_t    | FrequencyStep,   |

|          |                     |   | pu16_t    | FrequencyOut,    |

|          |                     |   | pMirror_t | FrequencyMirror, |

|          |                     |   | pAGC_t    | AgcType,         |

|          |                     |   | pu16_t    | Agc_level3       |

);

| Variable        | Туре      | Description                                                                                                                                                      |

|-----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | pu8_t*    | Returns the name of the tuner. Only relevant when more than one tuner is taken into account during compilation, for instance in applications like Signal Spyder. |

| FrequencyMin    | pu32_t    | Minimum available frequency for this tuner, in kHz.                                                                                                              |

| FrequencyMax    | pu32_t    | Maximum supported frequency for this tuner, in kHz.                                                                                                              |

| FrequencyStep   | pu16_t    | RF frequency step-size for this tuner.                                                                                                                           |

| FrequencyOut    | pu16_t    | Output frequency of this tuner.                                                                                                                                  |

| FrequencyMirror | pMirror_t | Variable indicating whether the output of this tuner is mirrored or not.                                                                                         |

| АдсТуре         | pAGC_t    | Variable indicating the preferred AGC setting for the tuner currently used.                                                                                      |

| AGC_level3      | pu16_t    | Integer value indicating the optimum PGA level in combination with the tuner currently used.                                                                     |

Next to acquiring information related to the type of tuner used, the API supports functions that will actually program the tuner to the desired frequency with the appropriate settings.

#### 3.3.3. SP7\_Tune\_program

```

Status_t SP7_Tune_program ( u32_t F );

```

| Variable | Туре  | Description                                                |

|----------|-------|------------------------------------------------------------|

| F        | u32_t | Frequency to which the tuner should be programmed, in kHz. |

In case communication with the tuner fails, the exact error status can be read back using the following function.

#### 3.3.4. SP7\_Tune\_error

ul6\_t SP7\_Tune\_error ( void );

Returns number that represents an error code.

Since the tuner has a finite step-size it will not be possible to exactly program the tuner to the desired frequency. The next function reports the frequency to which the tuner was actually programmed.

#### 3.3.5. SP7\_Tune\_get\_freq

u32\_t SP7\_Tune\_get\_freq ( void );

Returns exact frequency to which the tuner was programmed, in kHz.

When not using the given tuner programming functions, one needs to calculate the tuner settings and generate the command string (5 bytes) using the tuner specification. The DRX 8872C supports a gated clockline to the tuner. This means that the tuner is not connected directly to the serial bus but via the demodulator and an external analog switch. If connected in this way, the serial lines towards the tuner can be kept quiet during normal operation to minimize noise on the PLL inside the tuner. To select a channel first the connection to the tuner must be enabled, then the tuner specific settings must be applied (5  $I^2C$  byte accesses), and finally the connection to the tuner can be closed again. The following API function has been defined for opening and closing this port.

#### 3.3.6. SP7\_EnableTunerAccess

| Status_t SP7_Enabl | eTunerAccess( Bool_t | <pre>TunerAccess );</pre> |

|--------------------|----------------------|---------------------------|

|--------------------|----------------------|---------------------------|

| Variable    | Туре   | Description                                                               |

|-------------|--------|---------------------------------------------------------------------------|

| TunerAccess | Bool_t | If TRUE, the secondary protocol port is opened for programming the tuner. |

After programming the tuner, the chip will start to acquire lock. It is of course important to know whether

the chip has acquired lock. For this purpose the *SP7\_LockingStatus* function has been defined.

#### 3.3.7. SP7\_LockingStatus

```

Status_t SP7_LockingStatus ( pBool_t Locked );

```

| Variable | Туре    | Description                      |

|----------|---------|----------------------------------|

| Locked   | pBool_t | If TRUE, chip has acquired lock. |

## 3.4. Monitor Channel Quality

The channel estimator unit of the DRX 8872C performs a signal to noise measurement on the constellation diagram. The output of this calculation can be

) :

#### 3.4.1. SP7\_GetSN

Status\_t SP7\_GetSN ( pu16\_t pu16\_t

SN, MER

| Variable | Туре   | Description                                                                                                   |

|----------|--------|---------------------------------------------------------------------------------------------------------------|

| SN       | pu16_t | Integer number indicating the S/N ratio detected at the input of the demapper, in steps of $1/10$ th of a dB. |

| MER      | pu16_t | Integer number indicating the MER, in steps of 1/10th of a dB.                                                |

The S/N ratio gives a very good indication of the channel quality, independent of the mode of the signal. For a graphical feedback one can use the constellation diagram. A slow non-real-time diagram can be built using the following function.

retrieved using the API function *SP7\_GetSN*. From this measurement, a MER is also derived. The MER is cal-

culated using the deviation of the continual pilots and

is therefore an indication, not an exact value.

#### 3.4.2. SP7\_GetConstellationDiagram

| Status_t | SP7_GetConstellationD | iagram ( |       |

|----------|-----------------------|----------|-------|

|          |                       | ps16_t   | Real, |

|          |                       | ps16_t   | Imag  |

|          | )                     | ;        |       |

| Variable | Туре   | Description                                                                                                                                                             |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real     | ps16_t | Real part of the constellation point. The values 256/-256 correspond to the energy level of the pilots of the COFDM symbol. The maximum values range from –512 to +511. |

| Imag     | ps16_t | Imaginary part of the constellation point.                                                                                                                              |

A more common way to give an indication of the signal quality is to look at the BER values. This also allows

for comparison of the quality of the DRX 8872C to the ETS300744 DVB-T standard.

#### 3.4.3. SP7\_GetBer

Status\_t GetBer

( pu32\_t pu32\_t pu32\_t); PreViterbi, PostViterbi, PacketError

| Variable    | Туре   | Description                                                                                                            |

|-------------|--------|------------------------------------------------------------------------------------------------------------------------|

| PreViterbi  | pu32_t | Bit error rate (BER) before error correction, with a scale of 1e-6.                                                    |

| PostViterbi | pu32_t | BER after Viterbi decoder, with a scale of 1e-6. A value of 200 corresponds to a BER of 2e-4, the so-called QEF level. |

| PacketError | pu16_t | Counter indicating the number of packet errors after Reed Solomon decoding.                                            |

Next to using the previously described function *SP7\_GetOfdmParams* to obtain information on the incoming COFDM signal, the TPS information contained in the COFDM signal can be read using the following API function.

## 3.4.4. SP7\_GetTpsInfo

| Status_t | SP7_GetTpsInfo | (  | pMode_t     | TpsMode,          |

|----------|----------------|----|-------------|-------------------|

|          |                |    | pGuard_t    | TpsGuard,         |

|          |                |    | pConst_t    | TpsConstellation, |

|          |                |    | pHier_t     | TpsHierarchy,     |

|          |                |    | pRate_t     | TpsHiRate,        |

|          |                |    | pRate_t     | TpsLoRate,        |

|          |                |    | pTpsFrame_t | TpsFrame,         |

|          |                |    | pu8_t       | TpsLength,        |

|          |                |    | pBool_t     | TpsCellIdRdy,     |

|          |                |    | pu16_t      | TpsCellId         |

|          |                | ); |             |                   |

| Variable              | Туре            | Description                                                      |

|-----------------------|-----------------|------------------------------------------------------------------|

| TPSMode               | pMode_t         | Variable indicating the mode as described in the TPS parameters. |

| TpsGuard              | pGuard_t        | Guard interval length as described in the TPS parameters.        |

| TpsConstella-<br>tion | pConst_t        | Constellation diagram depth as described in the TPS parameters.  |

| TpsHierarchy          | pHier_t         | Level of Hierarchy as described in the TPS parameters.           |

| TpsHiRate             | pRate_t         | High priority code rate.                                         |

| TpsLoRate             | pRate_t         | Low priority code rate.                                          |

| TpsFrame              | pTpsFrame_<br>t | Frame number.                                                    |

| TpsLength             | pu8_t           | Integer number indicating the length of the TPS Frame.           |

| TpsCellIdRdy          | pBool_t         | Flag indicating that the returned TpsCellId is valid.            |

| TpsCellId             | pu16_t          | 16-Bit received Cell identifier.                                 |

#### 3.5. Commands and other Useful Functions

Next to the application specific function as described in the previous paragraphs, also some low level functions are available. Other API functions also make use of these low-level functions themselves.

#### 3.5.1. SP7\_Reboot

Status\_t SP7\_Reboot ( void );

Reinstall all register settings, which were stored during the first start-up, and reload all default algorithm constants. Starts demodulator.

#### 3.5.2. SP7\_Reset

Status\_t SP7\_Reset (void);

Reinstalls all register settings, does not reinitialize algorithm constants, such that user patches remain active. Restarts algorithm.

#### 3.5.3. SP7\_SysReset

Status\_t SP7\_SysReset (void);

First resets all internal hardware, then behaves like *SP7\_Reset*.

#### 3.5.7. SP7\_Wreg

| Status_t | SP7_Wreg | (   | u16_t | Reg, |

|----------|----------|-----|-------|------|

|          |          |     | u16_t | Data |

|          |          | ) • |       |      |

| Variable | Туре  | Description                                   |  |

|----------|-------|-----------------------------------------------|--|

| Reg      | u16_t | Address of register that needs to be written. |  |

| Data     | u16_t | New value for the register.                   |  |

### 3.5.8. SP7\_Rreg

Status\_t SP7\_Rreg

( u16\_t

pu16\_t

);

Reg, Data

| Variable | Туре   | Description                                |  |

|----------|--------|--------------------------------------------|--|

| Reg      | u16_t  | Address of register that needs to be read. |  |

| Data     | pu16_t | Returns value of the register.             |  |

#### 3.5.4. SP7 Restart

Status\_t SP7\_Restart

( void );

Just restart algorithm, with current register settings and algorithm constants.

#### 3.5.5. SP7\_Halt

Status\_t SP7\_Halt

( void );

Halts the current state of the DRX 8872C. This is a useful function when debugging your application. The DRX 8872C remains executing commands.

#### 3.5.6. SP7\_Nop

Status\_t SP7\_Nop (void);

Do nothing, but generate an interrupt on completion.

The next two functions enable different algorithm constants to be programmed to influence the behavior of the algorithm. Also the state of all microcode variables can be queried. Reading and writing microcode variables is done "atomically".

#### 3.5.9. SP7\_Wvar

| Status_t | SP7_Wvar | (  | u16_t  | Adr,  |

|----------|----------|----|--------|-------|

|          |          |    | u16_t  | Wnr,  |

|          |          |    | pu16_t | Wdata |

|          |          | ); |        |       |

| Variable | Туре   | Description                                               |  |

|----------|--------|-----------------------------------------------------------|--|

| Adr      | u16_t  | Address of (processor) variable that needs to be written. |  |

| Wnr      | u16_t  | Number of words that must be written.                     |  |

| Wdata    | pu16_t | New value for the variable (array).                       |  |

### 3.5.10.SP7\_Rvar

Status\_t SP7\_Rvar

| (  | u16_t  | Adr,  |

|----|--------|-------|

|    | u16_t  | Rnr,  |

|    | pu16_t | Rdata |

| ); |        |       |

| Variable | Туре   | Description                                            |  |

|----------|--------|--------------------------------------------------------|--|

| Adr      | u16_t  | Address of (processor) variable that needs to be read. |  |

| Rnr      | u16_t  | Number of words that must be read.                     |  |

| Rdata    | pu16_t | Returns value of the variable (array).                 |  |

## 3.6. Interrupts and Events

The DRX 8872C has an IRQN output which can generate an interrupt to the host to trigger an event. Two types of interrupts are reported back to the host: "Command Completion" interrupt, and "Algorithm Event" interrupt. The API uses the "Command Completion" interrupt internally. The "Algorithm Event" interrupt is of special interest to the application.

#### 3.6.1. SP7\_ReadIrq

Status\_t SP7\_ReadIrq ( void );

Reads the interrupt status register, such that new interrupts may occur.

On any occasion, the event register may be read to see if the DRX 8872C algorithm generated an event. If an event occurs, an interrupt is also generated. Thus if the interrupt line is used, it makes sense to only read the event register on an interrupt.

#### 3.6.2. SP7\_PollEvent

Status\_t

SP7\_PollEvent

OccurredEvents );

Reads the event register and sets bits in OccurredEvents according to the events that occurred since the last read.

(

pu16\_t

| Variable       | Туре   | Description                                                                                    |  |

|----------------|--------|------------------------------------------------------------------------------------------------|--|

| OccurredEvents | pu16_t | The following event bits may be set:                                                           |  |

|                |        | SP7_EV_ERR<br>Algorithm restarted (lock lost).                                                 |  |

|                |        | SP7_EV_SIG<br>Algorithm detected a DVB-T signal, lock will follow soon.                        |  |

|                |        | SP7_EV_LCK<br>Algorithm acquired a lock on the DVB-T signal and is demodulating now.           |  |

|                |        | SP7_EV_VBER<br>A new Pre-Viterbi BER measurement is ready to be read.                          |  |

|                |        | SP7_EV_RBER<br>A new Post-Viterbi BER measurement (or packet error count) is ready to be read. |  |

|                |        | SP7_EV_SN<br>A new SN and MER measurement is ready to be read.                                 |  |

|                |        | SP7_EV_TPS<br>A new TPS frame is ready to be read.                                             |  |

## 4. Specifications

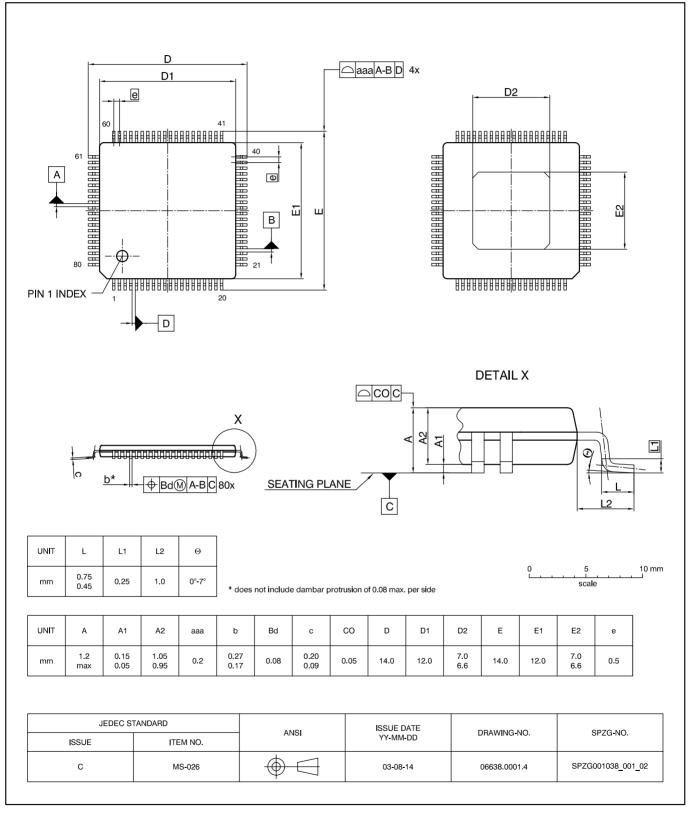

## 4.1. Outline Dimensions

Fig. 4–1:

**PTQFP80-1:** Plastic Thin Quad Flat Package, **80** leads,  $12 \times 12 \times 1.0 \text{ mm}^3$ , exposed die pad Ordering code: PL

## Weight approximately 1.0 g

## 4.2. Pin Connections and Short Descriptions

| Pin<br>No. | Pin Name | Туре | Connection               | Short Description                               |

|------------|----------|------|--------------------------|-------------------------------------------------|

|            |          |      | (If not used)            |                                                 |

| 1          | VDDL     | Р    |                          | Digital core supply 2.5 volt                    |

| 2          | VSS      | GND  |                          | Digital ground                                  |

| 3          | VSS      | GND  |                          | Digital ground                                  |

| 4          | ASEL     | I    |                          | Serial interface address select                 |

| 5          | VSS      | GND  |                          | Digital ground                                  |

| 6          | AGC      | 0    |                          | Automatic gain output                           |

| 7          | VSSA     | GND  |                          | Analog ground                                   |

| 8          | VREF     | Р    |                          | Bias circuitry reference voltage decoupling pin |

| 9          | INM      | I    |                          | Symmetrical IF or Base band input               |

| 10         | INP      | I    |                          | Symmetrical IF or Base band input               |

| 11         | VSSA     | GND  |                          | Analog ground                                   |

| 12         | VDDA     | Р    |                          | Analog supply 2.5V                              |

| 13         | VRM      | Р    |                          | External middle rail reference                  |

| 14         | VDDA     | Р    |                          | Analog supply 2.5V                              |

| 15         | VSSA     | GND  |                          | Analog ground                                   |

| 16         | VRH      | Р    |                          | High reference Voltage                          |

| 17         | VRL      | Р    |                          | Low reference Voltage                           |

| 18         | VSSA     | GND  |                          | Analog ground                                   |

| 19         | VSSA     | GND  |                          | Analog ground                                   |

| 20         | VDDH     | Р    |                          | Digital IO supply 3.3V                          |

| 21         | SCL      | 0    |                          | Clock line for serial protocol                  |

| 22         | SDA      | I/O  |                          | Data line for serial protocol                   |

| 23         | VSS      | GND  |                          | Digital ground                                  |

| 24         | TCLK     | I    | 10 kΩ pull-up<br>to VDDH | JTAG test clock                                 |

| 25         | TDI      | I    | 10 kΩ pull-up<br>to VDDH | JTAG test data in                               |

| 26         | TMS      | I    | 10 kΩ pull-up<br>to VDDH | JTAG test mode select                           |

| 27         | TDO      | 0    |                          | JTAG test data out                              |

| Pin<br>No. | Pin Name | Туре | Connection    | Short Description                          |

|------------|----------|------|---------------|--------------------------------------------|

|            |          |      | (If not used) |                                            |

| 28         | VDDL     | Р    |               | Core supply 2.5V                           |

| 29         | VSS      | GND  |               | Digital ground                             |

| 30         | VDDH     | Р    |               | Digital IO supply 3.3V                     |

| 31         | VSS      | GND  |               | Digital ground                             |

| 32         | VSS      | GND  |               | Digital ground                             |

| 33         | VSS      | GND  |               | Digital ground                             |

| 34         | VSS      | GND  |               | Digital ground                             |

| 35         | IRQN     | 0    |               | Interrupt to host (active low)             |

| 36         | VDDL     | Р    |               | Digital core supply 2.5V                   |

| 37         | VSS      | GND  |               | Digital ground                             |

| 38         | SCL2     | 0    |               | Secondary serial interface clock           |

| 39         | MERR     | 0    |               | MPEG packet error flag                     |

| 40         | MSTRT    | 0    |               | Frame start flag                           |

| 41         | VDDL     | Р    |               | Digital core supply 2.5V                   |

| 42         | VDDH     | Р    |               | Digital IO supply 3.3V                     |

| 43         | MVAL     | 0    |               | MPEG2 data valid signal                    |

| 44         | MCLK     | 0    |               | MPEG2 clock                                |

| 45         | MD_7     | 0    |               | MPEG2 data output                          |

| 46         | VSS      | GND  |               | Digital ground                             |

| 47         | MD_6     | 0    |               | MPEG2 data output                          |

| 48         | MD_5     | 0    |               | MPEG2 data output                          |

| 49         | MD_4     | 0    |               | MPEG2 data output                          |

| 50         | VDDH     | Р    |               | Digital IO supply 3.3V                     |

| 51         | VSS      | GND  |               | Digital ground                             |

| 52         | MD_3     | 0    |               | MPEG2 data output                          |

| 53         | MD_2     | 0    |               | MPEG2 data output                          |

| 54         | MD_1     | 0    |               | MPEG2 data output                          |

| 55         | MD_0     | 0    |               | MPEG2 data output/ MPEG serial data output |

| 56         | OFDM_LCK | 0    |               | Lock signal indicating valid OFDM signal   |

| 57         | VSS      | GND  |               | Digital ground                             |

| 58         | VDDH     | Р    |               | Digital IO supply 3.3V                     |

| Pin<br>No. | Pin Name | Туре | Connection    | Short Description                               |

|------------|----------|------|---------------|-------------------------------------------------|

|            |          |      | (If not used) |                                                 |

| 59         | FEC_LCK  | 0    |               | Lock signal indicating FEC lock                 |

| 60         | NC       |      | LV            | Should be left open                             |

| 61         | VDDL     | Р    |               | Digital core supply 2.5V                        |

| 62         | I2C_EN   | 0    |               | Secondary serial interface enable line          |

| 63         | VSS      | GND  |               | Digital ground                                  |

| 64         | VSS      | GND  |               | Digital ground                                  |

| 65         | VSS      | GND  |               | Digital ground                                  |

| 66         | VSS      | GND  |               | Digital ground                                  |

| 67         | VSS      | GND  |               | Digital ground                                  |

| 68         | VSS      | GND  |               | Digital ground                                  |

| 69         | VDDH     | Р    |               | Digital IO supply 3.3V                          |

| 70         | VSS      | GND  |               | Digital ground                                  |

| 71         | хо       | 0    |               | Crystal oscillator output                       |

| 72         | NC       |      |               | Internally not connected                        |

| 73         | ХІ       | I    |               | Crystal oscillator input                        |

| 74         | VSS      | GND  |               | Digital ground                                  |

| 75         | XPD      | I    |               | Power down mode low = oscillator active         |

| 76         | VDDL     | Р    |               | Digital core supply 2.5V                        |

| 77         | VSS      | GND  |               | Digital ground                                  |

| 78         | IREFSEL  | I    |               | Internal voltage reference select high = enable |

| 79         | RST      | I    |               | Reset signal (active low)                       |

| 80         | VSS      | GND  |               | Digital ground                                  |

## 4.3. Pin Configurations

Fig. 4-1: 80-pin PTQFP package

## 4.4. Electrical Characteristics

### Abbreviations

tbd = to be defined vacant = not applicable positive current values mean current flowing into the chip

## 4.4.1. Absolute Maximum Ratings

Stresses beyond those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these conditions is not implied. Exposure to absolute maximum rating conditions for extended periods will affect device reliability.

This device contains circuitry to protect the inputs and outputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than absolute maximum-rated voltages to this high-impedance circuit.

All voltages listed are referenced to ground (list voltages = 0 V) except where noted.

All GND pins must be connected to a low-resistive ground plane close to the IC.

| Symbol                  | Parameter                                                                        | Pin Name                                                       | Limit | Unit                   |    |

|-------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------|-------|------------------------|----|

|                         |                                                                                  |                                                                | Min.  | Max.                   |    |

| T <sub>A</sub>          | Ambient Operating Temperature                                                    | _                                                              | 0     | 70 <sup>1)</sup>       | °C |

| Τ <sub>S</sub>          | Storage Temperature                                                              | _                                                              | -40   | 125                    | °C |

| P <sub>MAX</sub>        | Maximum Power Dissipation                                                        | _                                                              | -     | 1.1                    | W  |

| V <sub>DDA</sub>        | Analog supply                                                                    | VDDA                                                           | -0.3  | 3.0                    | V  |

| V <sub>DDL</sub>        | Digital core supply                                                              | VDDL                                                           | -0.3  | 3.0                    | V  |

| V <sub>DDH</sub>        | Digital IO supply                                                                | VDDH                                                           | -0.3  | 3.6                    | V  |

| $\Delta V_{SUP}$        | Voltage differences within supply domains (V <sub>DDA</sub> - V <sub>DDL</sub> ) | -                                                              | -0.2  | 0.2                    | V  |

| V <sub>I analgoue</sub> | Analog Input Voltage                                                             | INM; INP; AGC;<br>VRH; VRL                                     | -0.3  | V <sub>DDA</sub> + 0.3 | V  |