# 3-Phase Brushless Motor Driver

Check for Samples: DRV3202-Q1

### **FEATURES**

- 3-Phase Pre-drivers for N-channel MOS Field Effect Transistors (MOSFETs)

- Pulse Width Modulation (PWM) Frequency up to 20 kHz

- Fault Diagnostics

- Charge Pump

- Phase Comparators

- Phase Monitoring Sample and Hold Op-Amps

- Central Processing Unit (CPU) Reset Generator

- Serial Port I/F (SPI)

- Motor Current Sense

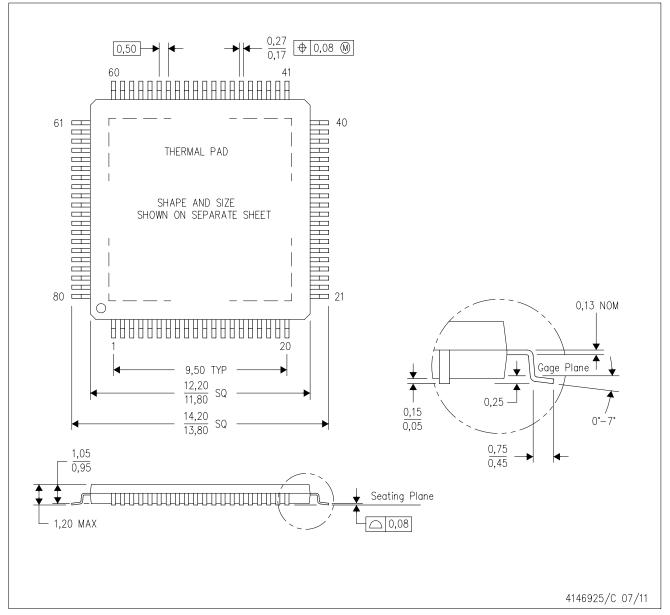

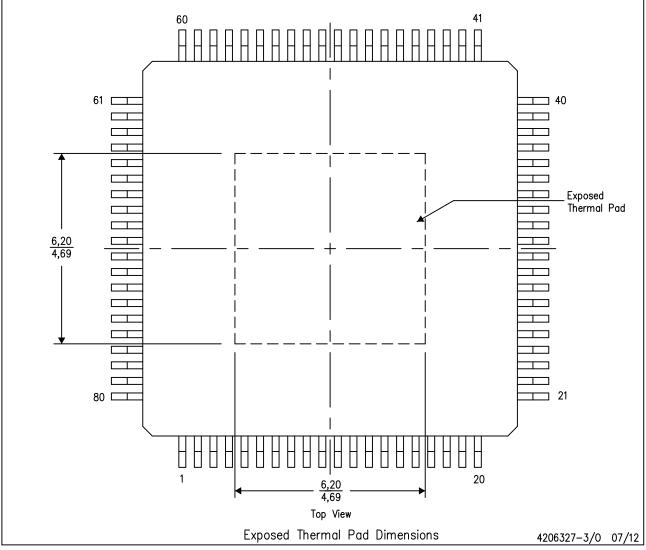

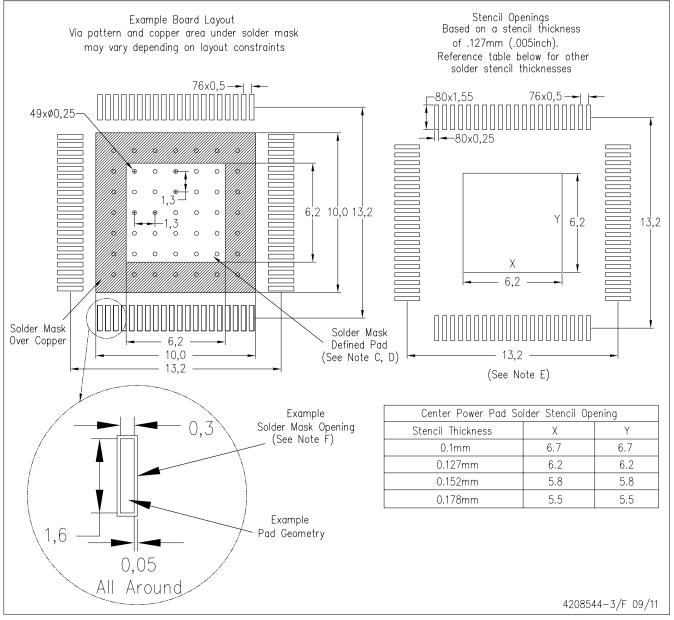

- 80-pin HTQFP

- Controller Area Network (CAN)

- 5-V Regulator

### **APPLICATIONS**

Automotive

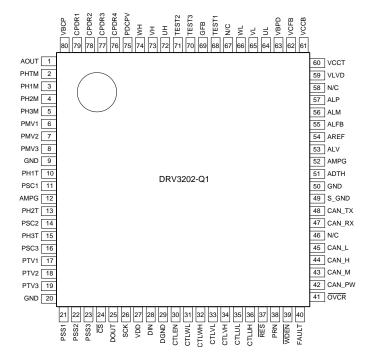

# **PIN OUT**

#### DESCRIPTION

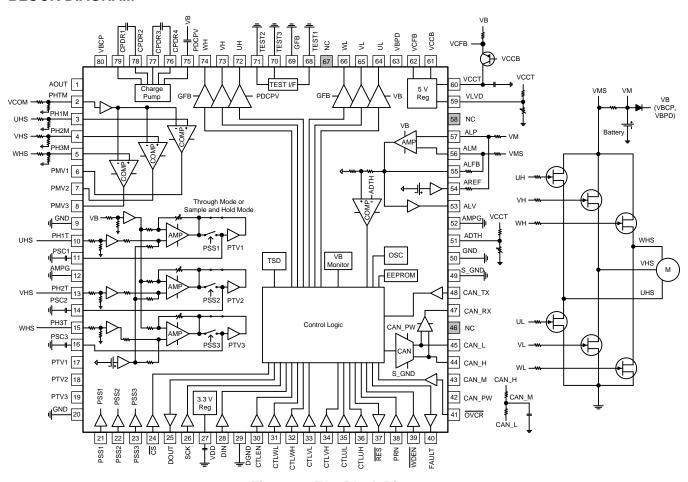

The DRV3202-Q1 device is a field effect transistor (FET) pre-driver designed for 3-phase motor control and its application such as an oil pump or a water pump. It is equipped with three high-side pre-FET drivers and three low-side drivers which are controlled by an external microcontroller (MCU). The power for the high side is supplied by a charge pump and no bootstrap cap is needed. For commutation, this integrated circuit (IC) sends a conditional motor drive signal and output to the MCU. Diagnostics provide undervoltage, overvoltage, overcurrent, overtemperature and power bridge faults. The motor current can be measured using an integrated current sense amplifier and comparator in a battery commonmode range, which allows the motor current to be used in a high-side current sense application. Gain is attained by external resistors. If the MCU does not have enough bandwidth, the phase monitoring sample and hold amplifiers can hold phase information until the MCU is ready to process it. The interfaces include SPI and CAN. The pre-driver and other internal settings can be configured through the SPI. The CAN is used to communicate with other electronic control units (ECUs).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **PIN FUNCTIONS**

|           | PIN    |          | FI         | N FUNCTIONS                           |

|-----------|--------|----------|------------|---------------------------------------|

| NO.       | NAME   | TYPE     | MAX RATING | FUNCTION                              |

| 1         | AOUT   | 0        | -0.3-6 V   | Test mode output                      |

| 2         | PHTM   |          | -1-40 V    | Phase comparator reference input      |

| 3         | PH1M   | i<br>I   | -1-40 V    | Phase comparator input                |

| 4         | PH2M   | i        | -1-40 V    | Phase comparator input                |

| 5         | PH3M   | i<br>I   | -1-40 V    | Phase comparator input                |

| 6         | PMV1   | 0        | -0.3-6 V   | Phase comparator output               |

| 7         | PMV2   | 0        | -0.3-6 V   | Phase comparator output               |

| 8         | PMV3   | 0        | -0.3-6 V   | Phase comparator output               |

| 9, 20, 50 | GND    | I        | -0.3-0.3 V | GND                                   |

| 10        | PH1T   | I        | -2-40 V    | Phase amplifier input                 |

| 11        | PSC1   | 0        | -0.3-6 V   | Sample and hold filter output         |

| 12        | AMPG   | I        | -0.3-0.3 V | Quiet GND                             |

| 13        | PH2T   | I        | -2-40 V    | Phase amplifier input                 |

| 14        | PSC2   | 0        | -0.3-6 V   | Sample and hold filter output         |

| 15        | PH3T   | I        | -2-40 V    | Phase amplifier input                 |

| 16        | PSC3   | 0        | -0.3-6 V   | Sample and hold filter output         |

| 17        | PTV1   | 0        | -0.3-6 V   | Phase amplifier output                |

| 18        | PTV2   | 0        | -0.3-6 V   | Phase amplifier output                |

| 19        | PTV3   | 0        | -0.3-6 V   | Phase amplifier output                |

| 21        | PSS1   | -        | -0.3-6 V   | Sample and hold control signal input  |

| 22        | PSS2   | I        | -0.3-6 V   | Sample and hold control signal input  |

| 23        | PSS3   | I        | -0.3-6 V   | Sample and hold control signal input  |

| 24        | CS     | I        | -0.3-6 V   | SPI chip select                       |

| 25        | DOUT   | 0        | -0.3-6 V   | SPI data output                       |

| 26        | SCK    | I        | -0.3-6 V   | SPI clock                             |

| 27        | VDD    | 0        | -0.3-3.6 V | Digital supply output                 |

| 28        | DIN    | I        | -0.3-6 V   | SPI data input                        |

| 29        | DGND   | I        | -0.3-0.3 V | Digital GND                           |

| 30        | CTLEN  | I        | -0.3-6 V   | Pre-driver parallel enable input      |

| 31        | CTLWL  | I        | -0.3-6 V   | Pre-driver parallel input             |

| 32        | CTLWH  | <u> </u> | -0.3-6 V   | Pre-driver parallel input             |

| 33        | CTLVL  | I        | -0.3-6 V   | Pre-driver parallel input             |

| 34        | CTLVH  | I        | -0.3-6 V   | Pre-driver parallel input             |

| 35        | CTLUL  | _        | -0.3-6 V   | Pre-driver parallel input             |

| 36        | CTLUH  | I        | -0.3-6 V   | Pre-driver parallel input             |

| 37        | RES    | 0        | -0.3-6 V   | Reset output                          |

| 38        | PRN    | I        | -0.3-6 V   | Pulse input                           |

| 39        | WDEN   | I        | -0.3-6 V   | Reset generator enable input          |

| 40        | FAULT  | 0        | -0.3-6 V   | Diagnosis output                      |

| 41        | OVCR   | I        | -0.3-6 V   | Over current reset input              |

| 42        | CAN_PW | I        | -0.3-6 V   | CAN supply input                      |

| 43        | CAN_M  | 0        | –27–40 V   | CAN transceiver middle point terminal |

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

# **PIN FUNCTIONS (continued)**

|            | PIN    |      |            |                                                                  |

|------------|--------|------|------------|------------------------------------------------------------------|

| NO.        | NAME   | TYPE | MAX RATING | FUNCTION                                                         |

| 44         | CAN_H  | Ю    | -27-40 V   | CAN transceiver positive terminal                                |

| 45         | CAN_L  | Ю    | –27–40 V   | CAN transceiver negative terminal                                |

| 46, 58, 67 | N/C    | _    | _          | Not connected                                                    |

| 47         | CAN_RX | 0    | -0.3-6 V   | CAN digital output                                               |

| 48         | CAN_TX | I    | -0.3-6 V   | CAN digital input                                                |

| 49         | S_GND  | I    | -0.3-0.3 V | CAN GND                                                          |

| 51         | ADTH   | I    | -0.3-6 V   | Motor overcurrent threshold input                                |

| 52         | AMPG   | I    | -0.3-0.3 V | Quiet GND                                                        |

| 53         | ALV    | 0    | -0.3-6 V   | Motor current sense amp output                                   |

| 54         | AREF   | 0    | -0.3-40 V  | Motor current sense reference output                             |

| 55         | ALFB   | 0    | -0.3-40 V  | Motor current sense amp feedback                                 |

| 56         | ALM    | I    | -0.3-40 V  | Motor current sense amp negative input                           |

| 57         | ALP    | I    | -0.3-40 V  | Motor current sense amp positive input                           |

| 59         | VLVD   | I    | -0.3-6 V   | V <sub>CC</sub> undervoltage threshold input                     |

| 60         | VCCT   | I    | -0.3-6 V   | V <sub>CC</sub> supply input                                     |

| 61         | VCCB   | 0    | -0.3-40 V  | V <sub>CC</sub> regulator base drive for PNP external transistor |

| 62         | VCFB   | I    | -0.3-40 V  | V <sub>CC</sub> regulator current sense input                    |

| 63         | VBPD   | I    | -0.3-40 V  | VB input                                                         |

| 64         | UL     | 0    | -0.3–20 V  | Pre-driver output                                                |

| 65         | VL     | 0    | -0.3–20 V  | Pre-driver output                                                |

| 66         | WL     | 0    | -0.3–20 V  | Pre-driver output                                                |

| 68         | TEST1  | I    | -0.3-6 V   | Test input                                                       |

| 69         | GFB    | I    | -0.3-0.3 V | Power GND                                                        |

| 70         | TEST3  | I    | -0.3–20 V  | Test input                                                       |

| 71         | TEST2  | I    | -0.3-6 V   | Test input                                                       |

| 72         | UH     | 0    | -0.3-40 V  | Pre-driver output                                                |

| 73         | VH     | 0    | -0.3-40 V  | Pre-driver output                                                |

| 74         | WH     | 0    | -0.3-40 V  | Pre-driver output                                                |

| 75         | PDCPV  | 0    | -0.3-40 V  | Charge pump output                                               |

| 76         | CPDR4  | 0    | -0.3-40 V  | Charge pump output                                               |

| 77         | CPDR3  | 0    | -0.3-40 V  | Charge pump output                                               |

| 78         | CPDR2  | 0    | -0.3-40 V  | Charge pump output                                               |

| 79         | CPDR1  | 0    | -0.3-40 V  | Charge pump output                                               |

| 80         | VBCP   | I    | -0.3-4 0V  | VB input                                                         |

Copyright © 2012, Texas Instruments Incorporated

### **BLOCK DIAGRAM**

Figure 1. Top Block Diagram

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

|                    |                                                |           | MIN         | MAX | UNITS  |

|--------------------|------------------------------------------------|-----------|-------------|-----|--------|

| ESD <sup>(1)</sup> |                                                |           |             |     |        |

| ESD all            | ESD performance of all pins to any other pin   | HBM model | -2          | 2   | kV     |

| pins               | ESD performance of all plins to any other plin | CDM model | -500        | 500 | V      |

| TEMPER             | ATURE                                          |           |             |     |        |

| T <sub>A</sub>     | Operating temperature range                    |           | -40         | 125 | degree |

| TJ                 | Junction temperature                           |           | -40         | 150 | degree |

| Ts                 | Storage temperature                            |           | <b>-</b> 55 | 150 | degree |

(1) ESD testing is performed according to the ACE-Q100 standard.

### THERMAL INFORMATION

|                  | THERMAL METRIC <sup>(1)</sup>                | DRV3202-Q1    | LINUT |

|------------------|----------------------------------------------|---------------|-------|

|                  | THERMAL METRIC                               | HTQP (80-PIN) | UNIT  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 23.0          |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 7.5           |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 7.6           | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.2           | C/VV  |

| ΨЈВ              | Junction-to-board characterization parameter | 7.4           |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 0.3           |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Copyright © 2012, Texas Instruments Incorporated

#### SUPPLY VOLTAGE AND CURRENT

$VB = 12 \text{ V}, T_A = -40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  (unless otherwise specified)

|                 | PARAMETER            | CONDITIONS                            | MIN | TYP | MAX | UNITS |

|-----------------|----------------------|---------------------------------------|-----|-----|-----|-------|

| SUPP            | PLY INPUT            |                                       |     |     |     |       |

| VB              | VB Supply voltage    |                                       | 5.3 | 12  | 18  | V     |

| I <sub>VB</sub> | VB Operating current | VB = 5.3 ~18 V, CAN_TX = High, No PWM |     | 20  | 35  | mA    |

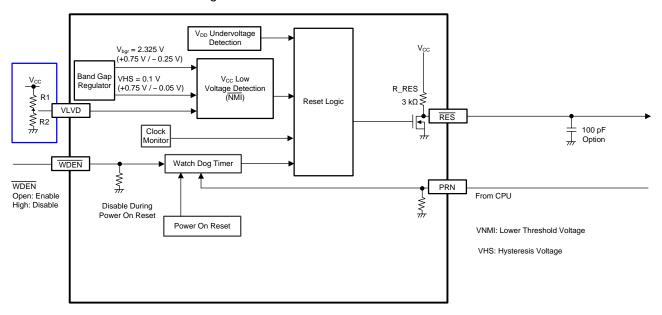

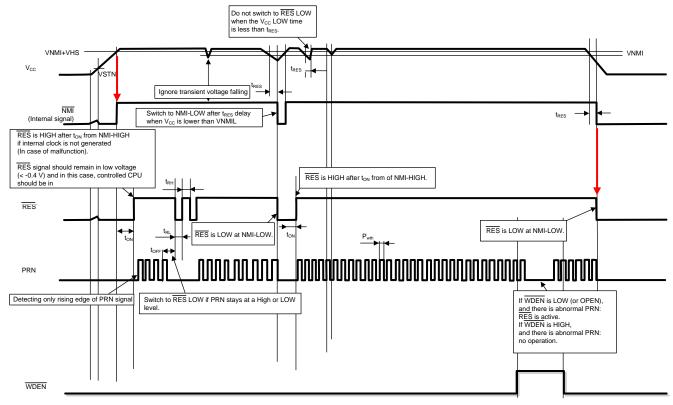

### **WATCHDOG**

### **Description**

The watchdog monitors the PRN signal and  $V_{CC}$  supply level and generates a reset to the MCU through the  $\overline{RES}$  pin if the status of the PRN is not normal or the  $V_{CC}$  is lower than the specified threshold level. The watchdog can be disabled if  $\overline{WDEN}$  is set high.

Figure 2. Watchdog Block Diagram

NOTE:  $\overline{\text{WDEN}} = \text{High}$ ,  $V_{CC}$  undervoltage condition sets  $\overline{\text{RES}} = \text{Low}$

Figure 3. Watchdog Timing Chart

# WATCHDOG ELECTRICAL CHARACTERISTICS(1)

$VB = 12 V,T_A = -40$ °C to 125°C (unless otherwise specified)

|                  | PARAMETER <sup>(2)</sup>                   | CONDITIONS        | MIN | TYP  | MAX | UNITS |

|------------------|--------------------------------------------|-------------------|-----|------|-----|-------|

| WATCH            | IDOG                                       |                   | •   |      | ·   |       |

| VSTN             | Function start V <sub>CC</sub> voltage RES |                   | _   | 0.8  | 1.3 | V     |

| t <sub>ON</sub>  | Power-on time RES                          |                   | 32  | 40   | 48  | ms    |

| t <sub>OFF</sub> | Clock off reset time RES                   |                   | 64  | 80   | 96  | ms    |

| t <sub>RL</sub>  | Reset pulse low time RES                   | Refer to Figure 3 | 16  | 20   | 24  | ms    |

| t <sub>RH</sub>  | Reset pulse high time RES                  |                   | 64  | 80   | 96  | ms    |

| t <sub>RES</sub> | Reset delay time RES                       |                   | 30  | 71.5 | 90  | μs    |

| P <sub>wth</sub> | Pulse width PRN                            |                   | 200 |      |     | ns    |

(1) The watchdog function is disabled and the timing parameters are invalid when the WDEN is at a high level.

(2) Specified by design

Copyright © 2012, Texas Instruments Incorporated

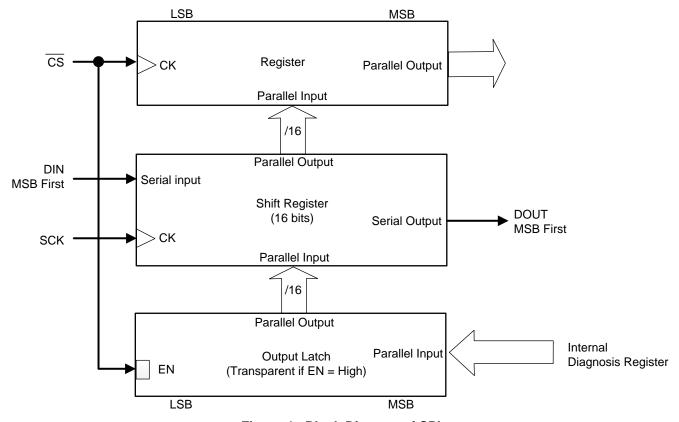

#### SERIAL PORT I/F

### Description

The SPI is used to receive an input byte from CPU and to transmit an output byte to CPU. Four signals are utilized according to the timing chart of Figure 4.

Figure 4. Block Diagram of SPI

#### • CS - Chip Select

- This input signal is utilized to select this IC by CPU.

- This input signal is normally high and the communication is possible only when it is forced low.

- When this input signal falls, the communication between this IC and the CPU starts.

- Transmitted data is latched and the DOUT pin comes out of high impedance.

- When this input signal rises, the communication stops.

- The DOUT pin goes into high impedance. Then, the internal input register updates with the received bits (only if the clock pulse numbers are right and the key bit of the DIN signals is correct).

- The next falling edge starts another communication.

- There is a minimum waiting time between two communications (T<sub>wait</sub>).

- The pin has an internal pullup.

### SCK – Synchronization Serial Clock

- This input signal is utilized to synchronize the communication by CPU.

- It is normally high and the correct clock pulse number is 16.

- At each falling edge, the CPU writes a new bit on the DIN input and this IC writes a new bit on the DOUT pin. At each rising edge, this IC reads the new bit on the DIN pin and the CPU reads the new bit on the DOUT pin.

- The maximum clock frequency is 4 MHz.

- The pin has an internal pullup.

#### DIN – Serial Input Data

#### www.ti.com

- This input signal is used to receive 16-bit data.

- The bits are received in order from the MSB (first) to the LSB (last).

- The pin has an internal pullup.

### DOUT – Serial Output Data

- This output signal is used to transmit 16-bit data.

- It is a 3-state output and it is in high impedance mode when CS is high.

- The serial data bits are transmitted in order from the MSB (first) to the LSB (last).

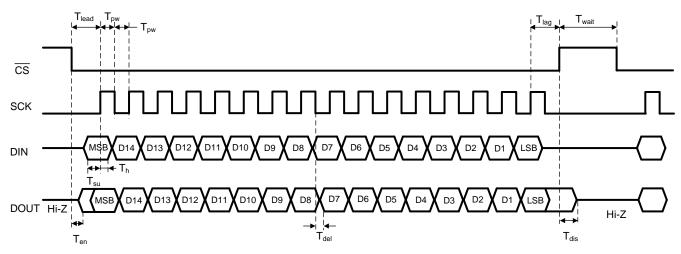

### SPI ELECTRICAL CHARACTERISTICS

$VB = 12 \text{ V}, T_{A} = -40 ^{\circ}\text{C}$  to  $125 ^{\circ}\text{C}$  (unless otherwise specified)

|                   | PARAMETER (1)                                   | CONDITIONS                                | MIN | TYP | MAX | UNITS |

|-------------------|-------------------------------------------------|-------------------------------------------|-----|-----|-----|-------|

| SPI               |                                                 |                                           |     |     | ,   |       |

| F <sub>op</sub>   | Operating frequency                             |                                           | DC  | _   | 4   | MHz   |

| T <sub>lead</sub> | Enable lead time                                |                                           | 100 | -   | -   | ns    |

| T <sub>wait</sub> | Wait time between two successive communications |                                           | 5   | -   | -   | μs    |

| T <sub>lag</sub>  | Enable lag time                                 | Refer to Figure 6                         | 100 | -   | -   | ns    |

| T <sub>pw</sub>   | SCLK pulse width                                |                                           | 100 | -   | -   | ns    |

| T <sub>su</sub>   | Data setup time                                 |                                           | 80  | _   | _   | ns    |

| T <sub>h</sub>    | Data hold time                                  |                                           | 80  | _   | _   | ns    |

| T <sub>dis</sub>  | Disable time                                    |                                           | _   | _   | 80  | ns    |

| T <sub>del</sub>  | Data delay time (SCK to DOUT)                   | C <sub>L</sub> = 50 pF, Refer to Figure 6 | _   | _   | 80  | ns    |

#### (1) Specified by design

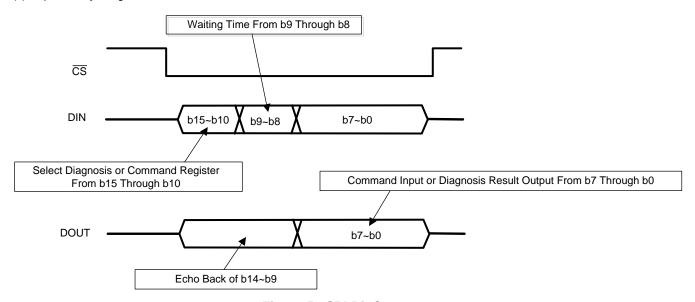

Figure 5. SPI Bit Sequence

Copyright © 2012, Texas Instruments Incorporated

Figure 6. SPI AC Timing Definition

Table 1. SPI Bit Map (DIN)

| ITEM       | B15 | B14 | B13 | B12 | B11 | B10 | В9 | В8 | B7  | В6  | B5 | B4 | В3 | B2 | B1 | В0 |

|------------|-----|-----|-----|-----|-----|-----|----|----|-----|-----|----|----|----|----|----|----|

| COMMAND1   | 0   | 0   | 0   | 0   | 0   | 1   | -  | -  | SHM | SRT | -  | -  | -  | -  | _  | -  |

| COMMAND2   | 0   | 0   | 0   | 0   | 1   | 0   | -  | -  | AG1 | AG0 | -  | -  | -  | -  | _  | -  |

| COMMAND3   | 0   | 0   | 0   | 0   | 1   | 1   | -  | -  | -   | -   | -  | -  | -  | -  | _  | -  |

| DIAG_READ1 | 0   | 0   | 1   | 0   | 0   | 0   | -  | _  | _   | -   | -  | -  | _  | -  | _  | -  |

| DIAG_READ2 | 0   | 1   | 0   | 0   | 0   | 0   | -  | -  | -   | -   | -  | -  | -  | -  | _  | -  |

| DIAG_READ3 | 0   | 1   | 1   | 0   | 0   | 0   | -  | -  | _   | -   | -  | -  | -  | -  | _  | -  |

In Table 1, the B15-B10 are the control bits, so the each command depends on them (listed below).

#### 1. B15-B10 = 0 0 0 0 0 1

These are the commands:

- 1) Phase AMP Sampling Hold Mode (B7 bit)

- 0: OFF (through) (INITIAL VALUE)

- 1: ON (use sample hold mode)

- 2) Phase AMP Short Mode [Short\_Mode] (B6 bit)

- 0: OFF (no calibration) (INITIAL VALUE)

- 1: ON (use calibration mode)

#### 2. **B15-B10 = 0 0 0 0 1 0**

These are the commands:

1) Phase AMP Gain (B7 bit and B6 bit)

B7:0 B6:0; Gain x1 (INITIAL VALUE)

B7:0 B6:1; Gain x2

B7:1 B6:0; Gain x3

B7:1 B6:1; Gain x4

#### 3. **B15-B10 = 0 0 0 0 1 1**

Not used

#### 4. B15-B10 = 0 0 1 0 0 0

This command is to read the diagnosis of the current regulator, SPI communication, overvoltage detection, and input diagnosis.

#### 5. **B15-B10 = 0 1 0 0 0 0**

This command is to read the diagnosis of SPI communication.

#### 6. **B15-B10 = 0 1 1 0 0 0**

Not used

#### 7. B15-B10 = Other command

This command sets the SPI-NG (DOUT, B7) bit.

### Table 2. SPI Bit Map (DOUT)

| ITEM                        | B15 | B14 | B13 | B12 | B11 | B10 | В9 | В8 | B7  | В6  | B5  | B4  | В3  | B2   | B1 | В0  |

|-----------------------------|-----|-----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|------|----|-----|

|                             | 0   | 0   | 0   | 0   | 0   | 0   | 1  | 0  | 0   | 0   | 0   | 0   | 0   | 0    | 0  | 0   |

| ON/OFF COMMAND<br>ECHO BACK | 0   | 0   | 0   | 0   | 0   | 1   | 0  | 0  | -   | _   | -   | _   | -   | -    | -  | -   |

| 20110 271011                | 0   | 0   | 0   | 0   | 0   | 1   | 1  | 0  | -   | -   | -   | -   | _   | -    | -  | -   |

| DIAG_READ1                  | 0   | 0   | 0   | 1   | 0   | 0   | 0  | 0  | VCC | OCD | CCD | VCO | VDO | CPLV | TD | EEP |

| DIAG_READ2                  | 0   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | SPI | -   | -   | -   | _   | -    | -  | -   |

| DIAG_READ3                  | 0   | 0   | 1   | 1   | 0   | 0   | 0  | 0  | -   | -   | -   | -   | _   | -    | -  | -   |

#### 1. **B14-B9 = 0 0 1 0 0 0**

This flag is cleared after the register is read by the CPU.

#### 1) V<sub>CC</sub> Current Detection (B7)

- 0: NORMAL

- 1: Fail (Short to GND or open)

#### 2) Overcurrent Detection (B6)

- 0: NORMAL

- 1: Fail (Overcurrent)

#### 3) CAN Current Detection (B5)

- 0: NORMAL

- 1: Fail (Overcurrent)

#### 4) V<sub>CC</sub> Overvoltage Detection (B4)

- 0: NORMAL

- 1: Fail (V<sub>CC</sub> overvoltage)

#### 5) V<sub>DD</sub> Overvoltage Detection (B3)

- 0: NORMAL

- 1: Fail (V<sub>DD</sub> overvoltage)

#### 6) CPV Low Voltage Detection (B2)

- 0: NORMAL

- 1: Fail (CPV low voltage)

#### 7) Thermal Detection (B1)

- 0: NORMAL

- 1: Fail (Overtemperature)

#### 8) EEPROM\* Data Consistency Check (B0)

- 0: NORMAL

- 1: Fail (EEPROM DATA CRC error)

\*ASIC calibration EEPROM

## NOTE

Just after power-on of the IC, some of the bits listed above may be set depending on the apply sequence of VB. It is recommended to issue a DIAG\_READ1 to clear these bits prior to all S/W sequences.

#### 2. B14-B9 = 0 1 0 0 0 0

This flag is cleared after the register is read by the CPU.

#### 1) SPI-NG (B7)

0: NORMAL

Copyright © 2012, Texas Instruments Incorporated

1: Fail (SPI read and write command is wrong)

Product Folder Links: DRV3202-Q1

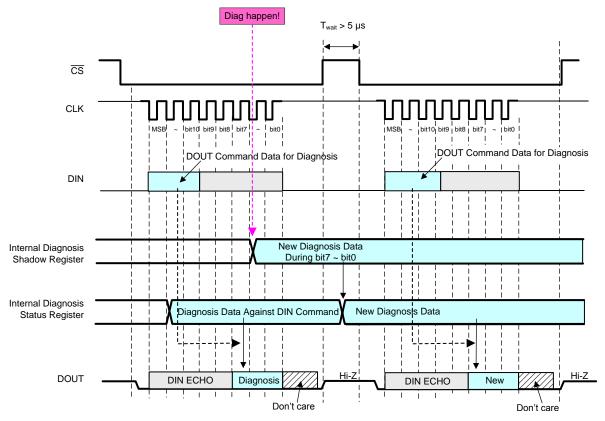

Figure 7. DIAG\_READ

# Internal Diagnosis Register (Status Register and Shadow Register)

If the diagnosis happens during the SPI communication, the function follows this protocol:

The diagnosis information is stored in the shadow register when the diagnosis happens.

After the output of the previous information a new diagnosis is sent from the shadow to the status register, and both registers are output through the DOUT pin.

In this case, a FAULT signal continues to be output until a new diagnosis is read by the CPU.

All diagnosis bits read by the DIAG\_READ1 command happen before the  $\overline{CS}$  falling edge. So, all the diagnosis events that happen right after the  $\overline{CS}$  falling edge are not read by the current DIAG\_READ1 command, instead they are read by the next DIAG\_READ1 command.

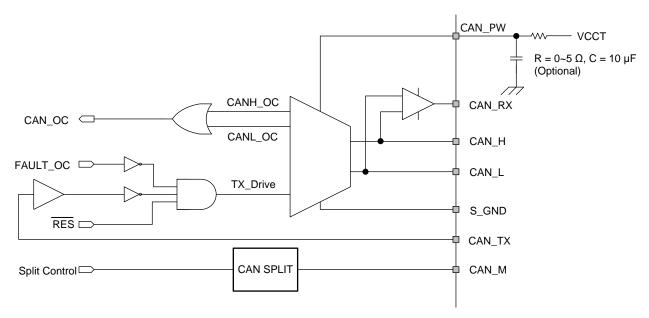

### **CAN**

Figure 8. CAN Block Diagram

### **Description**

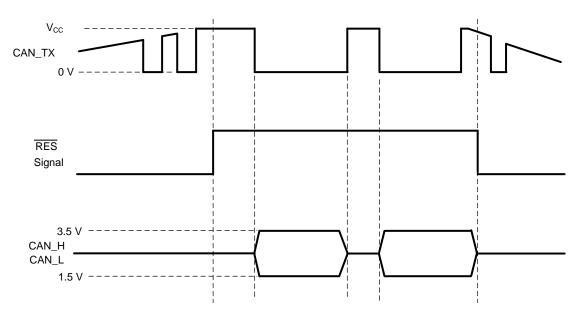

The CAN data from CAN control logic is transmitted to other systems through the CAN bus. The receiver compares the CAN\_H-CAN\_L voltage levels against an internally generated reference and the result is output through CAN\_TX. It has overcurrent protection, shown in Figure 12.

### **CAN ELECTRICAL CHARACTERISTICS**

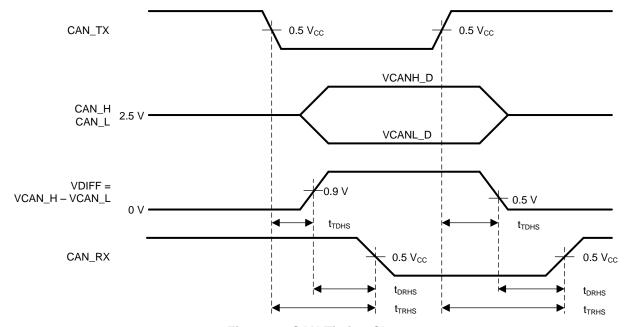

$VB = 12 \text{ V}, T_A = -40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  (unless otherwise specified)

|                                          | PARAMETER                                                                | CONDITIONS                                                | MIN  | TYP | MAX  | UNITS |

|------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------|------|-----|------|-------|

| CAN (TRANSMITTER SEC                     | CTION)                                                                   |                                                           |      |     |      |       |

| VCAN_H                                   | D                                                                        |                                                           | 2    | 2.5 | 3    | V     |

| VCAN_L                                   | Bus voltage recessive                                                    | $CAN\_TX = V_{CC}, I_{CANH} = I_{CANL} = 0,$              | 2    | 2.5 | 3    | V     |

| VDIFF =<br>(VCAN_H - VCAN_L)             | Differential output voltage                                              | see Figure 9                                              | -500 | 0   | 50   | mV    |

| VCAN_H                                   | Bus voltage recessive 2                                                  | CAN_TX = VCCRL = 60 Ω between CAN_H                       | 2.25 | 2.5 | 2.75 | V     |

| VCAN_L                                   | Bus voltage recessive 2                                                  | and CAN_L, see Figure 9 and Figure 10                     | 2.25 | 2.5 | 2.75 | V     |

| VCANH_D                                  | Dominant state CAN_H output voltage                                      | CAN_TX = 0 V, R <sub>L</sub> = 60 Ω between CAN_H         | 2.75 | 3.5 | 4.5  | V     |

| VCANL_D                                  | Dominant state CAN_L output voltage                                      | and CAN_L, see Figure 9                                   | 0.5  | 1.5 | 2.25 | V     |

| VDIFF =<br>(VCANH_D - VCANL_D)           | Differential output voltage                                              | CAN_TX = 0 V, $R_L$ = 60 $\Omega$ between CAN_H and CAN_L | 1.5  | 2   | 3    | V     |

| IA_CANH                                  | CAN_H short circuit threshold current                                    | CAN_TX = 0 V                                              | 70   | -   | 160  | mA    |

| IA_CANL                                  | CAN_L short circuit threshold current                                    | CAN_TX = 0 V                                              | 70   | -   | 160  | mA    |

| t <sub>OVCAN</sub>                       | Overcurrent to output switch-off delay                                   | Refer to Figure 12                                        | 200  |     |      | ns    |

| T <sub>RESCAN</sub>                      | Self recovery time                                                       | Refer to Figure 12                                        | 8    | 25  | 50   | μs    |

| CAN (RECEIVER SECTION                    | N)                                                                       |                                                           |      |     |      |       |

| V <sub>DOM</sub>                         | Differential input voltage for dominant state (VDIFF = VCAN_H - VCAN_L)  | $VCAN_L = -12 V \text{ to } 12 V, CAN_TX = V_{CC}$        | 900  |     |      | mV    |

| V <sub>REC</sub>                         | Differential input voltage for recessive state (VDIFF = VCAN_H - VCAN_L) | VCAN_L = -12 V to 12 V, CAN_TX = V <sub>CC</sub>          |      |     | 500  | mV    |

| V <sub>hys</sub>                         | Differential input hysteresis                                            |                                                           | 80   | 150 | -    | mV    |

| V <sub>com</sub> = (VCAN_H - VCAN_L) / 2 | Input common mode voltage range                                          |                                                           | -12  | -   | 12   | V     |

Copyright © 2012, Texas Instruments Incorporated

# **CAN ELECTRICAL CHARACTERISTICS (continued)**

VB = 12 V,  $T_A = -40$ °C to 125°C (unless otherwise specified)

|                                  | PARAMETER                                         | CONDITIONS                                       | MIN  | TYP | MAX  | UNITS           |

|----------------------------------|---------------------------------------------------|--------------------------------------------------|------|-----|------|-----------------|

| R <sub>IN</sub>                  | Input resistance CAN_H, CAN_L                     | CAN_TX = V <sub>CC</sub>                         | 5    | -   | 50   | kΩ              |

| R <sub>DIFF</sub>                | Differential input resistance                     | $CAN_TX = V_{CC}$                                | 10   | -   | 100  | kΩ              |

| C <sub>IN</sub> <sup>(1)</sup>   | Input capacitance to ground CAN_H, CAN_L          | CAN_TX = V <sub>CC</sub>                         | -    | 20  | 46   | pF              |

| C <sub>DIFF</sub> <sup>(1)</sup> | Differential input capacitance to ground          | $CAN_TX = V_{CC}$                                | _    | 10  | -    | pF              |

| C <sub>IN</sub> <sup>(1)</sup>   | Input capacitance between CAN_H and CAN_L         | CAN_TX = V <sub>CC</sub>                         | _    | -   | 46   | pF              |

| CAN (AC CHARACTERIS              | TIC)                                              |                                                  |      |     |      |                 |

| t <sub>TDhHS</sub>               | Delay time from CAN_TX to VDIFF = VCAN_H - VCAN_L | Refer to Figure 9                                | _    | _   | 100  | ns              |

| t <sub>TDIHS</sub>               |                                                   | Refer to Figure 9                                | _    | -   | 100  | ns              |

| t <sub>DRHS</sub>                | Delay time from VDIFF = VCAN_H - VCAN_L to CAN_RX | Refer to Figure 9                                | -    | -   | 150  | ns              |

| t <sub>TRIHS</sub>               | Delay time from CAN_TX to CAN_RX                  | Refer to Figure 9                                | _    | -   | 300  | ns              |

| t <sub>TRhHS</sub>               |                                                   | Refer to Figure 9                                | _    | _   | 300  | ns              |

| SRHS_R                           | Slew rate, CAN_H, rise                            | Threshold set to 20%–80%                         |      | 20  | 85   | ns              |

| SRHS_F                           | Slew rate, CAN_H, fall                            | Threshold set to 80%–20%                         |      | 20  | 85   | ns              |

| SRLS_R                           | Slew rate, CAN_L, rise                            | Threshold set to 20%–80%                         |      | 20  | 85   | ns              |

| SRLS_F                           | Slew rate, CAN_L, fall                            | Threshold set to 80%–20%                         |      | 20  | 85   | ns              |

| CAN (SPLIT, OPTIONAL)            |                                                   |                                                  |      |     | ·    |                 |

| VCAN_M_I                         | Output voltage                                    | I <sub>source</sub> , I <sub>sink</sub> = 500 μA | 0.3  | 0.5 | 0.7  | V <sub>CC</sub> |

| VCAN_M_u                         | Output voltage, unloaded condition                | $R_{measure} > 1 M\Omega$                        | 0.45 | 0.5 | 0.55 | V <sub>CC</sub> |

| CAN (POWER OFF CONE              | DITION)                                           |                                                  |      |     |      |                 |

| R <sub>IN</sub>                  | Input resistance CAN_H, CAN_L                     | VB = 0 V                                         | 10   | -   | 100  | kΩ              |

### (1) Specified by design

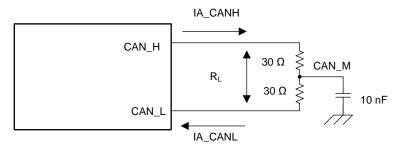

Figure 9. CAN Timing Chart

Test circuit for measurement of AC characteristics and slew rate.

NOTE: If CAN\_L is shorted to GND, try to keep transmission (no overcurrent event).

Figure 10. CAN Testing Condition

Figure 11. CAN Reset Function

Figure 12. Overcurrent Event

Product Folder Links: DRV3202-Q1

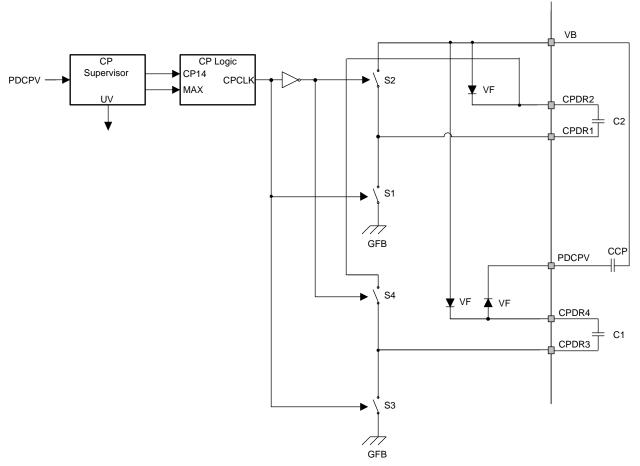

#### **CHARGE PUMP**

### **Description**

The charge pump block generates the supply for high-side and low-side pre-drivers to maintain the gate voltage on the external FETs. External storage cap (CCP) and bucket caps (C1, C2) are used to support pre-driver slope and switching frequency requirements. R1 and R2 can reduce switching current if required. The charge pump has a voltage supervisor for over and undervoltage, and a selectable stop condition for pre-drivers.

Figure 13. Charge Pump Block Diagram

# CHARGE PUMP ELECTRICAL CHARACTERISTICS(1)

$VB = 12 \text{ V}, T_A = -40^{\circ}\text{C}$  to 125°C (unless otherwise specified)

|                                 | PARAMETER                        | CONDITIONS                                                                                    | MIN          | TYP       | MAX     | UNITS |

|---------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------|--------------|-----------|---------|-------|

| CHARGE                          | PUMP                             |                                                                                               | "            |           |         |       |

| V <sub>chv1_0</sub>             |                                  | VB = 5.3 V, $I_{load}$ = 0 mA, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F                             | VB + 7       | VB + 8    | VB + 9  | V     |

| V <sub>chv1_1</sub>             |                                  | VB = 5.3 V, $I_{load}$ = 5 mA, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F                             | VB + 6       | VB + 7    | VB + 8  | V     |

| V <sub>chv1_2</sub>             |                                  | $VB = 5.3 \text{ V}, I_{load} = 8 \text{ mA}, C1 = C2 = 47 \text{ nF}, CCP = 2.2 \mu\text{F}$ | VB + 5       | VB + 6    | VB + 7  | V     |

| V <sub>chv2_0</sub>             |                                  | VB = 12 V, $I_{load}$ = 0 mA, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F                              | VB + 13      | VB + 14   | VB + 15 | V     |

| V <sub>chv2_1</sub>             | Output voltage                   | VB = 12 V, $I_{load}$ = 11 mA, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F                             | VB + 13      | VB + 14   | VB + 15 | V     |

| V <sub>chv2_2</sub>             |                                  | VB = 12 V, $I_{load}$ = 18 mA, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F                             | VB +<br>12.5 | VB + 13.5 | VB + 15 | V     |

| V <sub>chv3_0</sub>             |                                  | VB = 18 V, $I_{load}$ = 0 mA, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F                              | VB + 13      | VB + 14   | VB + 15 | V     |

| V <sub>chv3_1</sub>             |                                  | VB = 18 V, $I_{load}$ = 13 mA, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F                             | VB + 13      | VB + 14   | VB + 15 | V     |

| V <sub>chv3_2</sub>             |                                  | VB = 18 V, $I_{load}$ = 22 mA, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F                             | VB + 13      | VB + 14   | VB + 15 | V     |

| V <sub>chvmax</sub>             | Maximum voltage                  |                                                                                               | 35           | 37.5      | 40      | V     |

| $V_{chvUV}$                     | Undervoltage detection threshold |                                                                                               | VB + 4       | VB + 4.5  | VB + 5  | V     |

| T <sub>chv</sub> <sup>(2)</sup> | Rise time                        | VB = 5.3 V, C1 = C2 = 47 nF, CCP = 2.2 $\mu$ F, V <sub>chvUV</sub> released                   |              | 1         | 2       | ms    |

| R <sub>on</sub>                 | On resistance S1~S4              |                                                                                               |              | 8         |         | Ω     |

|                                 |                                  |                                                                                               |              |           |         |       |

<sup>(1)</sup> No variation of the external components

<sup>(2)</sup> Specified by design

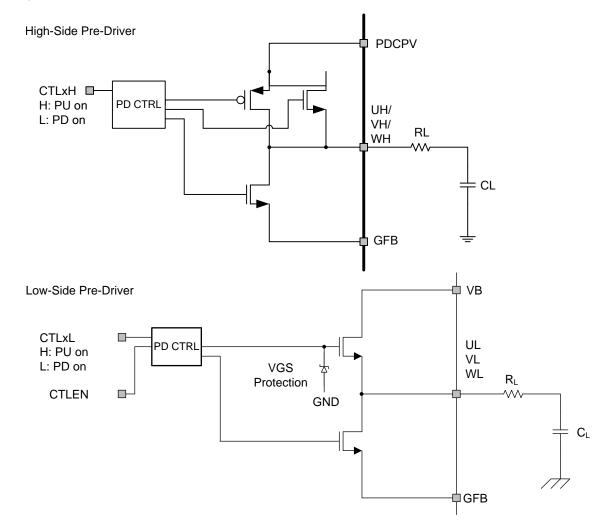

#### PRE-DRIVER

### Description

The pre-driver block provides three high-side pre-drivers and three low-side pre-drivers to drive external N-channel MOSFETs. The turn on side of the high-side pre-drivers supply the large N-channel transistor current to quickly charge and PMOS support output voltage up to PDCPV. The turn off side supplies the large N-channel transistor current to quickly discharge, while the low-side pre-drivers supply the large N-channel transistor current for charge and discharge. The output voltage of the low-side pre-driver is controlled by VB and it has VGS protection to make less than 18 V. The pre-driver has a stop condition in some fault conditions (\$16 Error Detection).

Figure 14. Pre-driver Block Diagram

# PRE-DRIVER ELECTRICAL CHARACTERISTICS

VB = 12 V,  $T_A = -40$ °C to 125°C (unless otherwise specified)

|                                      | PARAMETER                   | CONDITIONS                                                                   | MIN                    | TYP                        | MAX | UNITS |

|--------------------------------------|-----------------------------|------------------------------------------------------------------------------|------------------------|----------------------------|-----|-------|

| HIGH SIDE                            | PRE-DRIVER                  |                                                                              |                        |                            |     |       |

| V <sub>OH_H</sub>                    | Output voltage high         | I <sub>sink</sub> = 10 mA, U(V/W)H – GFB                                     | V <sub>chv</sub> – 2.7 | V <sub>chv</sub> –<br>1.35 |     | V     |

| $V_{OL\_H}$                          | Output voltage low          | I <sub>source</sub> = 10 mA, U(V/W)H – GFB                                   |                        | 60                         | 120 | mV    |

| R <sub>ONH_HP</sub>                  | ON resistance pull up (Pch) | U(V/W)H = PDCPV - 1 V                                                        |                        | 135                        | 270 | Ω     |

| R <sub>ONH_HN</sub>                  | ON resistance pull up (Nch) | U(V/W)H = PDCPV - 2.5 V                                                      |                        | 8                          | 16  | Ω     |

| R <sub>ONL_H</sub>                   | ON resistance pull down     |                                                                              |                        | 6                          | 12  | Ω     |

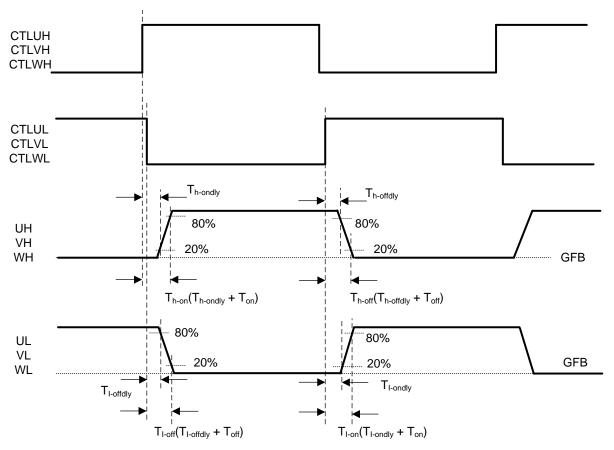

| T <sub>on_h</sub> <sup>(1)</sup>     | Turn-on time                | VB = 5.3 ~ 18 V, $C_L$ = 11 nF, $R_L$ = 0 $\Omega$ from 20% to 80%           | 100                    | 300                        | 500 | ns    |

| T <sub>off_h</sub> <sup>(1)</sup>    | Turn-off time               | VB = 5.3 ~ 18 V, $C_L$ = 11 nF, $R_L$ = 0 $\Omega$ from 80% to 20%           | 100                    | 300                        | 500 | ns    |

| T <sub>h-ondly</sub> <sup>(1)</sup>  | Output delay time           | VB = 5.3 ~ 18 V, $C_L$ = 11 nF, $R_L$ = 0 $\Omega$ to 20%, see Figure 15     | 100                    | 200                        | 400 | ns    |

| T <sub>h-offdly</sub> <sup>(1)</sup> | Output delay time           | VB = 5.3 ~ 18 V, $C_L$ = 11 nF, $R_L$ = 0 $\Omega$ to 80%, see Figure 15     | 100                    | 200                        | 400 | ns    |

| LOW SIDE                             | PRE-DRIVER                  |                                                                              |                        |                            |     |       |

| V <sub>OH_L</sub>                    | Output voltage high         | I <sub>sink</sub> = 10 mA, U(V/W)L – GFB                                     | VB - 0.14              | VB-0.07                    |     | V     |

| V <sub>OL_L</sub>                    | Output voltage low          | I <sub>source</sub> = 10 mA, U(V/W)L - GFB                                   |                        | 70                         | 140 | mV    |

| R <sub>ONH_L</sub>                   | ON resistance pull up       |                                                                              |                        | 7                          | 14  | Ω     |

| R <sub>ONL_L</sub>                   | ON resistance pull down     |                                                                              |                        | 7                          | 14  | Ω     |

| T <sub>on_l</sub> (1)                | Turn-on time                | VB = 5.3 ~ 18 V, $C_L$ = 22 nF, $R_L$ = 0 $\Omega$ from 20% to 80%           | 100                    | 300                        | 800 | ns    |

| T <sub>off_I</sub> <sup>(1)</sup>    | Turn-off time               | VB = 5.3 ~ 18 V, $C_L$ = 22 nF, $R_L$ = 0 $\Omega$ from 80% to 20%           | 100                    | 300                        | 800 | ns    |

| T <sub>I-ondly</sub> <sup>(1)</sup>  | Output delay time           | VB = 5.3 ~ 18 V, $C_L$ = 22 nF, $R_L$ = 0 $\Omega$ to 20%, see Figure 15     | 100                    | 200                        | 400 | ns    |

| T <sub>I-offdly</sub> <sup>(1)</sup> | Output delay time           | VB = 5.3 ~ 18 V, $C_L$ = 22 nF, $R_L$ = 0 $\Omega$ to 80%, see Figure 15     | 100                    | 200                        | 400 | ns    |

| V <sub>CLAMP</sub>                   | VGS protection voltage      |                                                                              | 16                     | 18                         | 20  | V     |

| T <sub>diff1</sub> <sup>(1)</sup>    | Differential time 1         | VB = $5.3 \sim 18$ V ( $T_{h-on}$ )–( $T_{l-off}$ ), see Figure 15           | -300                   |                            | 300 | ns    |

| T <sub>diff2</sub> <sup>(1)</sup>    | Differential time 2         | VB = 5.3 ~ 18 V (T <sub>I-on</sub> )–(T <sub>h-off</sub> ), see<br>Figure 15 | -300                   |                            | 300 | ns    |

<sup>(1)</sup> Specified by design

Copyright © 2012, Texas Instruments Incorporated

Figure 15. Delay Time from Input to Output

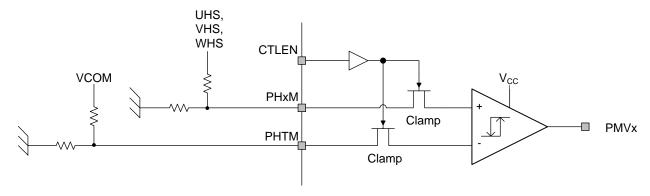

#### PHASE COMPARATOR

# **Description**

A 3-channel comparator module monitors the external FET by detecting voltage across the drain-source for highside and low-side FETs. PHTM is the threshold level of comparators usable for sensorless communication. Figure 16 shows an example of the threshold level. There is no detection when CTLEN = Low.

Figure 16. Phase Comparator Block Diagram

### PHASE COMPARATORS ELECTRICAL CHARACTERISTICS

VB = 12 V.  $T_{A} = -40 ^{\circ}\text{C}$  to  $125 ^{\circ}\text{C}$  (unless otherwise specified)

|                                    | PARAMETER                  | CONDITIONS                   | MIN                   | TYP | MAX                   | UNITS |

|------------------------------------|----------------------------|------------------------------|-----------------------|-----|-----------------------|-------|

| PHASE C                            | OMPARATOR                  | •                            | •                     |     |                       |       |

| V <sub>iofs</sub>                  | Input offset voltage       |                              | -15                   | _   | 15                    | mV    |

| V <sub>inp</sub>                   | Input voltage range (PHTM) | VB = 5.3 ~18 V               | 1.325                 | _   | 4.5                   | V     |

| V <sub>inm</sub>                   | Input voltage range (PHxM) |                              | -1                    | -   | VB                    | V     |

| V <sub>ihys</sub>                  | Input hysteresis voltage   |                              | 100                   | 200 | 400                   | mV    |

| V <sub>OH</sub>                    | Output high voltage        | $I_{sink} = 2.5 \text{ mA}$  | 0.9 × V <sub>CC</sub> | -   | -                     | V     |

| V <sub>OL</sub>                    | Output low voltage         | I <sub>source</sub> = 2.5 mA | _                     | _   | 0.1 × V <sub>CC</sub> | V     |

| T <sub>res_tr</sub> <sup>(1)</sup> | Response time (rising)     | C <sub>L</sub> = 100 pF      | _                     | 0.2 | 0.5                   | μs    |

| T <sub>res_tf</sub> <sup>(1)</sup> | Response time (falling)    | C <sub>L</sub> = 100 pF      | _                     | 0.4 | 1                     | μs    |

(1) Specified by design

Submit Documentation Feedback

Product Folder Links: DRV3202-Q1

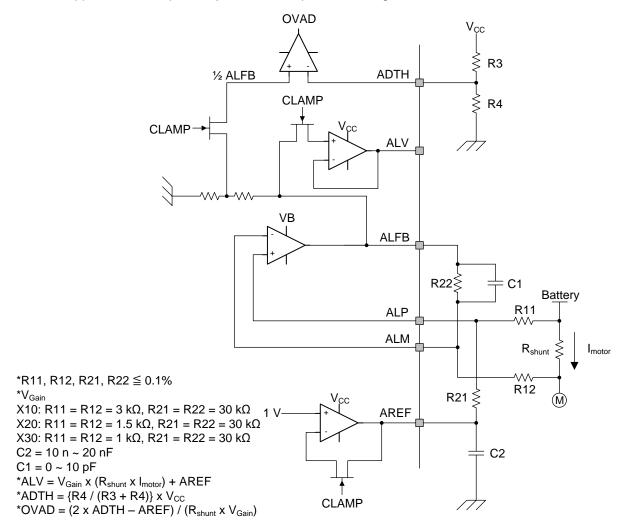

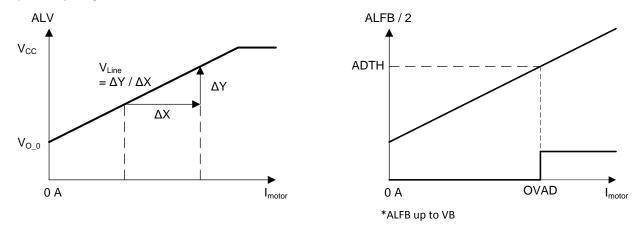

#### **MOTOR CURRENT SENSE**

#### Description

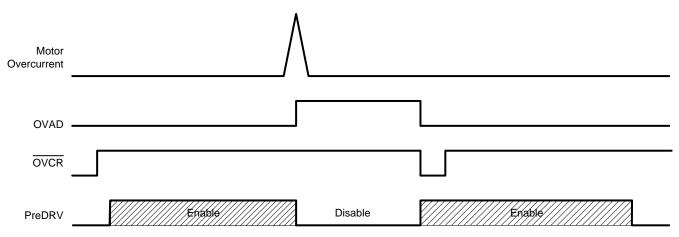

The operational amplifier is operating with an external resistor network for higher flexibility to adjust the current measurement to application requirements. The first stage amplifier is operating with the external resistor and the output voltage up to VB at ALFB. The gain of the amplifier is adjustable by external resistors from x10 to x30. The second stage amplifier is a buffer to MCU at ALV. Current sense has a comparator for motor overcurrent (OVAD). ADTH is the overcurrent threshold level and sets the value by the external resistor as well. Figure 18 shows the curve of the detection level. ALFB is divided by 2, compare this value with ADTH. In the recommended application, zero-point adjustment is required as a large error offset in the initial condition.

Figure 17. Motor Current Sense Block Diagram

### MOTOR CURRENT SENSE ELECTRICAL CHARACTERISTICS(1)

VB = 12 V,  $T_A = -40$ °C to 125°C (unless otherwise specified)

|                  | PARAMETER                   | CONDITIONS                                   | MIN | TYP | MAX | UNITS |

|------------------|-----------------------------|----------------------------------------------|-----|-----|-----|-------|

| MOTOR C          | URRENT <sup>(2)</sup> SENSE | •                                            | •   |     |     |       |

| V <sub>Ofs</sub> | Input offset voltage        |                                              | -5  |     | 5   | mV    |

| V <sub>O_0</sub> | Output voltage (ALV)        | VB = 5.3 ~ 18 V,<br>I <sub>motor</sub> = 0 A |     | 1   |     | V     |

(1) No variation of the external components

(2) Motor current is converted to voltage in test

# MOTOR CURRENT SENSE ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (continued)

VB = 12 V,  $T_A = -40$ °C to 125°C (unless otherwise specified)

|                      | PARAMETER                        | CONDITIONS                                                                                                                                                                                                                                                                                        | MIN  | TYP | MAX | UNITS |

|----------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| V <sub>Line</sub>    | Linearity (ALV)                  | $VB = 5.3 \sim 18 \ V,$<br>$R_{shunt} = 1 \ m\Omega,$<br>$R11 = R12 = 1 \ k\Omega, \ R21 = R22 = 30 \ k\Omega$                                                                                                                                                                                    | -2%  | 30  | 2%  | mV/A  |

| V <sub>Gain</sub>    | Gain                             |                                                                                                                                                                                                                                                                                                   | 10   |     | 30  |       |

| T <sub>set_TR1</sub> | Settling time (Rise) ALV ±1%     | $VB = 5.3 \sim 18 \text{ V},$<br>$R_{shunt} = 1 \text{ m}\Omega, \text{ C1} = 4.7 \text{ pF}, \text{ C}_L = 100 \text{ pF},$<br>$R11 = R12 = 1 \text{ k}\Omega, \text{ R21} = R22 = 30 \text{ k}\Omega,$<br>$I_{motor} = 0 \rightarrow 30 \text{ A}, \text{ (ALV : 1}\rightarrow 1.9 \text{ V)}$  | _    | 1   | 2.5 | μs    |

| T <sub>set_TR2</sub> | Settling time (Rise) ALV ±1%     | $VB = 5.3 \sim 18 \text{ V},$<br>$R_{shunt} = 1 \text{ m}\Omega, C1 = 4.7 \text{ pF}, C_L = 100 \text{ pF},$<br>$R11 = R12 = 1 \text{ k}\Omega, R21 = R22 = 30 \text{ k}\Omega,$<br>$I_{motor} = 0 \rightarrow 100 \text{ A}, (ALV : 1 \rightarrow 4 \text{ V})$                                  | _    | 1   | 2.5 | μs    |

| T <sub>set_TF1</sub> | Settling time (Fall) ALV ±1%     | $VB = 5.3 \sim 18 \text{ V},$<br>$R_{shunt} = 1 \text{ m}\Omega, \text{ C1} = 4.7 \text{ pF}, \text{ C}_L = 100 \text{ pF},$<br>$R11 = R12 = 1 \text{ k}\Omega, \text{ R21} = R22 = 30 \text{ k}\Omega,$<br>$I_{motor} = 30 \rightarrow 0 \text{ A}, \text{ (ALV : 1.9} \rightarrow 1 \text{ V)}$ | _    | 1   | 2.5 | μs    |

| T <sub>set_TF2</sub> | Settling time (Fall) ALV ±1%     | $\begin{split} VB &= 5.3 \sim 18 \ V, \\ R_{shunt} &= 1 \ m\Omega, \ C1 = 4.7 \ pF, \ C_L = 100 \ pF, \\ R11 &= R12 = 1 \ k\Omega, \ R21 = R22 = 30 \ k\Omega, \\ I_{motor} &= 100 \rightarrow 0 \ A, \ (ALV: 4 \rightarrow 1 \ V) \end{split}$                                                   | _    | 1   | 2.5 | μs    |

| OVAD                 | Overcurrent threshold            | 150-A detection, $R_{shunt} = 1 \ m\Omega, \\ R11 = R12 = 1 \ k\Omega, \ R21 = R22 = 30 \ k\Omega, \\ R3 = 8.2 \ k\Omega, \ R4 = 10 \ k\Omega$                                                                                                                                                    | -10% | 150 | 10% | А     |

| TDEL_OVAD (3)        | Propagation delay (Rise or fall) |                                                                                                                                                                                                                                                                                                   | _    | -   | 1.5 | μs    |

### (3) Specified by design

Figure 18. Motor Current Sense and Overcurrent

Copyright © 2012, Texas Instruments Incorporated

Figure 19. Motor Overcurrent Event

**Table 3. Motor Overcurrent Truth Table**

| RES | OVCR | MOTOR OVERCURRENT | OVAD              | PRE-DRIVER ENABLE OR DISABLE |

|-----|------|-------------------|-------------------|------------------------------|

| 0   | -    | _                 | 0 (Clear)         | Disable <sup>(1)</sup>       |

| 1   | 0    | _                 | 0 (Clear) (2) (3) | Enable                       |

|     | 1    | 0                 | Keep              | Enable                       |

|     |      | 1                 | 1 (Set)           | Disable                      |

Product Folder Links: DRV3202-Q1

<sup>(1)</sup> The CTLEN goes to Hi-Z because the external CPU will not drive it when  $\overline{RES} = 0$ , then all the pre-drivers are turned off because CTLEN is internally pulled down.

The OVAD is not set, even if a motor overcurrent error is generated during  $\overline{\text{OVCR}} = 0$ . The OVAD is cleared if  $\overline{\text{OVCR}} = 0$  even when the motor overcurrent error is generated.

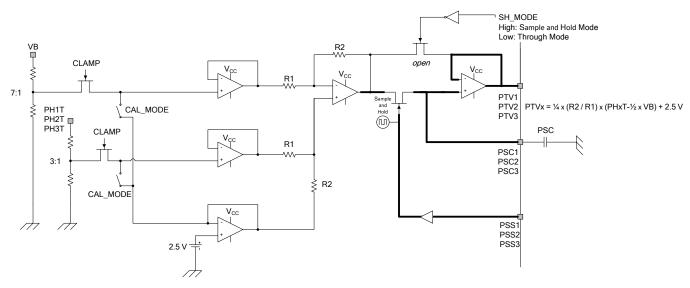

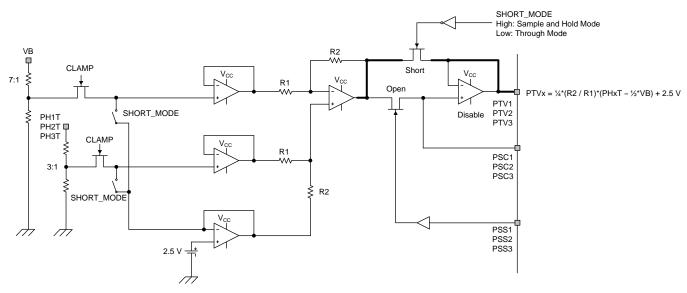

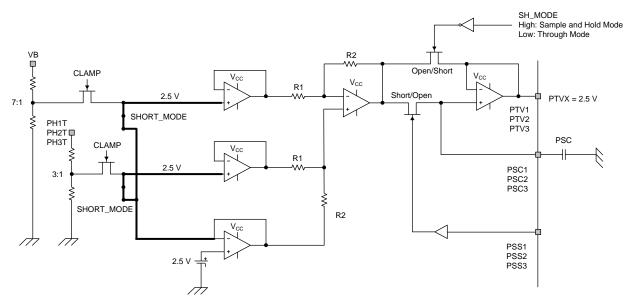

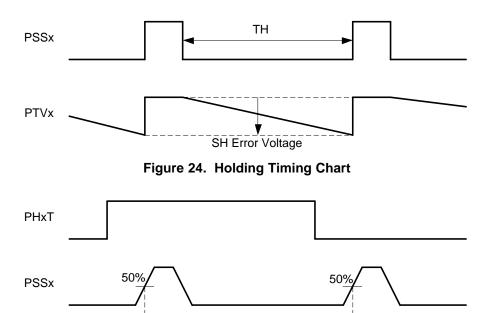

## PHASE AMPLIFIER (Sample and Hold Mode and Through Mode)

### Description

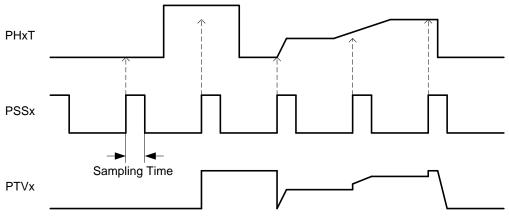

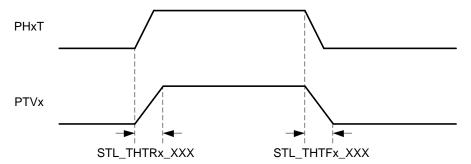

The 3-channel amplifier module monitors the drain-source for high-side and low-side FETs. Two modes (selected by the SPI) are provided: sample and hold mode, and through mode. Sample and hold is controlled by PSSx at the external pins and PSCx connects the charging capacitor. Through mode is real-time detection and the amplifier has x1–x4 gain control.

Figure 20. Sample and Hold Mode Block Diagram

Figure 21. Through Mode Block Diagram

Product Folder Links: DRV3202-Q1

Figure 22. Short Mode (Optional) Block Diagram

# PHASE AMPLIFIER ELECTRICAL CHARACTERISTICS(1)

$VB = 12 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C} \text{ (unless otherwise specified)}$

|                      | PARAMETER                                           | CONDITIONS                                                                                                                           | MIN         | TYP              | MAX         | UNITS |

|----------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|-------------|-------|

| PHASE AMP            | LIFIER                                              |                                                                                                                                      |             |                  |             |       |

| V <sub>ofs_SH</sub>  | Output offset voltage, sample and hold mode         | VB = 5.3–18 V, Gain = 1                                                                                                              | -50         | _                | 50          | mV    |

| V <sub>ofs_TH</sub>  | Output offset voltage, through mode                 | VB = 5.3–18 V, Gain = 1                                                                                                              | <b>-</b> 50 | -                | 50          | mV    |

| V <sub>in_cm</sub>   | Common mode input range                             | VB = 5.3–18 V, Gain = 1–4                                                                                                            | 1.5         |                  | VB –<br>1.5 | ٧     |

| V <sub>out_max</sub> | Maximum output voltage                              | VB = 5.3–18 V, Gain = 1–4                                                                                                            | 4.5         | _                | _           | V     |

| $V_{out\_min}$       | Minimum output voltage                              | VB = 5.3–18 V, Gain = 1–4                                                                                                            | -           | -                | 0.5         | ٧     |

| $V_{gain}^{(2)}$     | Gain                                                |                                                                                                                                      | _           | 1<br>2<br>3<br>4 | -           |       |

| V <sub>out_SH0</sub> | Output voltage, sample and hold mode                | VB = 5.3–18 V, Gain = 1–4, PHxT = VB / 2                                                                                             | _           | 2.5              | _           | V     |

| V <sub>out_TH0</sub> | Output voltage, through mode                        | VB = 5.3–18 V, Gain = 1–4 PHxT = VB / 2                                                                                              | -           | 2.5              | _           | V     |

| V <sub>out_SH1</sub> | Output voltage, sample and hold mode                | VB = 12 V, Gain = 1, PHxT = 1.5 V                                                                                                    | -           | 1.375            | _           | V     |

| V <sub>out_TH1</sub> | Output voltage, through mode                        | VB = 12 V, Gain = 1, PHxT = 1.5 V                                                                                                    | _           | 1.375            | _           | V     |

| $V_{out\_SH2}$       | Output voltage, sample and hold mode                | VB = 12 V, Gain = 1, PHxT = 10.5 V                                                                                                   | _           | 3.625            | -           | V     |

| V <sub>out_TH2</sub> | Output voltage, through mode                        | VB = 12 V, Gain = 1, PHxT = 10.5 V                                                                                                   | _           | 3.625            | -           | V     |

| STL_SHTR             | Settling time (rise), sample and hold mode PTVx ±1% | VB = 12 V, Gain = 1, PSC = 470 pF,<br>PTVx = 100 pF, PHxT = 1.5 V ≥ 10.5 V,<br>(PTVx = 1.375 V $\rightarrow$ 3.625 V), see Figure 25 |             | 1.5              | 3           | μs    |

| STL_THTR             | Settling time (rise), through mode PTVx ±1%         | VB = 12 V, Gain = 1, PTVx = 100 pF,<br>PHxT = 1.5 V ≥ 10.5 V,<br>(PTVx = 1.375 V $\rightarrow$ 3.625 V), see Figure 26               |             | 1.5              | 3           | μs    |

| STL_SHTF             | Settling time (fall), sample and hold mode PTVx ±1% | VB = 12 V, Gain = 1, PSC = 470 pF,<br>PTVx = 100 pF, PHxT = 10.5 V ≥ 1.5 V,<br>(PTVx = 3.625 V → 1.375 V), see Figure 25             |             | 1.5              | 3           | μs    |

| STL_THTF             | Settling time (fall), through mode PTVx ±1%         | VB = 12 V, Gain = 1, PTVx = 100 pF,<br>PHxT = 10.5 V ≥ 1.5V,<br>(PTVx = 3.625 V $\rightarrow$ 1.375 V), see Figure 26                |             | 1.5              | 3           | μs    |

| SH Error<br>Voltage  | Falling voltage                                     | VB = 5.3–18 V, PSC = 470 pF, TH = 1 mS, see Figure 24                                                                                |             | 5                | 75          | mV    |

- (1) No variation of the external components.

- (2) V<sub>gain</sub> is an SPI setting

Figure 23. Sampling Timing Chart

PTVx

Figure 25. Settling Time Timing Chart (Sample and Hold Mode)

STL\_SHTFx\_XXX

STL\_SHTRx\_XXX

Figure 26. Settling Time Timing Chart (Through Mode)

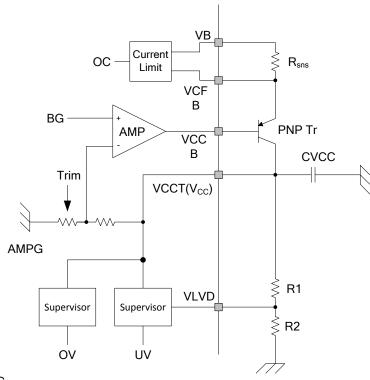

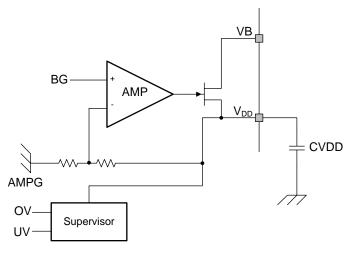

#### **REGULATORS**

### Description

The regulator block offers a 5-V LDO and a 3.3-V LDO. The  $V_{CC}$  LDO regulates VB down to 5 V with an external PNP controlled by the regulator block. The 5-V LDO is supplied to the MCU and other components. The 5-V LDO is protected against a short to GND fault, and the external resistors R1 and R2 set the undervoltage. The  $V_{DD}$  regulator regulates VB down to 3.3-V with an internal FET and a controller.

The regulators detect the overvoltage and undervoltage events of both supplies.

- \*  $R_{sns}$  = 0.2 V / ICLVCC

- \* VCCUV = 2.325 x {(R1+R2) / R2}

Figure 27. V<sub>CC</sub> Block Diagram

Figure 28. V<sub>DD</sub> Block Diagram

# V<sub>CC</sub> AND V<sub>DD</sub> ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

VB = 12 V,  $T_A = -40$ °C to 125°C (unless otherwise specified)

|                                 | PARAMETER                                   | CONDITIONS                                           | MIN  | TYP  | MAX  | UNITS |

|---------------------------------|---------------------------------------------|------------------------------------------------------|------|------|------|-------|

| V <sub>CC</sub>                 |                                             |                                                      |      |      |      |       |

| $V_{CC}$                        | Output voltage                              | $VB = 5.3-18 \text{ V}, I_{load} = 5-150 \text{ mA}$ | 4.9  | 5    | 5.1  | V     |

| IBVCC                           | Base current                                |                                                      | 1.5  |      |      | mA    |

| hfePNP                          | DC current gain of external VCC             |                                                      | 100  |      |      |       |

| VLRVCC                          | Load regulation                             | VB = 5.3–18 V, I <sub>load</sub> = 5–150 mA          | -50  | _    | 50   | mV    |

| CVCC                            | Load capacitance                            |                                                      | 22   |      | 100  | μF    |

| RVCC                            | ESR of external capacitance                 |                                                      |      |      | 300  | mΩ    |

| VCCUV                           | Undervoltage detection threshold            | R1 = 7.5 kΩ, R2 = 10 kΩ,<br>VCCUV > 4 V              | 3.97 | 4.07 | 4.17 | V     |

| VCCUVHY<br>S                    | Undervoltage detection threshold hysteresis |                                                      |      | 100  |      | mV    |

| VCCOV                           | Overvoltage detection threshold             |                                                      | 6    | 6.5  | 7    | V     |

| ICLVCC                          | Current limit                               | $R_{sns} = 0.51 \Omega$                              | 300  | 400  | 550  | mA    |

| TVCC1                           | Rise time                                   | $V_{CC}$ > UVVCC, CVCC = 22 $\mu$ F                  |      | 0.3  | 0.5  | ms    |

| TVCC2                           | Rise time                                   | V <sub>CC</sub> > UVVCC, CVCC = 100 μF               |      | 1    | 1.5  | ms    |

| V <sub>DD</sub>                 |                                             |                                                      |      |      |      |       |

| $V_{DD}$                        | Output voltage                              | VB = 5.3–18 V, I <sub>load</sub> = 0–2 mA            | 3    | 3.3  | 3.6  | V     |

| CVDD                            | Load capacitance                            |                                                      |      | 1    |      | μF    |

| VDDUV                           | Undervoltage detection threshold            |                                                      | 2.2  | 2.3  | 2.4  | V     |

| VDDOV                           | Overvoltage detection threshold             |                                                      | 4.1  | 4.3  | 4.5  | V     |

| T <sub>vdd</sub> <sup>(2)</sup> | Rise time                                   | V <sub>DD</sub> > VDDUV, CVDD = 1 μF                 |      | 75   | 150  | μs    |

<sup>(1)</sup> No variation of the external components

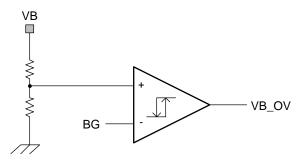

### **VB Monitor**

### **Description**

The block monitors VB overvoltage.

Figure 29. VB Monitor Block Diagram

### **VB MONITOR ELECTRICAL CHARACTERISTICS**

VB = 12 V,  $T_A = -40$ °C to 125°C (unless otherwise specified)

| PARAMETER                                    | CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|------------|------|------|------|-------|

| VB MONITOR                                   |            |      |      |      |       |

| V <sub>stop</sub> Pre-driver stop VB voltage |            | 26.5 | 27.5 | 28.5 | V     |

<sup>(2)</sup> Specified by design

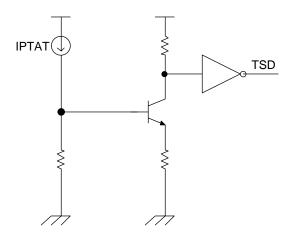

#### THERMAL SHUTDOWN

### Description

The device has temperature sensors that produce a pre-driver stop condition if the chip temperature exceeds 175°.

Figure 30. Thermal Shutdown Block Diagram

#### THERMAL SHUTDOWN ELECTRICAL CHARACTERISTICS

VB = 12 V,  $T_A = -40$ °C to 125°C (unless otherwise specified)

| PARAMETER CONDITIONS |                             |  | MIN | TYP | MAX | UNITS |

|----------------------|-----------------------------|--|-----|-----|-----|-------|

| THERMA               | L SHUT DOWN                 |  |     |     |     |       |

| TSD <sup>(1)</sup>   | Thermal shut down threshold |  | 155 | 175 | 195 | °C    |

(1) Specified by design

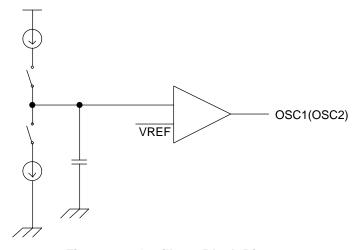

### **OSCILLATOR**

### **Description**

Oscillator block generates two 10-MHZ clock signals. OSC1 is the main clock used for internal logic synchronization and timing control. OSC2 is the secondary clock which is used to monitor the status of OSC1.

Figure 31. Oscillator Block Diagram

Copyright © 2012, Texas Instruments Incorporated

## **OSCILLATOR ELECTRICAL CHARACTERISTICS**

VB = 12 V,  $T_A = -40$ °C to 125°C (unless otherwise specified)

| PARAMETER CONDITIONS |               |  |   | TYP | MAX | UNITS |

|----------------------|---------------|--|---|-----|-----|-------|

| OSCILLA              | TOR           |  |   |     |     |       |

| OSC                  | OSC frequency |  | 9 | 10  | 11  | MHz   |

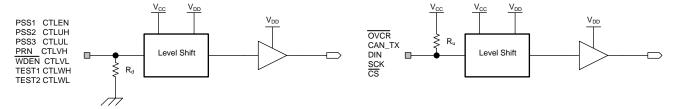

# I/O

Figure 32. Input Buffer 1 Block Diagram

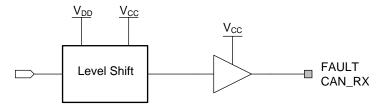

Figure 33. Output Buffer 1 Block Diagram

Figure 34. Output Buffer 2 Block Diagram

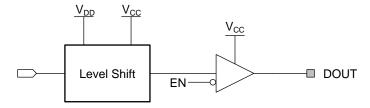

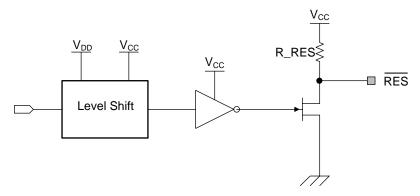

Figure 35. Output Buffer 3 Block Diagram

# **ELECTRICAL CHARACTERISTICS**

$VB = 12 \text{ V}, T_A = -40^{\circ}\text{C}$  to 125°C (unless otherwise specified)

|                         | PARAMETER                  | CONDITIONS                   | MIN                   | TYP | MAX                   | UNITS |

|-------------------------|----------------------------|------------------------------|-----------------------|-----|-----------------------|-------|

| INPUT BUFFER            | ₹1                         |                              |                       |     |                       |       |

| V <sub>IH</sub>         | Input threshold logic high |                              | 0.7 × V <sub>CC</sub> |     |                       | V     |

| V <sub>IL</sub>         | Input threshold logic low  |                              |                       |     | 0.3 × V <sub>CC</sub> | V     |

| R <sub>u</sub>          | Input pullup resistance    |                              | 50                    | 100 | 150                   | kΩ    |

| R <sub>u</sub> (CAN_TX) | Input pullup resistance    |                              | 12.5                  | 25  | 37.5                  | kΩ    |

| R <sub>d</sub>          | Input pulldown resistance  |                              | 50                    | 100 | 150                   | kΩ    |

| OUTPUT BUFF             | ER 1 AND 2                 |                              |                       |     |                       |       |

| V <sub>OH</sub>         | Output level logic high    | I <sub>sink</sub> = 2.5 mA   | 0.9 × V <sub>CC</sub> |     |                       | V     |

| V <sub>OL</sub>         | Output level logic low     | I <sub>source</sub> = 2.5 mA |                       |     | 0.1 × V <sub>CC</sub> | V     |

| OUTPUT BUFF             | ER 3                       |                              |                       |     |                       |       |

| R_RES                   | Pullup resistor            |                              | 1.5                   | 3   | 4.5                   | kΩ    |

| V <sub>OL</sub>         | Output level logic low     | I <sub>source</sub> = 2 mA   |                       |     | 0.1 × V <sub>CC</sub> | V     |

# **ERROR DETECTION**

**Table 4. Error Detection**

| ITEMS                          | SPI                          | PRE-DRIVER | FAULT SIGNAL | RES |

|--------------------------------|------------------------------|------------|--------------|-----|

| VB – Overvoltage               | -                            | STOP       | L            | Н   |

| CP – Overvoltage               | -                            | STOP       | L            | Н   |

| CP – Undervoltage              | Error Bit (CPLV)             | _          | L            | Н   |

| V <sub>CC</sub> – Overvoltage  | Error Bit (VCO)              | _          | L            | Н   |

| V <sub>CC</sub> – Undervoltage | -                            | STOP       | L            | L   |

| V <sub>CC</sub> – Overcurrent  | Error Bit (V <sub>CC</sub> ) | _          | Н            | Н   |

| Motor – Overcurrent            | Error Bit (OVAD)             | STOP       | Н            | Н   |

| V <sub>DD</sub> – Overvoltage  | Error Bit (VDO)              | _          | L            | Н   |

| V <sub>DD</sub> – Undervoltage | -                            | STOP       | L            | L   |

| Thermal Shut Down              | Error Bit (TD)               | STOP       | Н            | Н   |

| Watchdog                       | -                            | _          | L            | L   |

| EEPROM Data Check              | Error Bit (EEP)              | _          | L            | Н   |

| Clock Monitor                  | -                            | _          | L            | L   |

| CAN Overcurrent                | Error Bit (CCD)              | _          | L            | Н   |

| SPI                            | Error Bit (SPI)              | _          | L            | Н   |

Product Folder Links: DRV3202-Q1

# **REVISION HISTORY**

| Cł | hanges from Original (October, 2012) to Revision A                                                                                                                                                                                                                                                                                                | Page |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed max rating for PHTM, PH1M, PH2M, and PH3M from -2 -40 V to -1-40 V.                                                                                                                                                                                                                                                                       | 2    |

| •  | Changed O to IO for pin 44 and 45.                                                                                                                                                                                                                                                                                                                | 3    |

| •  | Deleted Table 1 Pin Equivalent Circuits.                                                                                                                                                                                                                                                                                                          | 3    |

| •  | Changed max I <sub>VB</sub> from 40 to 35 mA.                                                                                                                                                                                                                                                                                                     | 6    |

| •  | Changed CANH and CANL to CAN_H and CAN_L in description section; changed CANH, CANL, and CANM to CAN_H, CAN_L, and CAN_M in block diagram.                                                                                                                                                                                                        | 13   |

| •  | Changed VCANH and VCANL to VCAN_H and VCAN_L in CAN receiver section.                                                                                                                                                                                                                                                                             |      |

| •  | Changed VCANH and VCANL to VCAN_H and VCAN_L in CAN AC characteristic section.                                                                                                                                                                                                                                                                    |      |

| •  | Changed CANH_D to VCANH_D, CANL_D to VCANL_D, and VCANH - VCANL to VCAN_H - VCAN_L in CAN timing chart.                                                                                                                                                                                                                                           |      |

| •  | Changed ICANH to IA_CANH and ICANL to IA_CANL in CAN testing condition image                                                                                                                                                                                                                                                                      |      |

| •  | Changed CANTX to CAN_TX and CANH and CANL to CAN_H and CAN_L in CAN reset function image                                                                                                                                                                                                                                                          |      |

| •  | Changed charge pump description.                                                                                                                                                                                                                                                                                                                  |      |

| •  | Changed V <sub>chv1_12</sub> to V <sub>chv1_2</sub> , V <sub>chv1_20</sub> to V <sub>chv2_12</sub> to V <sub>chv2_12</sub> , V <sub>chv2_20</sub> to V <sub>chv2_2</sub> , V <sub>chv3_22</sub> to V <sub>chv3_2</sub> to V <sub>chv3_2</sub> .                                                                                                   |      |

| •  | Added min and typ values to V <sub>chvmax</sub> parameter.                                                                                                                                                                                                                                                                                        | 17   |

| •  | Changed min, typ and max values for V <sub>chv1 0</sub> through V <sub>chv3 2</sub> ; changed typ R <sub>on</sub> value from 10 to 8                                                                                                                                                                                                              | 17   |

| •  | Changed pre-driver description and updated block diagram.                                                                                                                                                                                                                                                                                         | 18   |