### Contents

| Page | Section  | Title                                                                        |

|------|----------|------------------------------------------------------------------------------|

| 5    | 1.       | Introduction                                                                 |

| 6    | 1.1.     | Main Features                                                                |

| 6    | 1.2.     | Building Blocks                                                              |

| 6    | 2.       | Functional Description                                                       |

| 7    | 3.       | Specifications                                                               |

| 7    | 3.1.     | Outline Dimensions                                                           |

| 7    | 3.2.     | Pin Connections and Short Descriptions                                       |

| 9    | 3.3.     | Pin Descriptions                                                             |

| 9    | 3.3.1.   | VDD, AVDD, VSS, AVSS                                                         |

| 9    | 3.3.2.   | I <sup>2</sup> CD                                                            |

| 9    | 3.3.3.   | I <sup>2</sup> CC                                                            |

| 9    | 3.3.4.   | PORQ                                                                         |

| 9    | 3.3.5.   | CLKO                                                                         |

| 9    | 3.3.6.   | XTI, XTO                                                                     |

| 9    | 3.3.7.   | TE                                                                           |

| 9    | 3.3.8.   | PI0PI3                                                                       |

| 9    | 3.3.9.   | SO1C, SO1I, SO1D                                                             |

| 10   | 3.3.10.  | SI1C, SI1D, SI1I (ADR input interface)                                       |

| 10   | 3.3.11.  | SPDIF                                                                        |

| 10   | 3.3.12.  | SO0C, SO0I, SO0D                                                             |

| 10   | 3.3.13.  | SI1C*, SI1D*, SI1I* (PI1416)                                                 |

| 10   | 3.3.14.  | PI12PI19                                                                     |

| 10   | 3.3.15.  | EODQ, PRTWQ, PR, (PRTRQ, PCSQ                                                |

| 11   | 3.4.     | Pin Configuration                                                            |

| 11   | 3.5.     | Electrical Characteristics                                                   |

| 11   | 3.5.1.   | Absolute Maximum Ratings                                                     |

| 12   | 3.5.2.   | Recommended Operating Conditions                                             |

| 13   | 3.5.3.   | Characteristics                                                              |

| 13   | 3.5.4.   | Recommended Crystal Characteristics                                          |

| 14   | 3.5.4.1. | Single Crystal Mode – 24.576 MHz at DRP 3510A                                |

| 14   | 3.5.4.2. | Single Crystal Mode – 18.432 MHz at MSP 3400C                                |

| 15   | 3.5.4.3. | Dual Crystal Mode – 18.432/24.576 MHz                                        |

| 16   | 3.5.4.4. | Dual Crystal Mode – 18.432/18.432 MHz                                        |

| 16   | 3.5.5.   | System Characteristics                                                       |

| 17   | 4.       | Basic Application                                                            |

| 18   | 5.       | Clock Concepts                                                               |

| 18   | 5.1.     | Both MSP and DRP with own crystal running at a 18.432 MHz frequency          |

| 18   | 5.2.     | MSP running with a 18.432 MHz crystal, DRP running with a 24.576 MHz crystal |

| 19   | 5.3.     | DRP running with a 24.576 MHz crystal, MSP receives its clock from DRP       |

| 19   | 5.4.     | DRP receives its clock from the MSP                                          |

## Contents, continued

| Page     | Section        | Title                                                      |

|----------|----------------|------------------------------------------------------------|

| 20       | 6.             | Interfaces                                                 |

| 20       | 6.1.           | The ADR Input Interface                                    |

| 20       | 6.2.           | The SDO0 Interface                                         |

| 21       | 6.3.           | The SDO1 Interface                                         |

| 21       | 6.4.           | The PIO Interface                                          |

| 21       | 6.4.1.         | General Purpose PIO Mode                                   |

| 22       | 6.4.2.         | PIO-DMA Mode                                               |

| 22       | 6.5.           | The SP/DIF Interface                                       |

| 22       | 6.6.           | Copy Protection                                            |

| 24       | 7.             | The I <sup>2</sup> C Interface                             |

| 24       | 7.1.           | The I <sup>2</sup> C-Data Register                         |

| 24       | 7.2.           | The I <sup>2</sup> C-Control Register                      |

| 25       | 7.3.           | The I <sup>2</sup> C Protocol                              |

| 25       | 7.3.1.         | Controller Writes to the DRP Control Register              |

| 25       | 7.3.2.         | Controller Writes to the DRP Data Register                 |

| 25       | 7.3.3.         | Controller Reads from the DRP Data Register                |

| 26       | 7.4.           | The I <sup>2</sup> C Commands                              |

| 26       | 7.4.1.         | Write into a DRP Register                                  |

| 26       | 7.4.2.         | Default Read Command                                       |

| 27       | 7.4.3.         | Read from a DRP Register                                   |

| 27       | 7.4.4.         | Get ADR Data                                               |

| 28       | 7.4.5.         | Write DMX Data                                             |

| 28       | 7.4.6.         | Write Data into the D0-memory of the DRP                   |

| 29       | 7.4.7.         | Write Data into the D1-memory of the DRP                   |

| 29       | 7.4.8.         | Read Data from the D0-memory of the DRP                    |

| 30       | 7.4.9.         | Read Data from the D1-memory of the DRP                    |

| 30       | 7.4.10.        | Freeze                                                     |

| 30       | 7.4.11.        | The Run Command                                            |

| 31       | 8.             | Internal Registers and Memory Areas                        |

| 31       | 8.1.           | Default Read (Index and Status)                            |

| 31       | 8.2.           | Digital Volume and Channel Mapping (Write)                 |

| 32       | 9.             | Handling of the DRP via Internal Registers                 |

| 32       | 9.1.           | The Internal Fixed Point Number Format                     |

| 33       | 9.2.           | Main Configuration Register 96 (Write)                     |

| 34       | 9.3.           | AGC Register 115 (Read)                                    |

| 34       | 9.4.           | Viterbi Min-distance Register 210 (Read)                   |

| 34       | 9.5.           | Clock-deviation Register 244 (Read, Write)                 |

| 34<br>24 | 9.6.<br>0.7    | Timing Recovery Control Register 168 (Write)               |

| 34<br>34 | 9.7.<br>0.8    | SP/DIF Configuration Register 83 (Write)                   |

| 34<br>25 | 9.8.<br>0.0    | SDO0 Configuration Register 67 (Write)                     |

| 35<br>35 | 9.9.<br>9.10.  | SO0AUXA Register 69 (Write)<br>SO0AUXB Register 70 (Write) |

| 35<br>35 | 9.10.<br>9.11. | SDI1 Input Configuration Register 187 (Write)              |

| 35<br>35 | 9.11.<br>9.12. | SD11 Input Selection Register 79 (Write)                   |

| 35<br>35 | 9.12.<br>9.13. | Actual MPEG Header Register 117 (Read)                     |

| 36       | 10.            | Downloading of Programs                                    |

## Contents, continued

| Page | Section | Title                                                                             |

|------|---------|-----------------------------------------------------------------------------------|

| 37   | 11.     | Application Recommendations                                                       |

| 37   | 11.1.   | MSP 3400C Parameter Setting                                                       |

| 37   | 11.1.1. | Input Gain and Differences between the MSP 3400C Versions C6 and C7               |

| 38   | 11.1.2. | Mode Register                                                                     |

| 39   | 11.1.3. | FIR Coefficients for FIR_REG1                                                     |

| 39   | 11.1.4. | DCO Increment Setting with SAT Carriers                                           |

| 39   | 11.2.   | Pure ADR Music Decoding                                                           |

| 39   | 11.3.   | Receiving the ADR Data                                                            |

| 40   | 11.4.   | Receiving FM / TV Sound with MSP                                                  |

| 40   | 11.5.   | Receiving of ADR                                                                  |

| 41   | 11.6.   | Typical ADR Application Circuit (DRP Application with 24 MHz Single Crystal Mode) |

| 42   | 11.7.   | Typical ADR Application Circuit (DRP Application with 18 MHz Dual Crystal Mode)   |

| 43   | 12.     | Timing Diagrams                                                                   |

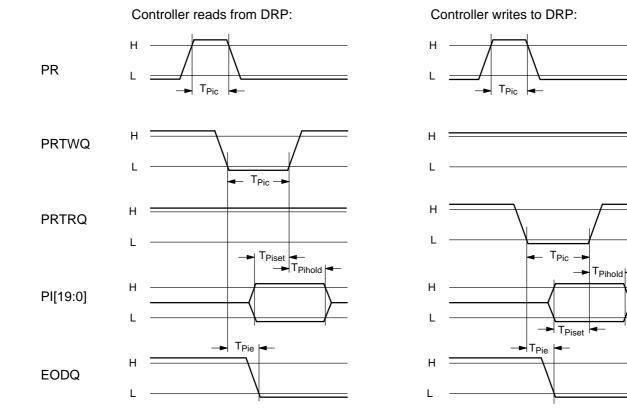

| 43   | 12.1.   | PIO Timing                                                                        |

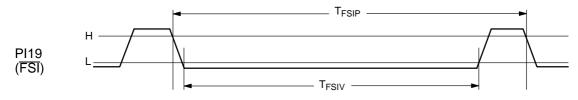

| 43   | 12.2.   | FSI Timing                                                                        |

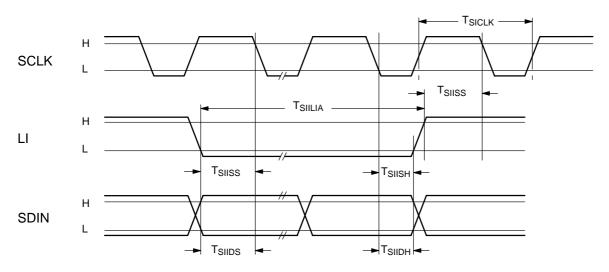

| 44   | 12.3.   | SDI Timing                                                                        |

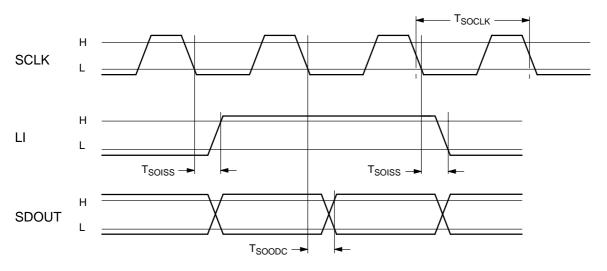

| 44   | 12.4.   | SDO Timing                                                                        |

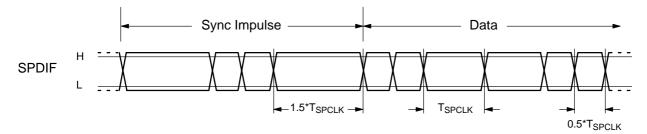

| 44   | 12.5.   | SPDIF Timing                                                                      |

| 45   | 12.6.   | Recommended Power Up Sequence                                                     |

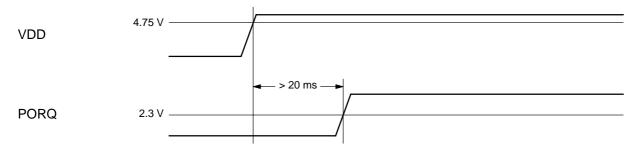

| 45   | 12.6.1. | Power Up Sequence for Dual Crystal Modes                                          |

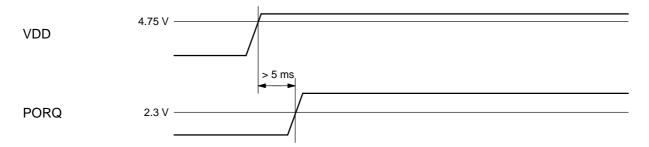

| 45   | 12.6.2. | Power Up Sequence for 18.432 MHz Single Crystal Mode                              |

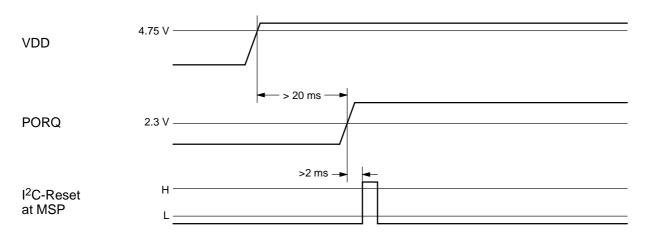

| 45   | 12.6.3. | Power Up Sequence for 24.576 MHz Single Crystal Mode                              |

| 46   | 13.     | DRP 3510A Version History                                                         |

| 48   | 14.     | Data Sheet History                                                                |

#### **Digital Radio Processor**

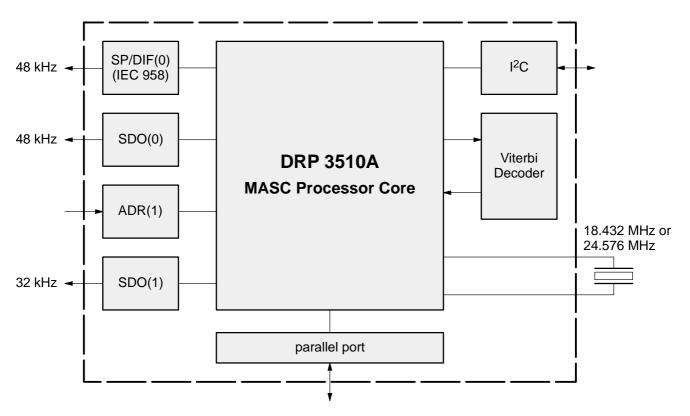

#### 1. Introduction

The DRP 3510A decodes digital audio data transmitted according to the Astra Digital Radio standard<sup>1)</sup>. The DRP 3510A has a well-defined interface to the Multistandard Sound Processor MSP 3400C. The DRP 3510A and the MSP 3400C (alternatively MSP 3410D<sup>2</sup>) provide all functions that are necessary for ADR and DMX<sup>3</sup> decoding. The IC is manufactured in a low-cost 0.8  $\mu$ m CMOS technology and housed in a 44-pin PLCC package.

The DRP is designed as a coprocessor for the MSP, which may already be used in a standard satellite receiver. The video baseband A/D converter, the channel selection, some preprocessing of the digital audio subcarrier, and the TV-sound output are shared with the MSP. Only those parts that are additionally required for ADR-decoding are implemented in the DRP. Thus, upgrading of existing receiver concepts for ADR compatibility is comparably simple and generates a minimum of additional costs. The core of the digital radio processor is based on INTERMETALL'S MASC DSP. A very important feature of the MASC core is its two operating modes: the standard mode that works with 20-bit fixed point numbers and the complex mode that works with 2\*10-bit numbers, consisting of a10-bit fixed point real part and a 10-bit fixed point imaginary part. This feature offers the opportunity of using the same processor for different tasks like QPSK channel demodulation, MPEG Layer 2 source decoding, and system controlling. Consequently, most parts of the ADR decoder are implemented as firmware and could easily be updated if required.

A special controllable viterbi module has been integrated with a burst decoding rate of 2 MBit/s. The data transport between the viterbi module and the DSP is done in the background with an internal non-cycle stealing DMA. This is exactly the same kind of transport mechanism that is used between the processor core and its various interfaces. The complete data-I/O handling is pushed into the background and does not affect the main processing.

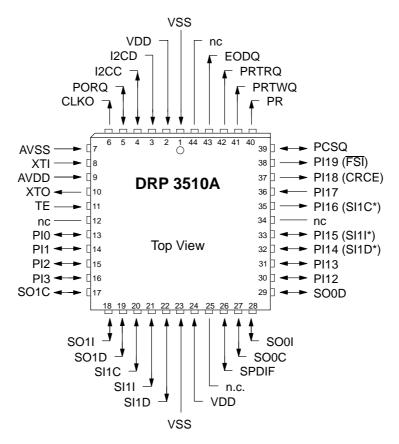

Fig. 1–1: DRP 3510A interfaces

<sup>1)</sup> ASTRA ADR/Rev. 1.3 SYS -078/02-94 TW/ab 15 December 1994

<sup>2)</sup> MSP 3410D is derived from MSP 3400C with an added NICAM decoding feature.

<sup>3)</sup> Digital Music Express (for DMX decoding, a verifier-IC and a smartcard reader is additionally required)

#### 1.1. Main Features

- single power supply 5 V

- 44-pin PLCC plastic package

- on-chip crystal oscillator (18.432 MHz or 24.576 MHz) and internal DCO

- general purpose parallel interface

- 1 serial input interface and 2 serial output interfaces  $I^2S$  (32 kHz and 48 kHz audio out)

- SP/DIF output interface (48 kHz)

- I<sup>2</sup>C control interface

- download feature for alternative operation modes

#### 1.2. Building Blocks

- 20-bit MASC DSP kernel

- 2-kWord internal RAM and 6-kWord ROM (0.75 k config RAM)

- QPSK demodulator

- Viterbi decoder

- V.35 descrambling

- DMX-descrambler

- MPEG1 layer 2 decoder

- ancillary data processing

- sample rate converter

#### 2. Functional Description

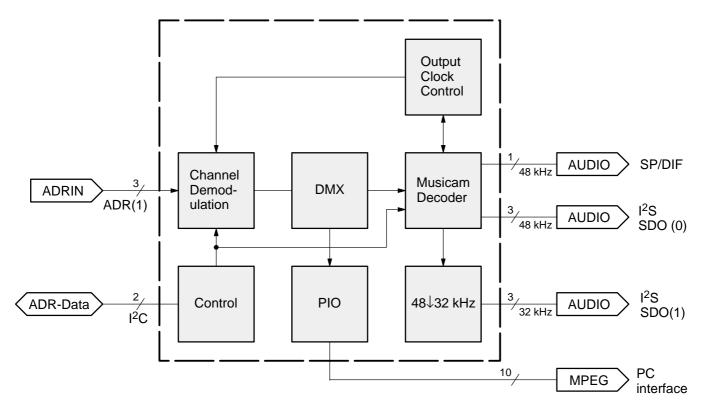

The incoming preprocessed ADR-data stream first passes the carrier offset adjustment and the intersymbol interference filtering blocks. Then, the sample rate of the signal will be decimated to the symbol rate. A bit slicer is used for the generation of the timing recovery and carrier offset adjustment control signals. Then, the signal is sent to the soft decision viterbi decoder. A linear transformation that is placed in front of the viterbi decoder leads to an optimal signal mapping with respect to signal space of the viterbi decoder. The output of the viterbi decoder is copied to the bit stream buffer of the following MPEG1 layer 2 (MUSICAM) decoder.

After the data decompression, the audio signal is available at a sampling frequency of 48 kHz at the I<sup>2</sup>S and the SP/DIF output interfaces. A third output is used as audio feedback for the MSP. For compatibility reasons, a sample rate converter reduces the sampling frequency to 32 kHz. In addition to the pure audio signal, some ancillary data are embedded in the MPEG signal. These data are extracted, deinterleaved, error corrected, and sent to the I<sup>2</sup>C interface, where they may be read by the receiver system controller. The software/hardware module that performs a descrambling of pay radio services (in addition to a verifier IC and a "smart card" reader) is also controlled via the I<sup>2</sup>C bus.

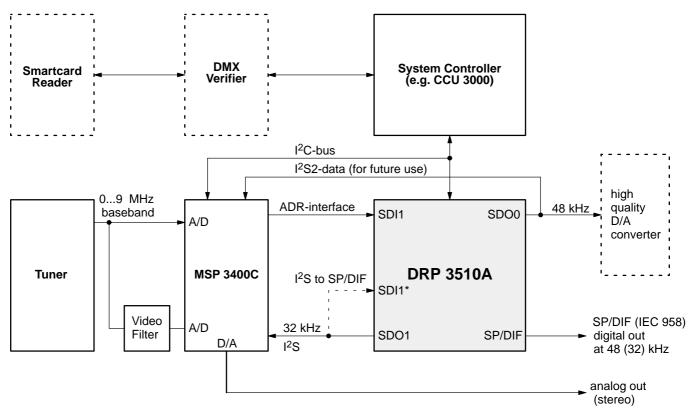

Fig. 1-2: DRP 3510A simplified block diagram

### 3. Specifications

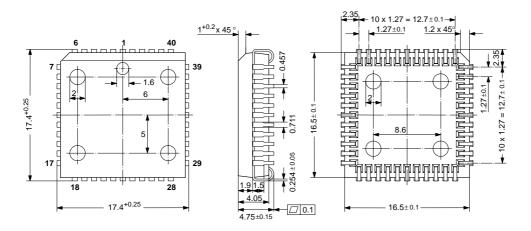

## 3.1. Outline Dimensions

**Fig. 3–1:** 44-Pin Plastic Leaded Chip Carrier Package **(PLCC44)** Weight approximately 2.5 g Dimensions in mm

#### 3.2. Pin Connections and Short Descriptions

NC = not connected; leave vacant LV = if not used, leave vacant X = obligatory; connect as described in circuit diagram VDD\_10k = connected with VDD via 10 k resistor VSS\_10k = connected with VSS via 10 k resistor

| Pin No.<br>PLCC<br>44-pin | Connection<br>(if not used) | Pin Name          | Туре   | Short Description                                           |

|---------------------------|-----------------------------|-------------------|--------|-------------------------------------------------------------|

| 1                         | Х                           | VSS               | SUPPLY | Digital Ground                                              |

| 2                         | Х                           | VDD               | SUPPLY | 4.75 to 5.25 V power supply                                 |

| 3                         | LV                          | l <sup>2</sup> CD | IN/OUT | I <sup>2</sup> C-Data Line                                  |

| 4                         | VDD                         | I <sup>2</sup> CC | IN/OUT | I <sup>2</sup> C-Clock Line (must be set to VDD on reset)   |

| 5                         | Х                           | PORQ              | IN     | Reset active low                                            |

| 6                         | LV                          | CLKO              | OUT    | Clock Out                                                   |

| 7                         | Х                           | AVSS              | SUPPLY | 0 V for analog circuits                                     |

| 8                         | Х                           | ХТІ               | IN     | Crystal Input (18.432 or 24.576 MHz) base mode, Clock Input |

| 9                         | Х                           | AVDD              | SUPPLY | 4.75 to 5.25 V for analog circuits                          |

| 10                        | LV                          | хто               | OUT    | Crystal Oscillator Output                                   |

| 11                        | VSS                         | TE                | IN     | Test Enable                                                 |

| 12                        | NC                          |                   |        |                                                             |

| Pin No.<br>PLCC<br>44-pin | Connection<br>(if not used) | Pin Name     | Туре       | Short Description                                                                                                                |

|---------------------------|-----------------------------|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| 13                        | Х                           | P10          | IN         | PIO DATA [0] Crystal Select.<br>0: 18.432 MHz, 1: 24.576 MHz; should be con-<br>nected with VSS (VDD) via a resistor (e.g. 10 k) |

| 14                        | VSS_10k                     | PI1          | IN         | PIO DATA [1] reserved TASK Input; should be<br>connected with VSS via resistors (10k)                                            |

| 15                        | VSS_10k                     | PI2          | IN         | PIO DATA [2] reserved TASK Input; should be connected with VSS via resistors (10k)                                               |

| 16                        | Х                           | PI3          | IN         | PIO DATA [3]<br>0: ADR-mode, 1: Layer 2 decoder; should be<br>connected with VSS (VDD) via a resistor<br>(e.g. 10 k)             |

| 17                        | Х                           | SO1C         | IN/OUT     | Clock of the SDO1 interface, 32 kHz audio out                                                                                    |

| 18                        | Х                           | SO1I         | OUT        | Frame indication of the SDO1 interface, 32 kHz audio out                                                                         |

| 19                        | Х                           | SO1D         | OUT        | Data of the SDO1 interface, 32 kHz audio out                                                                                     |

| 20                        | х                           | SI1C         | IN/OUT     | Clock of the SDI1 interface, 384 kHz clock of ADR data                                                                           |

| 21                        | х                           | SI1I         | IN         | Frame indication of the SDI1 interface,<br>(I/O of ADR data)                                                                     |

| 22                        | Х                           | SI1D         | IN         | Data of the SDI1 interface, ADR input data                                                                                       |

| 23                        | Х                           | VSS          | SUPPLY     | Digital Ground                                                                                                                   |

| 24                        | Х                           | VDD          | SUPPLY     | 4.75 to 5.25 V power supply                                                                                                      |

| 25                        | NC                          |              |            |                                                                                                                                  |

| 26                        | LV                          | SPDIF        | OUT        | Sony Philips digital interface,<br>48 kHz stereo audio                                                                           |

| 27                        | LV                          | SOOC         | IN/OUT     | Clock of the SDO0 interface,<br>48 kHz audio out                                                                                 |

| 28                        | LV                          | SOOI         | OUT        | Frame indication of the SDO0 interface, 48 kHz audio out                                                                         |

| 29                        | LV                          | SOOD         | OUT        | Data of the SDO0 interface,<br>48 kHz audio out                                                                                  |

| 30                        | LV                          | PI12         | (IN/OUT)   | PIO DATA [12] in/out                                                                                                             |

| 31                        | LV                          | PI13         | (IN/OUT)   | PIO DATA [13] in/out                                                                                                             |

| 32                        | VSS_10k                     | PI14 (SI1D*) | (IN/OUT) I | PIO DATA [14] (alternative input for SI1D)                                                                                       |

| 33                        | VSS_10k                     | PI15 (SI1I*) | (IN/OUT) I | PIO DATA [15] (alternative input for SI1I)                                                                                       |

| 34                        | NC                          |              |            |                                                                                                                                  |

| 35                        | VSS_10k                     | PI16 (SI1C*) | (IN/OUT) I | PIO DATA [16] (alternative input for SI1C)                                                                                       |

| 36                        | LV                          | PI17         | (IN/OUT) O | PIO DATA [17] (not used)                                                                                                         |

| Pin No.<br>PLCC<br>44-pin | Connection<br>(if not used) | Pin Name                | Туре       | Short Description                               |

|---------------------------|-----------------------------|-------------------------|------------|-------------------------------------------------|

| 37                        | LV                          | PI18 (CRCE)             | (IN/OUT) O | PIO DATA [18] (CRC-error)                       |

| 38                        | LV                          | PI19 ( <del>FSI</del> ) | (IN/OUT) O | PIO DATA [19] (frame start impulse, low active) |

| 39                        | VDD_10k                     | PCSQ                    | IN         | PIO Chip Select                                 |

| 40                        | VDD_10k                     | PR                      | IN         | PIO Read/Write                                  |

| 41                        | LV                          | PRTWQ                   | OUT        | PIO Ready to Write                              |

| 42                        | LV                          | PRTRQ                   | OUT        | PIO Ready to Read                               |

| 43                        | LV                          | EODQ                    | OUT        | PIO End of DMA                                  |

| 44                        | NC                          |                         |            |                                                 |

#### 3.3. Pin Descriptions

#### 3.3.1. VDD, AVDD, VSS, AVSS

VDD and AVDD should be blocked against VSS and AVSS. For proper operation and in order to avoid EMV problems, a capacitive blocking of VDD against VSS over a wide frequency range is recommended.

#### 3.3.2. I<sup>2</sup>CD

The  $I^2CD$  line is used for  $I^2C$  data transfers from the DRP to a controller and vice versa.

#### 3.3.3. I<sup>2</sup>CC

The I<sup>2</sup>C clock line is used for the I<sup>2</sup>C clock if the IC is in the operation mode. However, on a power on reset, the I<sup>2</sup>C line determines the operating mode of the internal clock generator of the DRP. If the I<sup>2</sup>CC line is set to low during power on reset, the internal DRP clock is directly taken from the crystal input XTI and the internal crystal oscillator is disabled. In standard ADR mode, the I<sup>2</sup>C clock pin has to set to high level, in order to activate the internal oscillator and the internal DCO, which is used to synchronize the DRP clock system with the data rate of the incoming ADR signal.

#### 3.3.4. PORQ

Reset input (active low). The minimum length of a reset impulse should be  $100 \,\mu s$ . See the timing diagrams (section 12.) for the recommended power up sequence and further details.

#### 3.3.5. CLKO

If the DRPA is driven with a 24.576 MHz quartz, the CLKO pin delivers a synchronized 18.432 MHz clock, otherwise the the CLKO pin is muted.

#### 3.3.6. XTI, XTO

The crystal input XTI can either be used for the crystal application or for a direct input of a clock signal with the correct frequency. If the XTI signal is used for direct input, the input signal has to be DC-free, a minimum level of  $0.7 V_{ss}$  and a maximum level of  $3 V_{ss}$ . The XTO signal is the output of the internal crystal oscillator.

#### 3.3.7. TE

The TE pin is reserved for chip testing only. For customer applications, this pin must always be connected to VSS.

#### 3.3.8. PI0..PI3

In standard PIO mode, these pins are static input pins that allow the selection of different operating modes. The PIO pin is used to select the used crystal frequency. The level of the PIO pin is evaluated within 10 ms after reset. The PI3 pin is used to select the basic operating mode (either ADR or L2-only decoding). The PI1 and PI2 inputs are reserved for future use and have to be set to '0'. Because these PIx pins are generally used as input pins, it is recommended to connect them with a fixed potential. However, in DMA output mode, they operate as output pins. Thus, their connection with VSS or VDD should be done via 10 k resistors in order to avoid shortcircuits.

#### 3.3.9. SO1C, SO1I, SO1D

These three serial data output lines transport the decoded ADR/DMX signal at a sample rate of 32 kHz. An internal sample rate converter performs the 48 to 32 kHz downsampling. For proper ADR-operation, it is mandatory to connect them with one  $I^2S$  input of the MSP. The MSP clock system has to be switched into 'slave mode'. The data word is not delayed vs. the word-strobe (SO1I) signal.

#### 3.3.10. SI1C, SI1D, SI1I (ADR input interface)

The ADR input interface has to be connected with the ADR/S-Bus interface of the MSP chip. In Layer 2 mode, the lines SI1C (for clock) and SI1D (for data) will expect a valid Layer 2 data stream.

#### 3.3.11. SPDIF

The SPDIF interface provides the ADR/DMX data in the digital SPDIF format, in accordance with the consumer standard IEC 958.

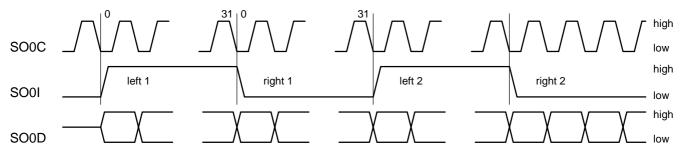

#### 3.3.12. SOOC, SOOI, SOOD

The SO0 output interface is the standard interface for a 48 kHz additional DAC, for full sampling rate output, which is not implemented in the MSP. The data word is not delayed vs. the word-strobe (SO1I) signal by default.

#### 3.3.13. SI1C\*, SI1D\*, SI1I\* (PI14..16)

These lines are used as alternative input lines and could be connected e.g. with the I<sup>2</sup>S output of the MSP. How-

ever, these input pins are not supported by the built-in firmware. Downloaded program codes can use these input lines for alternative functionality of the DRP. An example for an adequate download program is an I<sup>2</sup>S to SP/DIF converter program that can be used to map the analog FM-sound signal from the MSP to the SP/DIF output interface of the DRP. In the standard ADR-mode, these lines are input pins that should be connected via resistors to a fixed level (VSS).

#### 3.3.14. PI12..PI19

In standard ADR mode, the PIO pin PI19 shows the Frame Start Impulse (FSI). This impulse is synchronized with the MPEG frame and is set to low level for at maximum 23 ms, which indicates that a new ADR ancillary data block is available for read-out via I<sup>2</sup>C. The CRC-error pin PI18 will be set to high level for 24 ms (duration of one MPEG Layer 2 frame) when an MPEG CRC error has been detected. In DMA mode, the PI12..PI19 pins will contain the 8-bit aligned undecoded MPEG data stream.

#### 3.3.15. EODQ, PRTWQ, PR, (PRTRQ, PCSQ)

For a description of EODQ, PRTRQ, PR, see section 6.4.2. The PRTRQ line is reserved for future use. The PCSQ line is not used by the actual firmware and should be connected to VDD via a resistor.

#### 3.4. Pin Configuration

Fig. 3-2: 44-pin PLCC package

#### 3.5. Electrical Characteristics

#### 3.5.1. Absolute Maximum Ratings

| Symbol                    | Parameter                                  | Pin No.           | Min.              | Max.                                           | Unit |

|---------------------------|--------------------------------------------|-------------------|-------------------|------------------------------------------------|------|

| T <sub>A</sub>            | Ambient Operating Temperature              | -                 | -20               | 85                                             | °C   |

| Τ <sub>S</sub>            | Storage Temperature                        | -                 | -40               | 125                                            | О°   |

| V <sub>SUP</sub>          | Supply Voltage                             | 2, 9, 24          | -0.2              | 6                                              | V    |

| V <sub>PIN</sub>          | Pin Voltage                                | all other<br>pins | -0.3              | V <sub>SUP</sub> +0.3 or 6<br>whatever is less | V    |

| CL                        | Load Capacitance                           | all               | 0                 | 200                                            | pF   |

| RL                        | Load Resistance to V <sub>SUP</sub> or GND | output<br>pins    | 500 <sup>1)</sup> | infinite                                       | Ω    |

| ΙL                        | Load Current Open Drain Outputs            | 3, 4              |                   | 10                                             | mA   |

| <sup>1)</sup> Shorts will | not damage the IC, if they do not exce     | ed a time per     | iod of 5 s        |                                                |      |

Stresses beyond those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions/Characteristics" of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

## 3.5.2. Recommended Operating Conditions at $V_{SUP}$ = 4.75 to 5.25 V

| Symbol              | Parameter                                                                    | Pin No.         | Min.                | Тур. | Max.     | Unit             |

|---------------------|------------------------------------------------------------------------------|-----------------|---------------------|------|----------|------------------|

| T <sub>A</sub>      | Ambient Operating Temperature                                                | -               | 0                   |      | 65       | °C               |

| V <sub>SUP</sub>    | Supply Voltage                                                               | 2, 9, 24        | 4.75                | _    | 5.25     | V                |

| f <sub>CP</sub>     | Internal Processor Clock<br>Frequency (set by software)                      | _               |                     |      | 40       | MHz              |

| V <sub>DIL</sub>    | Data Input Low Voltage                                                       | all other       | -                   |      | 1        | V                |

| V <sub>DIH</sub>    | Data Input High Voltage                                                      | inputs          | V <sub>SUP</sub> –1 |      | -        | V                |

| t <sub>RES</sub>    | Reset Input Low Time<br>(after V <sub>SUP</sub> has reached specified range) | 5               | 20                  |      |          | ms               |

| t <sub>Pic</sub>    | PIO Timing (see Fig. 12–1)                                                   | 13–22,          | 50                  |      | no limit | ns               |

| t <sub>Pip</sub>    | PIO Timing (see Fig. 12–1)                                                   | 28–43           | 0                   |      | no limit | ns               |

| t <sub>Pir</sub>    | PIO Timing (see Fig. 12–1)                                                   |                 | 0                   |      | no limit | ns               |

| t <sub>Piset</sub>  | PIO Timing (see Fig. 12–1)                                                   |                 | 50                  |      | no limit | ns               |

| t <sub>Pihold</sub> | PIO Timing (see Fig. 12–1)                                                   |                 | 50                  |      | no limit | ns               |

| t <sub>SISCLK</sub> | SDI Timing (see Fig. 12–3)                                                   | 20–22,          | 120                 |      |          | ns               |

| t <sub>SIISS</sub>  | SDI Timing (see Fig. 12–3)                                                   | (32, 33,<br>35) | 30                  |      |          | ns               |

| t <sub>SIIDS</sub>  | SDI Timing (see Fig. 12–3)                                                   |                 | 30                  |      |          | ns               |

| t <sub>SIISH</sub>  | SDI Timing (see Fig. 12–3)                                                   |                 | 30                  |      |          | ns               |

| t <sub>SIIDH</sub>  | SDI Timing (see Fig. 12–3)                                                   |                 | 30                  |      |          | ns               |

| t <sub>SIILIA</sub> | SDI Timing (see Fig. 12–3)                                                   |                 | 480                 |      | no limit | ns               |

| t <sub>SOSCLK</sub> | SDO Timing (see Fig. 12–4)                                                   | 17, 27          | 120                 |      |          | ns               |

| V <sub>I2ICIL</sub> | I <sup>2</sup> C-Bus Input Low Voltage                                       | 3, 4            |                     |      | 0.3      | V <sub>SUP</sub> |

| V <sub>I2ICIH</sub> | I <sup>2</sup> C-Bus Input High Voltage                                      |                 | 0.6                 |      |          | V <sub>SUP</sub> |

| t <sub>I2C1</sub>   | I <sup>2</sup> C-Start Condition Setup Time                                  |                 | 120                 |      |          | ns               |

| t <sub>I2C2</sub>   | I <sup>2</sup> C-Stop Condition Setup Time                                   |                 | 120                 |      |          | ns               |

| t <sub>I2C3</sub>   | I <sup>2</sup> C-Clock Low Pulse Time                                        |                 | 500                 |      |          | ns               |

| t <sub>I2C4</sub>   | I <sup>2</sup> C-Clock High Pulse Time                                       |                 | 500                 |      |          | ns               |

| t <sub>I2C5</sub>   | I <sup>2</sup> C-Data Setup Time before<br>Rising Edge of Clock              |                 | 55                  |      |          | ns               |

| t <sub>I2C6</sub>   | I <sup>2</sup> C-Data Hold Time after<br>Falling Edge of Clock               |                 | 55                  |      |          | ns               |

| f <sub>I2CIH</sub>  | I <sup>2</sup> C-Bus Frequency                                               | 1               |                     |      | 1.0      | MHz              |

## 3.5.3. Characteristics at V\_{SUP} = 4.75 to 5.25 V, $T_{amb}$ = 0 to 65 $^\circ C$

| Symbol              | Parameter                                                                         | Pin No. | Min.                  | Тур. | Max.       | Unit   | Test Conditions                                      |

|---------------------|-----------------------------------------------------------------------------------|---------|-----------------------|------|------------|--------|------------------------------------------------------|

| Р                   | Power Consumption                                                                 |         |                       | 900  | 1100       | mW     | at 40 MHz<br>C <sub>L</sub> = 30 pF on all outputs   |

| V <sub>DOL</sub>    | Data Output Low Voltage                                                           | 1)      |                       |      | 0.6        | V      | $I_{LOAD} = 10 \mu A$                                |

| T <sub>FALL</sub>   | Data Output High to Low<br>Transition Time                                        | 2)      |                       |      | 10         | ns     | $C_L = 50 \text{ pF max}.$                           |

| V <sub>DOH</sub>    | Data Output High Voltage                                                          | 1)      | V <sub>SUP</sub> -0.6 |      |            | V      | I <sub>LOAD</sub> = -10 μA                           |

| T <sub>Rise</sub>   | Data Output High to Low<br>Transition Time                                        | 1)      |                       |      | 10         | ns     | $C_L = 50 \text{ pF max.}$                           |

| V <sub>DOLI</sub>   | I <sup>2</sup> C Output Low Voltage, I <sup>2</sup> C switching hysteresis on POR | 3, 4    |                       |      | 0.4<br>0.6 | V<br>V | I <sub>LOAD</sub> = 3 mA<br>I <sub>LOAD</sub> = 6 mA |

| I <sub>DOHI</sub>   | I <sup>2</sup> C Output High<br>Leakage Current                                   |         | 0                     |      | 2          | μΑ     | V <sub>DOH</sub> = 5 V                               |

| V <sub>RESHYS</sub> | Hysteresis Voltage of POR                                                         | 5       | 160                   | 240  | 320        | mV     |                                                      |

| t <sub>Piw</sub>    | PIO Timing (see Fig. 12–1)                                                        | 13–22,  | 0                     |      |            | ns     |                                                      |

| t <sub>Pie</sub>    | PIO Timing (see Fig. 12–1)                                                        | 28–43   | -25                   | 0    | 25         | ns     | Equal Load Capacitance or EOD, RTR, and RTW          |

| t <sub>Pieset</sub> | PIO Timing (see Fig. 12–1)                                                        |         | 50                    |      |            | ns     | C <sub>L</sub> = 50 pF max.                          |

| t <sub>Pihold</sub> | PIO Timing (see Fig. 12–1)                                                        |         | 50                    |      |            | ns     | $C_L = 5 \text{ pF min.}$                            |

| t <sub>FSIV</sub>   | FSI Timing, (see Fig. 12–2)                                                       | 38      |                       | 22   | 23         | ms     | $C_L = 5 \text{ pF min.}$                            |

| t <sub>FSIP</sub>   | FSI Timing, (see Fig. 12–2)                                                       |         | 23                    | 24   | 25         | ms     | $C_L = 5 \text{ pF min.}$                            |

| t <sub>SOSCLK</sub> | SDO Timing (see Fig. 12–4)                                                        | 17–19,  | 120                   |      |            | ns     |                                                      |

| t <sub>SOISS</sub>  | SDO Timing (see Fig. 12–4)                                                        | 27–29   | 10                    |      |            | ns     |                                                      |

| tSOODC              | SDO TIming (see Fig. 12-4)                                                        |         | 10                    |      |            | ns     |                                                      |

| t <sub>SPCLK</sub>  | SPDIF Timing (see Fig. 12–5)                                                      |         |                       | 325  |            | ns     |                                                      |

## 3.5.4. Recommended Crystal Characteristics

| Symbol              | Parameter                                       | Pin No. | Min. | Тур. | Max. | Unit            |

|---------------------|-------------------------------------------------|---------|------|------|------|-----------------|

| V <sub>XCA</sub>    | External Clock Amplitude                        | 8       | 0.7  |      |      | V <sub>pp</sub> |

| T <sub>Jitter</sub> | Clock Jitter without<br>Timing Recovery Control |         |      |      | 2    | ns              |

| Symbol           | Parameter                                                        | Pin No.     | Min.   | Тур.            | Max.         | Unit     |

|------------------|------------------------------------------------------------------|-------------|--------|-----------------|--------------|----------|

| f <sub>P</sub>   | Parallel Resonance Frequency at 12 pF Load Capacitance           |             |        | 24.576          |              | MHz      |

| f <sub>TOL</sub> | Accuracy of Adjustment                                           |             | -100   |                 | +100         | ppm      |

| D <sub>TEM</sub> | Frequency Variation versus<br>Temperature                        |             | -50    |                 | +50          | ppm      |

| R <sub>R</sub>   | Series Resistance                                                |             |        |                 | 20           | Ω        |

| C <sub>0</sub>   | Shunt (Parallel) Capacitance                                     |             |        |                 | 7.0          | pF       |

| Load Capacit     | ance Recommendations                                             |             |        |                 |              |          |

| CL               | External Load Capacitance*)                                      | 8, 10       | 18     |                 |              | pF       |

| f <sub>CL</sub>  | Required Open Loop Clock<br>Frequency (T <sub>amb</sub> = 25 °C) |             | 24.574 | 24.576          | 24.578       | MHz      |

| *) Remark or     | defining the External Load Capacita                              | ance:       |        |                 |              | •        |

| Extornal conc    | ecitors at each crystal pip to groupd are r                      | aquirad Tha |        | any to tupo the | froo rupping | frequen- |

External capacitors at each crystal pin to ground are required. They are necessary to tune the free running frequency of the DRP or the open-loop frequency of the MSP. The higher the capacitors, the lower the clock frequency results. The nominal free running frequency should match 18.432/24.576 MHz as closely as possible. Due to different layouts of customer PCBs the matching capacitor size should be defined in the application. The suggested values are figures based on experience with various PCB layouts. For adjusting the DRP crystal frequency, use external capacitors with 5% tolerance.

#### 3.5.4.2. Single Crystal Mode – 18.432 MHz at MSP 3400C

| Symbol           | Parameter                                                        | Pin No. | Min.    | Тур.   | Max.    | Unit |  |

|------------------|------------------------------------------------------------------|---------|---------|--------|---------|------|--|

| f <sub>P</sub>   | Parallel Resonance Frequency at 12 pF Load Capacitance           |         |         | 18.432 |         | MHz  |  |

| f <sub>TOL</sub> | Accuracy of Adjustment                                           |         | -30     |        | +30     | ppm  |  |

| D <sub>TEM</sub> | Frequency Variation versus<br>Temperature                        |         | -30     |        | +30     | ppm  |  |

| R <sub>R</sub>   | Series Resistance                                                |         |         | 8      | 25      | Ω    |  |

| C <sub>0</sub>   | Shunt (Parallel) Capacitance                                     |         |         | 6.2    | 7.0     | pF   |  |

| C <sub>1</sub>   | Motional (Dynamic) Capacitance                                   |         | 15      |        |         | fF   |  |

| Load Capacit     | ance Recommendations                                             |         |         |        |         |      |  |

| CL               | External Load Capacitance <sup>*)</sup>                          | 8, 10   | 3.3     | 3.3    |         |      |  |

| f <sub>CL</sub>  | Required Open Loop Clock<br>Frequency (T <sub>amb</sub> = 25 °C) |         | 18.4305 | 18.432 | 18.4335 | MHz  |  |

## 3.5.4.3. Dual Crystal Mode – 18.432/24.576 MHz

| Symbol           | Parameter                                                        | Pin No. | Min.    | Тур.   | Max.    | Unit |

|------------------|------------------------------------------------------------------|---------|---------|--------|---------|------|

| For MSP          |                                                                  |         | •       |        |         |      |

| f <sub>P</sub>   | Parallel Resonance Frequency at 12 pF Load Capacitance           |         |         | 18.432 |         | MHz  |

| f <sub>TOL</sub> | Accuracy of Adjustment                                           |         | -20     |        | +20     | ppm  |

| D <sub>TEM</sub> | Frequency Variation versus<br>Temperature                        |         | -20     |        | +20     | ppm  |

| R <sub>R</sub>   | Series Resistance                                                |         |         | 8      | 25      | Ω    |

| C <sub>0</sub>   | Shunt (Parallel) Capacitance                                     |         |         | 6.2    | 7.0     | pF   |

| C <sub>1</sub>   | Motional (Dynamic) Capacitance                                   |         | 19      | 24     |         | fF   |

| Load Capacit     | ance Recommendations                                             |         |         |        |         |      |

| CL               | External Load Capacitance <sup>*)</sup>                          | 8, 10   | 3.3     |        |         | pF   |

| f <sub>CL</sub>  | Required Open Loop Clock<br>Frequency (T <sub>amb</sub> = 25 °C) |         | 18.431  | 18.432 | 18.433  | MHz  |

| For DRP          |                                                                  |         |         |        |         |      |

| f <sub>P</sub>   | Parallel Resonance Frequency at 12 pF Load Capacitance           |         |         | 24.576 |         | MHz  |

| f <sub>TOL</sub> | Accuracy of Adjustment                                           |         | -20     |        | +20     | ppm  |

| D <sub>TEM</sub> | Frequency Variation versus<br>Temperature                        |         | -20     |        | +20     | ppm  |

| R <sub>R</sub>   | Series Resistance                                                |         |         |        | 20      | Ω    |

| C <sub>0</sub>   | Shunt (Parallel) Capacitance                                     |         |         |        | 7.0     | pF   |

| Load Capacit     | ance Recommendations                                             |         |         |        |         |      |

| CL               | External Load Capacitance*)                                      | 8, 10   | 18      |        |         | pF   |

| f <sub>CL</sub>  | Required Open Loop Clock<br>Frequency (T <sub>amb</sub> = 25 °C) |         | 24.5747 | 24.576 | 24.5773 | MHz  |

| Symbol           | Parameter                                                        | Pin No. | Min.                | Тур.   | Max.   | Unit     |

|------------------|------------------------------------------------------------------|---------|---------------------|--------|--------|----------|

| f <sub>P</sub>   | Parallel Resonance Frequency at 12 pF Load Capacitance           |         |                     | 18.432 |        | MHz      |

| f <sub>TOL</sub> | Accuracy of Adjustment                                           |         | -20                 |        | +20    | ppm      |

| D <sub>TEM</sub> | Frequency Variation versus<br>Temperature                        |         | -20                 |        | +20    | ppm      |

| R <sub>R</sub>   | Series Resistance                                                |         |                     | 8      | 25     | Ω        |

| C <sub>0</sub>   | Shunt (Parallel) Capacitance                                     |         |                     | 6.2    | 7.0    | pF       |

| C <sub>1</sub>   | Motional (Dynamic) Capacitance<br>(at MSP, not required at DRP)  |         | 19                  | 24     |        | fF       |

| Load Capacit     | ance Recommendations                                             |         |                     |        |        |          |

| CL               | External Load Capacitance <sup>*)</sup>                          | 8, 10   | MSP: 3.3<br>DRP: 18 |        |        | pF<br>pF |

| f <sub>CL</sub>  | Required Open Loop Clock<br>Frequency (T <sub>amb</sub> = 25 °C) |         | 18.431              | 18.432 | 18.433 | MHz      |

## 3.5.4.4. Dual Crystal Mode - 18.432/18.432 MHz

## 3.5.5. System Characteristics

| Symbol                 | Parameter                             | Min.  | Тур. | Max. | Unit |

|------------------------|---------------------------------------|-------|------|------|------|

| F <sub>R</sub>         | Covered frequency range for receiving | 0.180 |      | 9.00 | MHz  |

| C/N <sub>clear</sub>   | C/N for error rate < $1*10^{-5}$      |       | 9.5  |      | dB   |

| C/N <sub>Aqu</sub>     | C/N for acquisition                   |       | 8.5  |      | dB   |

| T <sub>rec</sub>       | Lock time                             |       | 0.2  |      | S    |

| F <sub>LockRange</sub> | Carrier Lock Range                    | -2.0  |      | +2.0 | kHz  |

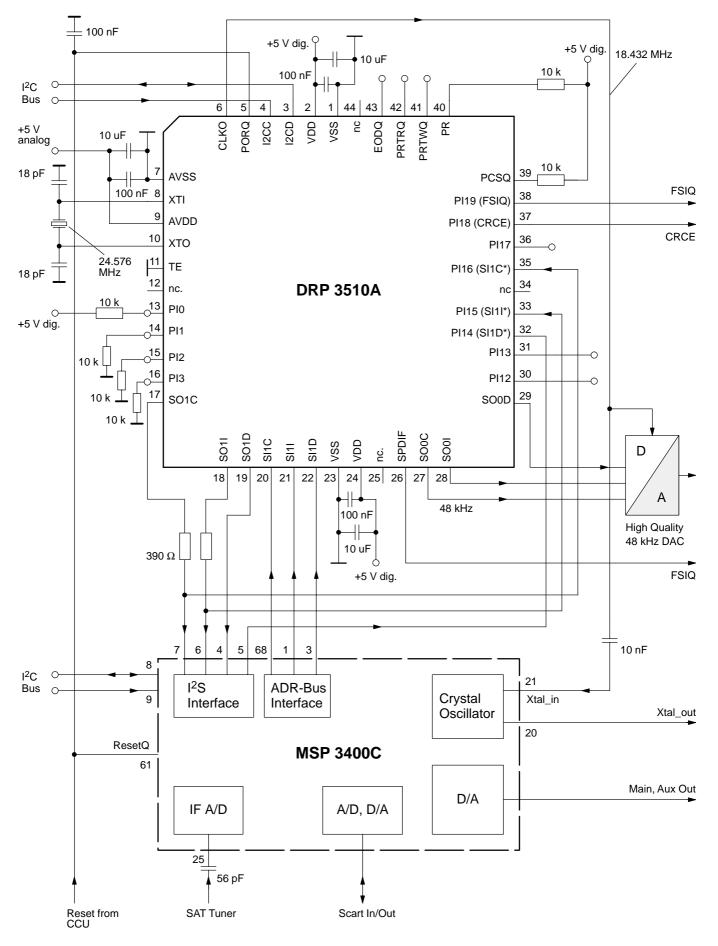

#### 4. Basic Application

The ADR decoder application shows the obligatory parts: MSP 3400C and DRP 3510A. In full transponder mode (48 ADR-channels on one transponder), the tuner output signal should be directly connected with the MSP. In standard mode, the video signal should be suppressed with a highpass filter. The two analog inputs of the MSP can be used for selecting either full-transponder or standard mode. The built-in D/A converter of the MSP generates the analog audio output. Optionally, a 48 kHz D/A converter may be connected to the second I<sup>2</sup>S output interface. The system controlling is done via the I<sup>2</sup>C interface.

Fig. 4–1: ADR/DMX decoder application

#### 5. Clock Concepts

In order to support various applications and board layouts, different clock concepts are supported. Each of the described clock concepts has its advantages. The digital nature of the ADR bit stream forces the decoder IC to synchronize its clock frequency to the symbol rate of the incoming signal. Both the MSP and the DRP clock have to be synchronized, but only the DRP does the timing recovery. The MSP clock is synchronized indirectly with a PLL that locks onto the I<sup>2</sup>S (SO1) signal from the DRP. Thus, the I<sup>2</sup>S feedback connection is mandatory in all ADR applications. See the application recommendations (section 11.) for further details.

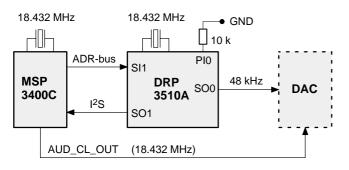

## 5.1. Both MSP and DRP with own crystal running at a 18.432 MHz frequency

The "two crystal mode" is the standard application for the ADR-chip set. Two identical crystals may be used. This mode is preferable in all applications where a considerable physical distance between both ICs is given by the actual board layout.

Fig. 5–1: Two crystal mode

#### Table 5–1: Clock concepts

#### **Clock Concept** 5.1. 5.3. 5.4. 5.2. (I/II) Processor clock 39.936 MHz 36.864 MHz 36.864 MHz 39.936 MHz **Timing recovery** no action required no action required no action required \$200 control register (see 9.6.) Comment less power MSP crystal is 4-bit DAC (48 kHz) omitted, best C/N, consumption is required low crystal spec., less power consumption

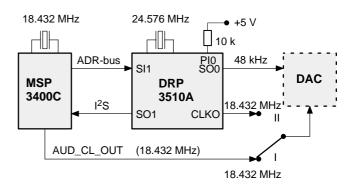

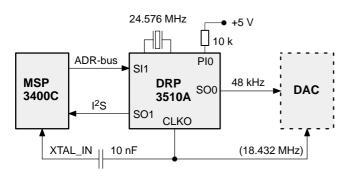

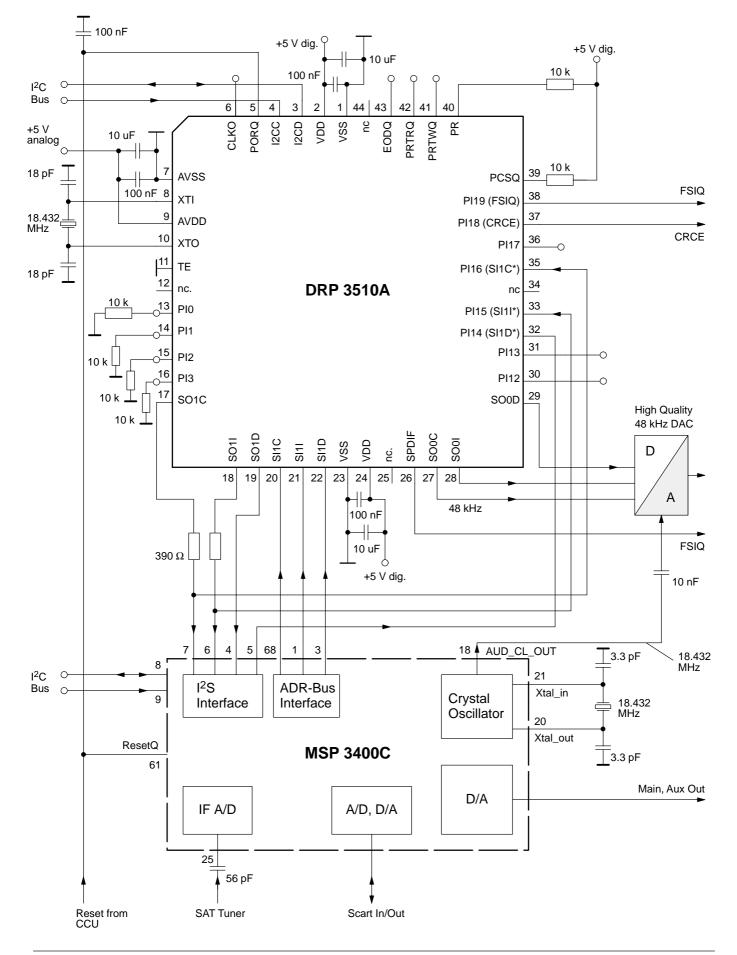

# 5.2. MSP running with a 18.432 MHz crystal, DRP running with a 24.576 MHz crystal

The "two crystal mode" with a 18.432 and a 24.576 MHz crystal leads to a smaller power dissipation (about 10% smaller) for the DRP and makes it possible to derive the oversampling clock for the optional 48 kHz DAC directly from the DRP (position II of the switch in Fig. 5–2).

**Fig. 5–2:** Two crystal mode with 18.432 and 24.576 MHz crystal

#### 5.3. DRP running with a 24.576 MHz crystal, MSP receives its clock from DRP

In this "single crystal mode", the MSP clock is taken from the DRP. This avoids any problems that may arise due to frequency deviations of the crystals. The DRP-PLL works directly without any effects caused by the MSP. So the best C/N performance can be reached. The 24.576 MHz crystal leads to a smaller power dissipation (about 10% smaller) for the DRP. This is the most cost effective solution, because the crystal specification is very low. The oversampling clock for the optional 48 kHz DAC comes directly from the DRP. The NICAM mode of the MSP 3410D is not useable. If the system in this mode is running without an ADR-carrier at the input, the clock will slowly drift to its maximum deviation. The DRP clock can be restored either to its default value by writing the value '0' into the clock-deviation register (see 9.5.) or better with an initialization value according to section 11.5. After a simultaneous hardware reset of MSP and DRP, it is necessary to give the MSP a software reset using an I<sup>2</sup>C-command. A MSP software reset (via I<sup>2</sup>C) is necessary after each reset (by hardware or by I<sup>2</sup>C) of the DRP.

Fig. 5-3: Single-crystal mode with 24.576 MHz

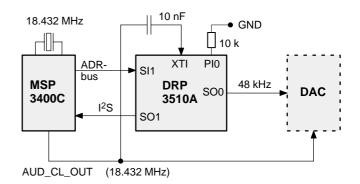

#### 5.4. DRP receives its clock from the MSP

In this "single crystal mode", the DRP clock is taken from the MSP. This avoids any problems that may arise due to frequency deviations of the crystals. However, this mode leads to a more critical symbol-clock recovery. The reference clock of the DRP is generated by the MSP, which again is the base for the DRP system. This causes an integrating system behavior that has to be stabilized by changing some control circuit parameters (write \$200 into timing recovery control register – see 9.6.). If the system in this mode is running without an ADR-carrier at the input, the clock will slowly drift to its maximum deviation. The DRP clock can be restored either to its default value by writing the value '0' into the clock-deviation register (see 9.5.) or better with an initialization value according to section 11.5.

Fig. 5–4: Single crystal mode with 18.432 MHz

#### 6. Interfaces

#### 6.1. The ADR Input Interface

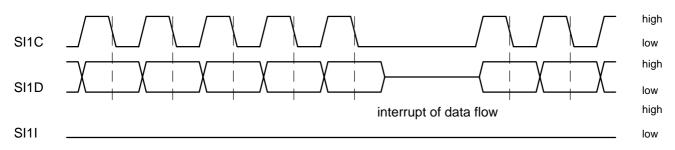

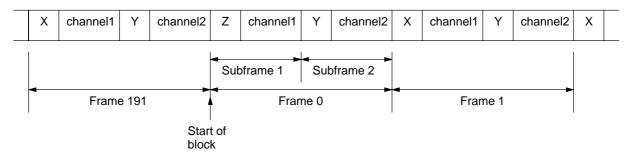

The ADR input lines SI1C, SI1D, and SI1I are designed as a direct interface to the MSP. These lines transport some preprocessed channel-data from the MSP, which are directly used for the channel decoding within the DRP (see the MSP 3400C/D data sheet for connecting the MSP with the DRP). If the Layer 2 mode is selected, the ADR interface expects Layer 2 data instead of ADR data. The format for the L2 data stream is shown in Fig. 6–1. Short interruptions of the data stream are allowed (< 5 ms). However, the mean input data rate must correspond to the data rate that is coded in the MPEG bit stream. It is possible to route the input to SDI1\* by using the input selection register (see 9.12.).

#### 6.2. The SDO0 Interface

The SDO0 interface passes the decoded 48 kHz audio signal e.g. to a high quality D/A converter. The serial format generates 2\*32 bits for stereo audio samples on the data line SO0D, a word strobe SO0I, and a serial clock at the SOOC line. The first 18 bits of each mono-sample contain valid data, bit 19 and bit 20 are always set to zero. The 12 trailing bits are determined by the content of the SO0AUXA (left) and SO0AUXB (right) registers. Some high quality DACs do need an oversampled clock signal. If the DRP is working with a 24.576 MHz crystal, the oversampled clock may be taken from the CLKOUT pin of the DRP. If working with a 18.432 MHz crystal, the oversampled clock has to be taken from the MSP-clockout. In the 18.432 MHz MSP single crystal mode, the external DAC should not be a 1-bit converter. This is to prevent clock jitter effects caused by the timing recovery.

Fig. 6-2: Schematic timing of the SDO0 output interface

#### 6.3. The SDO1 Interface

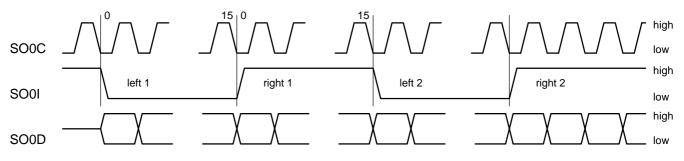

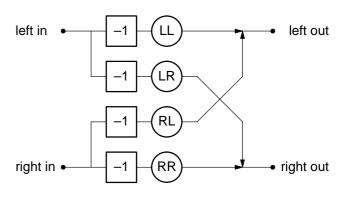

The SDO1 interface sends a decoded 32 kHz audio signal back to the MSP. The 32 kHz signal is generated via an internal high quality sample rate converter, which is perfectly matched to the performance of the MSP DACs. The cutoff frequency now is reduced to approximately 15 kHz. The signal of most of the free to air ADR-stations, however, does not exceed this cutoff frequency. The serial format generates 2\*16 bits for stereo audio samples on the data line SO1D, a word strobe on the SO1I, and a serial clock at the SO1C line. This offers the opportunity to use the MSPC DACs for analog output. This connection to the MSPC is obligatory for every application, even if it is not intended to use the MSPC DACs. This is due to the fact that the clock synchronization between DRP and MSP uses this connection. The timing of the SDO1 interface is shown in Fig. 6-3.

#### 6.4. The PIO Interface

The PIO interface can be used in two different modes. In the standard mode, the PIO lines PIO..PI3 are used to select the crystal frequency or to switch between different applications; and the PI12..PI19 lines are used as signalling outputs or serial interface pins (see section 3.2.). In a second mode, the DMA mode (direct memory access), the internal MPEG Layer 2 data stream (after descrambling but before decoding) is provided on the PIO lines PI12..PI19.

#### 6.4.1. General Purpose PIO Mode

The general purpose PIO mode is selected after reset. In this mode, the PIO-lines have the functionality as described below. The PIO and PI3 pins are only read out after a reset of the DRP.

Fig. 6–3: Schematic timing of the SDO1 output interface

|   | PI0               | PI1 | PI2 | PI3             | PI14      | PI15                                         | PI16            | PI18                  | PI19               |

|---|-------------------|-----|-----|-----------------|-----------|----------------------------------------------|-----------------|-----------------------|--------------------|

|   | crystal<br>select |     |     | Mode<br>select  | SI1D*     | SI1I*                                        | SI1C*           | CRCE                  | FSI (def.<br>mode) |

| 0 | 18.432            |     |     | ADR             | (for exam | e input lines<br>ple: I <sup>2</sup> S to SI | no CRC<br>error | anc.data<br>available |                    |

| 1 | 24.576            |     |     | L2 de-<br>coder |           | combinatior<br>ed software)                  | CRC<br>error    | anc.data<br>invalid   |                    |

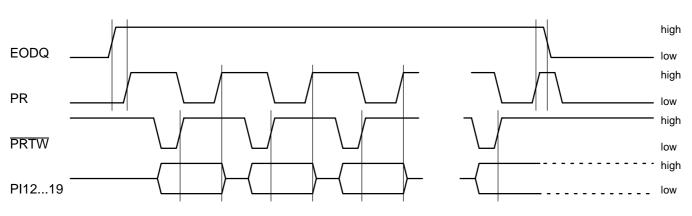

#### 6.4.2. PIO-DMA Mode

The PIO-DMA mode is selected by setting the corresponding bit in the main configuration register 96. The PIO-DMA mode gives access to the undecoded data, which are simultaneously sent to the integrated MPEG Layer 2 decoder. In this mode, PIO lines PIO...PI3 and PI12...PI19 are switched to output. The PIO lines PI12...PI19 will give an 8-bit parallel access to the bit stream data. The data is always sent in packets of 16 bytes every 0.667 ms. The data are 8-bit aligned with MSB first (at position PI19). The MPEG data are aligned in such a way that the first bit of the MPEG header is always positioned at the MSB (PI19) of the 8-bit word. In order to read out the data stream, a special handshake protocol must be used (see Fig. 6–4).

The data transfer is started after the EODQ-pin of the DRP is set to an active state. After checking this, the controller requests data by activating the PR-line. The DRP asserts that the first data word is placed on the bus by generating a negative strobe impulse on PRTW. Now, the controller may read the data word, and subsequently, it may request the next byte by activating the PR-line again. This procedure will be repeated 16 times. After the 17th PR impulse of the controller, the EODQ signal of the DRP will be activated, which indicates that the transfer of one data block has been finalized. The data for one 16-byte block is transmitted in 0.6 ms. However, the complete protocol should be executed in less than 0.5 ms to avoid data loss. A description of timing details can be found in section 12.1. This PIO-DMA mode will not work in the E4 version (see also section 13).

#### 6.5. The SP/DIF Interface

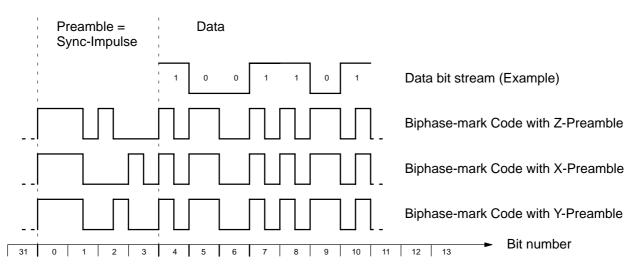

The SP/DIF interface generates a 48, 44.1, or 32 kHz digital signal conforming to the IEC 958 consumer stan-

dard. In ADR mode, only 48 kHz sampling frequencies are generated. The interface definition covers the data stream and the physical timing specifications of the data transmission. The transmission is done via the "biphase-mark" code (Fig. 6–5).

The SP/DIF signal consists of 32-bit subframes. The first 4 bits are used for the sync impulse (Preambles). There are three different sync signals: The first subframe normally starts with preamble "X". However, the preamble changes to preamble "Z" once every 192 frames. "Z" also indicates the block begin, which is used to organize the channel status information. The second subframe always starts with preamble "Y". (see Fig 6–7). Two subframes form one frame, 192 frames are collected into one super-frame (or block). The preamble is followed by 4 auxiliary bits, which are not used in this application (forced to 0), and 20 data bits. A subframe will be completed with the validity bit, user bit, channel status bit, and parity bit (see Fig 6–6).

#### 6.6. Copy Protection

The copy protection mode is set either according to the incoming MPEG bit stream or explicitly to "no copy allowed" regardless of the copy protection setting of the MPEG bit stream. The copy protection mode is selectable by setting bit 8 in the main configuration register. In the default mode (bit 8 = 0), the copy bit of the MPEG bit stream that is set by the service provider is directly evaluated to set the copy protection within the SPDIF output bit stream. If copy protection is coded in the MPEG header, one can record the program, but a further digital copy of the recorded material is not allowed. If no copy protection is coded in the MPEG header, a digital copy is allowed. The copy protection can be forced regardless of the copy protection setting in the MPEG bit stream by setting the main configuration register (bit 8 = 1).

Fig. 6-4: Handshake protocol for getting MPEG data via PIO-DMA

Fig. 6–5: Preamble and biphase-mark code specification (polarity may be changed)

| 0 3      | 4   | 7   | 8   |                          | 27  | 28              | 29               | 30                    | 31            |

|----------|-----|-----|-----|--------------------------|-----|-----------------|------------------|-----------------------|---------------|

| Preamble | 0 0 | 0 0 | LSB | 20-bit audio sample word | MSB | Validity<br>Bit | User data<br>Bit | Channel<br>status Bit | Parity<br>Bit |

#### Fig. 6-6: Subframe format

Fig. 6-7: Frame format

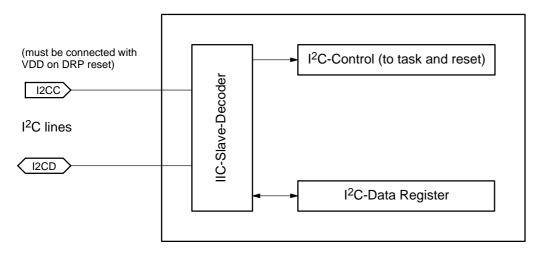

### 7. The I<sup>2</sup>C Interface

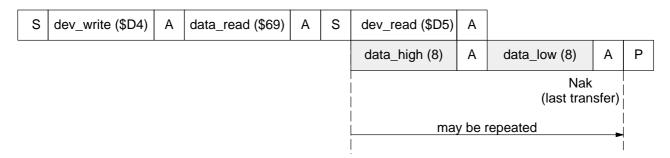

Device address: 1101010X (\$D4 (dev\_write), \$D5 dev\_read)) Slave-Subaddresses: 01101000 (\$68) subaddress write 01101001 (\$69) subaddress read 01101010 (\$6A) control

#### 7.1. The I<sup>2</sup>C-Data Register

The I<sup>2</sup>C-Data Register is used to communicate with the internal firmware of the DRP. It has a length of 16 bits. The data transfer is done with the MSB first. The following table shows the bit assignment used in this document.

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|-----|

| msb |     |     |     |     |     |    |    |    |    |    |    |    |    |    | lsb |

#### 7.2. The I<sup>2</sup>C-Control Register

The I<sup>2</sup>C-Control Register is used to set the tasks to switch between different operating modes and to generate a hardware reset.

If the reset bit is set to "1", the DRP will stay in the "reset" state. This  $I^2C$  reset will affect all blocks of the DRP but

not the I<sup>2</sup>C-interface itself. Thus, writing a new word into the control register with the reset bit 8 cleared, will restart the processor. If the task bits T0...T3 are set, the corresponding tasks in the DRP are set permanently. The bits C4...C7 must always be set to "0". If no bit is set, the DRP will work in its default mode, which is ADR-decoding. Task 3 corresponds to the Layer 2 only decoder.

| C15           | C14 | C13 | C12 | C11 | C10 | C9         | C8 | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |

|---------------|-----|-----|-----|-----|-----|------------|----|----|----|----|----|----|----|----|----|

| reserved bits |     |     |     |     |     | Re-<br>set | 0  | 0  | 0  | 0  | Т3 | T2 | T1 | Т0 |    |

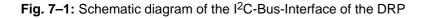

#### 7.3. The I<sup>2</sup>C Protocol

A data transfer via I<sup>2</sup>C is always initiated by an external controller with a start condition on the I<sup>2</sup>C bus. Then, the controller sends the device address and the subaddress. The value of the subaddress specifies the direction of the following data transfer. The subaddresses \$68 and \$6A indicate a transfer from the controller to the DRP, the subaddress \$69 indicates a transfer from the DRP to the controller. The transfer is continued until a stop condition is transmitted by the controller.

Fig. 7-2: Timing of start (S) and stop (P) condition of the I<sup>2</sup>C protocol

#### 7.3.1. Controller Writes to the DRP Control Register

| S | dev_write (\$D4) | A | control_adr (\$6a) | А | control_high (8) | А | control_low (8) | А | Ρ |

|---|------------------|---|--------------------|---|------------------|---|-----------------|---|---|

|---|------------------|---|--------------------|---|------------------|---|-----------------|---|---|

Fig. 7–3: Writing a control word into the control register

#### 7.3.2. Controller Writes to the DRP Data Register

| S | dev_write (\$D4) | А | data_write (\$68) | А | data_high (8) | А | data_low (8) | А | Ρ |  |

|---|------------------|---|-------------------|---|---------------|---|--------------|---|---|--|

|---|------------------|---|-------------------|---|---------------|---|--------------|---|---|--|

Fig. 7-4: Writing a 16-bit word into the data register

#### 7.3.3. Controller Reads from the DRP Data Register

Fig. 7-5: Reading 16-bit data word(s) from the data register

#### MICRONAS INTERMETALL

#### 7.4. The I<sup>2</sup>C Commands

The following commands are used to communicate with the DRP-firmware. The commands are executed by the DRP during the normal operation without any interruptions of the audio signal. These I<sup>2</sup>C commands do allow an external system controller to access all internal states, RAM contents, and even the internal hardware control registers. This may be very useful for special purpose application and non standard operation modes. Note: Writing values into not documented internal DRP registers or RAM-cells may corrupt the decoding process and may lead to unpredictable processor states, which can be left only by a hardware reset of the whole system. The description of the various  $I^2C$  commands uses the following formalism: A value is split into nibbles, which are numbered beginning with 0 for the least significant nibble. The data values or the nibbles are written in hexadecimal notation indicated by a preceding \$ character. A hexadecimal number is written, for example, as d=\$17C63. The 5 nibbles of this number are d0=\$3, d1=\$6, d2=\$C, d3=\$7, d4=\$1. Register addresses are called **r**, data values are called **d**, addresses **a**, and a count value is called **n**. If a fixed number is to be used, it is listed directly preceded by a \$-sign.

#### 7.4.1. Write into a DRP Register

| S | dev_write (\$D4) | А | data_write (\$68) | А | \$9 r1 | А | r0 d0 |   |   |

|---|------------------|---|-------------------|---|--------|---|-------|---|---|

|   |                  | - |                   | А | d4 d3  | А | d2 d1 | А | Ρ |

**Fig. 7–6:** Write a 20-bit value **d**=(d4,d3,d2,d1,d0) into register **r** = (r1,r0)

The DRP has an address space of 256 registers, 128 of them in the D0-area and 128 in the D1-area. Some of the registers are direct control inputs for various hardware blocks, others do control the internal program flow. In the next section, those registers that may be changed by the system controller are described in detail.  $\Delta$  Writing random values into undocumented registers may corrupt the execution of the program.

#### 7.4.2. Default Read Command

| S | dev_write (\$D4) | Α | data_read (\$69) | А | s | dev_read (\$D5) | А |       |     |   |  |

|---|------------------|---|------------------|---|---|-----------------|---|-------|-----|---|--|

|   |                  |   |                  |   |   | status          | А | index | Nak | Р |  |

Fig. 7-7: Default read of a 16-bit word (status and index) from the DRP

The status and index values are described in section 8.1.

#### 7.4.3. Read From a DRP Register

| S | dev_write (\$D4) | А | data_write (\$68)  | А   |   | \$d r1          | А |        | r0 \$0 | А   | Ρ |  |

|---|------------------|---|--------------------|-----|---|-----------------|---|--------|--------|-----|---|--|

|   |                  |   | 2. get register va | lue |   |                 |   |        |        |     |   |  |

| S | dev_write (\$D4) | А | data_read (\$69)   | А   | S | dev_read (\$D5) |   |        |        |     |   |  |

|   |                  |   | d3 d2              |     | А | d1 d0           |   | A      |        |     |   |  |

|   |                  |   |                    |     |   | \$xx            | А | \$x d4 |        | Nak | Р |  |

1. send command

Fig. 7–8: Reading a 20-bit value from a DRP register

#### 7.4.4. Get ADR Data

|      |                                            |   | 1. send comman                    | nd |   |              |      |     |             |    |   |  |

|------|--------------------------------------------|---|-----------------------------------|----|---|--------------|------|-----|-------------|----|---|--|

| S    | dev_write (\$D4)                           | А | data_write (\$68)                 | A  |   | \$60         | А    | of  | fset count  | А  | Р |  |

|      |                                            |   | 2. get data                       |    |   |              |      |     |             |    |   |  |

| S    | dev_write (\$D4)                           | А | data_read (\$69)                  | Α  | S | dev_read (\$ | SD5) | А   |             |    |   |  |

|      |                                            |   |                                   |    |   | status       |      | А   | index       |    | А |  |

|      | et: first value to b                       |   | ad (\$0\$9)<br>o be read (\$1\$a) |    |   | adr0         |      | А   | adr1        |    | А |  |

| Read | the complete data                          |   |                                   | •  |   | adr2         |      | А   | adr3        |    | А |  |

|      | t = 0, count = \$a<br>d only control data: |   |                                   |    |   | adr4         |      | А   | adr5        |    | А |  |

|      | t = 8, count = 2                           |   |                                   |    |   | adr6         |      | А   | adr7        |    | А |  |

|      |                                            |   |                                   |    |   | adr8         |      | А   | adr9        |    | А |  |

|      |                                            |   |                                   |    |   | adr10        |      | А   | adr11       |    | А |  |

|      |                                            |   |                                   |    |   | adr12        |      | А   | adr13       |    | А |  |

|      |                                            |   |                                   |    |   | adr14        |      | А   | adr15 (ctrl | 0) | А |  |

|      |                                            |   | adr16 (ctrl                       | 1) | А | adr17 (ctrl  | 2)   | Nak | Ρ           |    |   |  |

Fig. 7-9: Reading the status, index, and the 18 bytes of ADR-data from the DRP

The 18 bytes of the ADR data will be updated every 24 ms. The content of this data field is documented in the ADR-specification. These data are already deinter-leaved and error corrected. The last three bytes do always keep the control data. The meaning of the first 15 bytes may change due to different services. In order to optimize the access to the ADR data, a simple selection mechanism has been implemented where the offset and

the number of word to be read could be selected. It is important that this command is always completed, i.e. the number of words passed by "count" to the DRP has to be read by the controller, otherwise the operation system may crash. The MSB of control byte 1, which indicates that the auxiliary and RDS data in the frame are complemented, will be processed internally according to the "free to air" standard. Thus, this bit is always set to zero, indicating that the inversion of the control data must not be done by the controller. In case of DMX, the meaning of the MSB of control byte 1 is inverted, so that the controller always has to complement the auxiliary and RDS data.

#### 7.4.5. Write DMX Data

| S   | dev_write (\$D4)                         | А      | data_wr | te (\$ | 668) | А | \$50 | A | \$00 | А |   |

|-----|------------------------------------------|--------|---------|--------|------|---|------|---|------|---|---|

|     |                                          |        |         |        |      |   | dmx1 | A | dmx0 | А |   |

|     | : 8 dmx bytes (dmx<br>eceived from the v |        |         |        |      |   | dmx3 | A | dmx2 | А |   |

| Whe | n writing these by<br>start with dmx     | tes to | o the   |        |      |   | dmx5 | Α | dmx4 | А |   |

|     | ng dmx0 etc.                             |        |         |        |      |   | dmx7 | Α | dmx6 | А | Р |

Fig. 7-10: Send 8 bytes to DRP for DMX data decryption

#### 7.4.6. Write Data into the D0-Memory of the DRP