# Contents

| Page | Section  | Title                                                        |

|------|----------|--------------------------------------------------------------|

| 4    | 1.       | Introduction                                                 |

| 5    | 1.1.     | Features of the DPL 4519G                                    |

| 6    | 1.2.     | Application Fields of the DPL 4519G                          |

| 7    | 2.       | Functional Description                                       |

| 7    | 2.1.     | Architecture of the DPL 4519G Family                         |

| 8    | 2.2.     | Preprocessing I <sup>2</sup> S Input Signals                 |

| 8    | 2.3.     | Selection of Internal Processed Surround Signals             |

| 8    | 2.4.     | Source Selection and Output Channel Matrix                   |

| 8    | 2.5.     | Audio Baseband Processing                                    |

| 8    | 2.5.1.   | Main and Aux Outputs                                         |

| 8    | 2.6.     | Surround Processing                                          |

| 8    | 2.6.1.   | Surround Processing Mode                                     |

| 8    | 2.6.1.1. | Decoder Matrix                                               |

| 9    | 2.6.1.2. | Surround Reproduction                                        |

| 9    | 2.6.1.3. | Center Modes                                                 |

| 9    | 2.6.1.4. | Useful Combinations of Surround Processing Modes             |

| 10   | 2.6.2.   | Examples                                                     |

| 11   | 2.6.3.   | Application Tips for using 3D-PANORAMA                       |

| 11   | 2.6.3.1. | Sweet Spot                                                   |

| 11   | 2.6.3.2. | Clipping                                                     |

| 11   | 2.6.3.3. | Loudspeaker Requirements                                     |

| 11   | 2.6.3.4. | Cabinet Requirements                                         |

| 11   | 2.6.4.   | Input and Output Levels for Dolby Surround Pro Logic         |

| 11   | 2.7.     | SCART Signal Routing                                         |

| 11   | 2.7.1.   | SCART Out Select                                             |

| 12   | 2.7.2.   | Stand-by Mode                                                |

| 12   | 2.8.     | I <sup>2</sup> S Bus Interfaces                              |

| 12   | 2.8.1.   | Synchronous I <sup>2</sup> S-Interface(s)                    |

| 12   | 2.8.2.   | Asynchronous I <sup>2</sup> S-Interface                      |

| 12   | 2.8.3.   | Multichannel I <sup>2</sup> S-Output                         |

| 12   | 2.8.4.   | Asynchronous Multichannel I <sup>2</sup> S-Input             |

| 13   | 2.9.     | Digital Control I/O Pins                                     |

| 13   | 2.10.    | Clock PLL Oscillator and Crystal Specifications              |

| 14   | 3.       | Control Interface                                            |

| 14   | 3.1.     | I <sup>2</sup> C Bus Interface                               |

| 14   | 3.1.1.   | Device and Subaddresses                                      |

| 14   | 3.1.2.   | Internal Hardware Error Handling                             |

| 15   | 3.1.3.   | Description of CONTROL Register                              |

| 15   | 3.1.4.   | Protocol Description                                         |

| 16   | 3.1.5.   | Proposals for General DPL 4519G I <sup>2</sup> C Telegrams   |

| 16   | 3.1.5.1. | Symbols                                                      |

| 16   | 3.1.5.2. | Write Telegrams                                              |

| 16   | 3.1.5.3. | Read Telegrams                                               |

| 16   | 3.1.5.4. | Examples                                                     |

| 16   | 3.2.     | Start-Up Sequence: Power-Up and I <sup>2</sup> C Controlling |

# Contents, continued

| Page | Section  | Title                                                            |

|------|----------|------------------------------------------------------------------|

| 16   | 3.3.     | DPL 4519G Programming Interface                                  |

| 16   | 3.3.1.   | User Registers Overview                                          |

| 19   | 3.3.2.   | Description of User Registers                                    |

| 19   | 3.3.2.1. | Write Registers on I <sup>2</sup> C Subaddress 10 <sub>hex</sub> |

| 21   | 3.3.2.2. | Read Registers on I <sup>2</sup> C Subaddress 11 <sub>hex</sub>  |

| 21   | 3.3.2.3. | Write Registers on I <sup>2</sup> C Subaddress 12 <sub>hex</sub> |

| 33   | 3.3.2.4. | Read Registers on I <sup>2</sup> C Subaddress 13 <sub>hex</sub>  |

| 34   | 3.4.     | Programming Tips                                                 |

| 34   | 3.5.     | Examples of Minimum Initialization Codes                         |

| 34   | 3.5.1.   | Micronas Dolby Digital chipset (with MAS 3528E)                  |

| 35   | 4.       | Specifications                                                   |

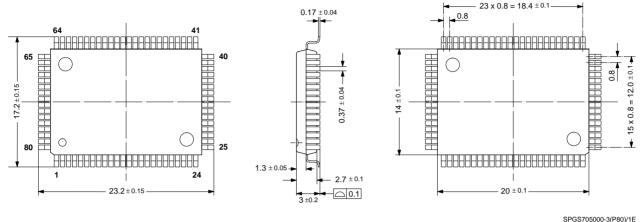

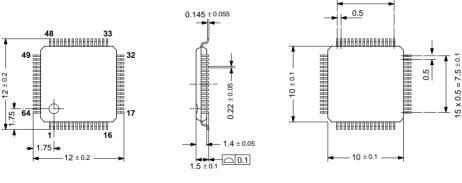

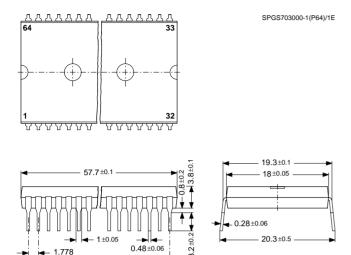

| 35   | 4.1.     | Outline Dimensions                                               |

| 37   | 4.2.     | Pin Connections and Short Descriptions                           |

| 40   | 4.3.     | Pin Descriptions                                                 |

| 43   | 4.4.     | Pin Configurations                                               |

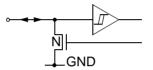

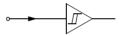

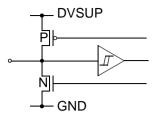

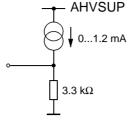

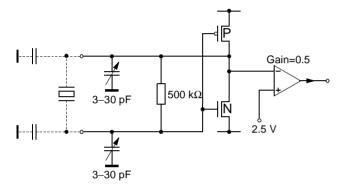

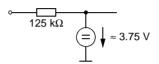

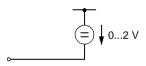

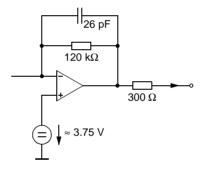

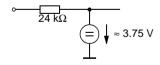

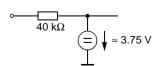

| 45   | 4.5.     | Pin Circuits                                                     |

| 47   | 4.6.     | Electrical Characteristics                                       |

| 47   | 4.6.1.   | Absolute Maximum Ratings                                         |

| 48   | 4.6.2.   | Recommended Operating Conditions (T <sub>A</sub> = 0 to 70 °C)   |

| 48   | 4.6.2.1. | General Recommended Operating Conditions                         |

| 48   | 4.6.2.2. | Analog Input and Output Recommendations                          |

| 49   | 4.6.2.3. | Crystal Recommendations                                          |

| 50   | 4.6.3.   | Characteristics                                                  |

| 50   | 4.6.3.1. | General Characteristics                                          |

| 51   | 4.6.3.2. | Digital Inputs, Digital Outputs                                  |

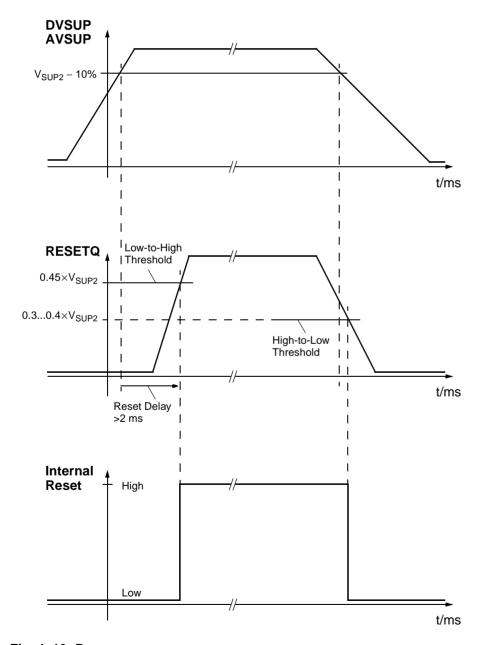

| 52   | 4.6.3.3. | Reset Input and Power-Up                                         |

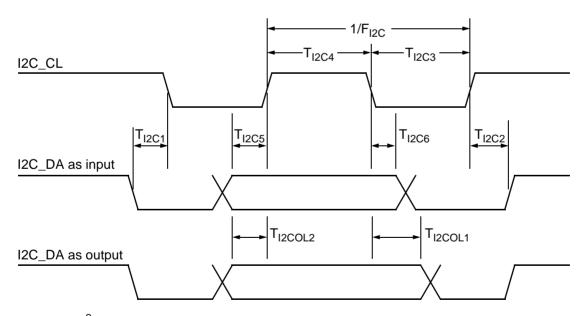

| 53   | 4.6.3.4. | I <sup>2</sup> C-Bus Characteristics                             |

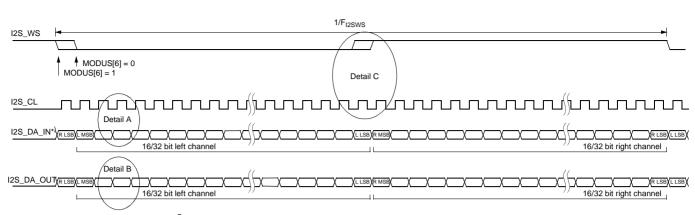

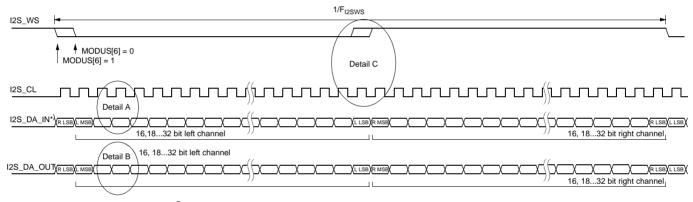

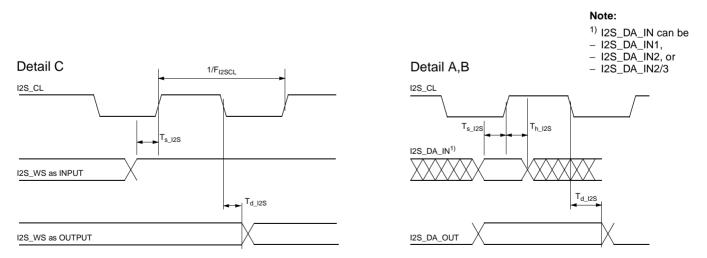

| 54   | 4.6.3.5. | I <sup>2</sup> S-Bus Characteristics                             |

| 56   | 4.6.3.6. | Analog Baseband Inputs and Outputs, AGNDC                        |

| 58   | 4.6.3.7. | Power Supply Rejection                                           |

| 58   | 4.6.3.8. | Analog Performance                                               |

| 61   | 5.       | Appendix A: Application Information                              |

| 61   | 5.1.     | Phase Relationship of Analog Outputs                             |

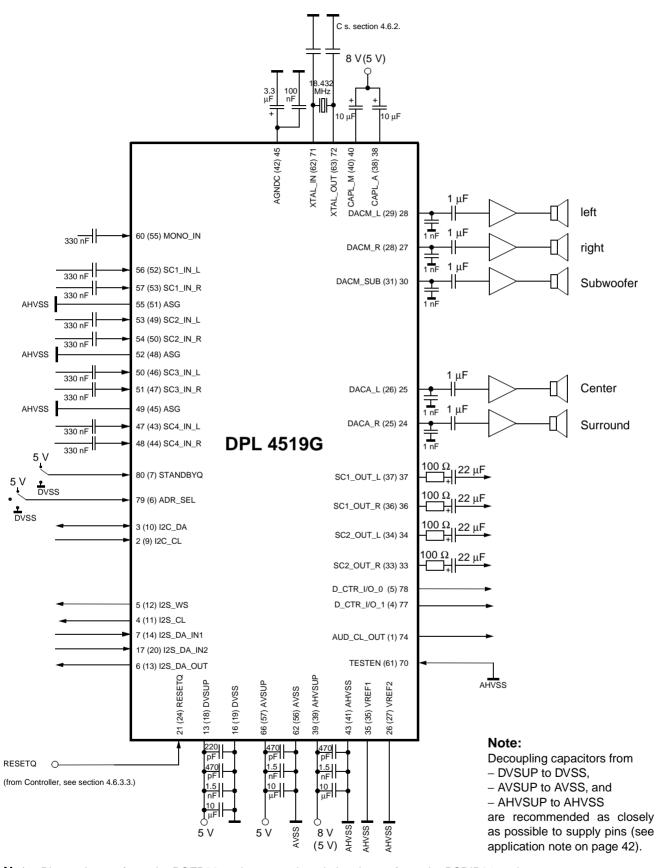

| 62   | 5.2.     | Application Circuit                                              |

| 64   | 6.       | Data Sheet History                                               |

# License Notice:

Supply of this implementation of Dolby Technology does not convey a license nor imply a right under any patent, or any other industrial or intellectual property right of Dolby Laboratories, to use this implementation in any finished end-user or ready-to-use final product. Companies planning to use this implementation in products must obtain a license from Dolby Laboratories Licensing Corporation before designing such products.

<sup>&</sup>quot;Dolby Pro Logic" and "Dolby Digital" are trademarks of Dolby Laboratories.

# Sound Processor for Digital and Analog Surround Systems

The hardware and software description in this document is valid for the DPL 4519G version A1 and following versions.

#### 1. Introduction

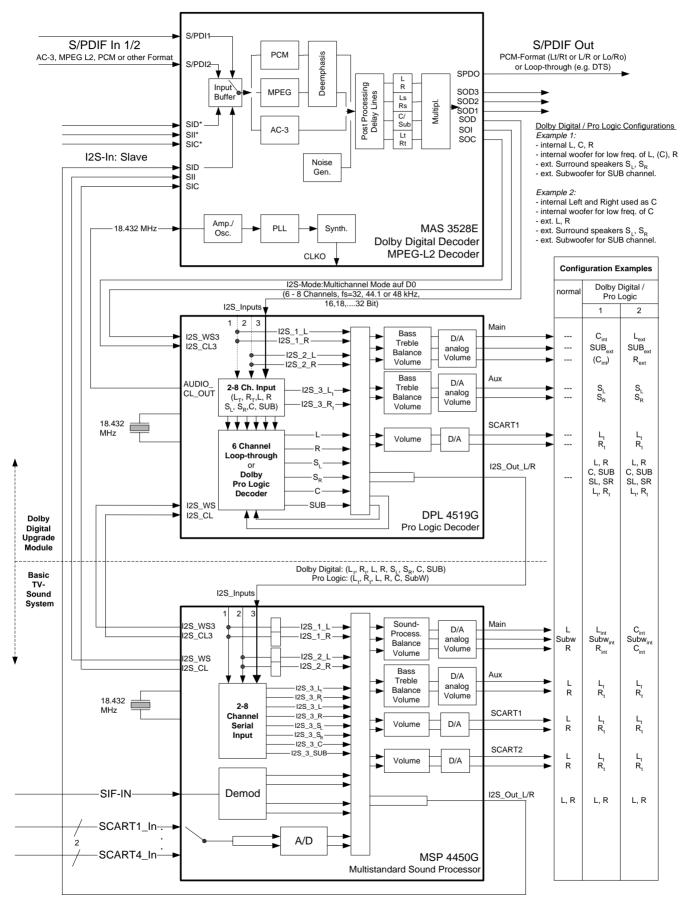

The DPL 4519G processor is designed as part of the Micronas chip set for digital and analog Surround Systems i. e. Dolby Digital, MPEG 2 Audio, or Dolby ProLogic. The combination of MAS 3528E, DPL 4519G, and MSP 44x0G is a complete 5.1 channel Dolby Digital decoder and playback solution, while DPL 4519G and MSP 44x0G alone, represent a complete Dolby Surround Pro Logic system.

The DPL 4519G receives its incoming data via highly flexible I<sup>2</sup>S interfaces. The three I<sup>2</sup>S input interfaces can be configured as three asynchronous I<sup>2</sup>S inputs or two synchronous and one asynchronous interface. In the latter case, the asynchronous interface allows reception of 2-8 channels with arbitrary sample rate ranging from 8 to 48 kHz. The synchronization is performed by means of an adaptive high-quality sample rate converter.

In an application together with the Dolby Digital decoder MAS 3528E, eight channels (left, right, surround left, surround right, center, subwoofer, Pro Logic encoded left, Pro Logic encoded right) are fed in and processed in the DPL 4519G.

Similar to the multichannel I<sup>2</sup>S input interface, the DPL is provided with an 8-channel I<sup>2</sup>S output interface, which can be connected to a MSP 44x0G. Therefore all 8 channels can be routed to each output in both ICs.

The baseband processing including e.g. balance, bass, treble, and loudness is performed at a fixed sample rate of 48 kHz.

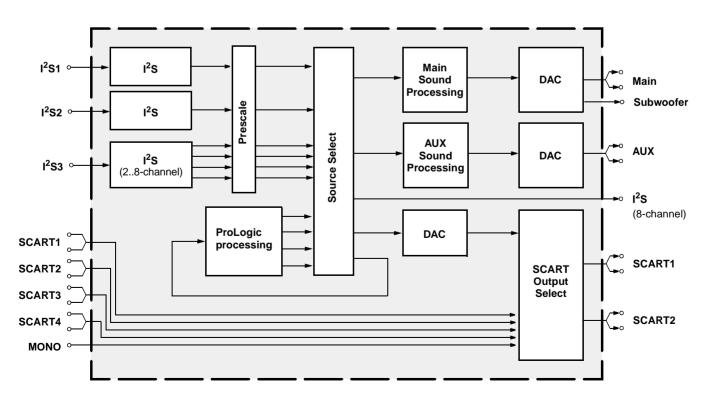

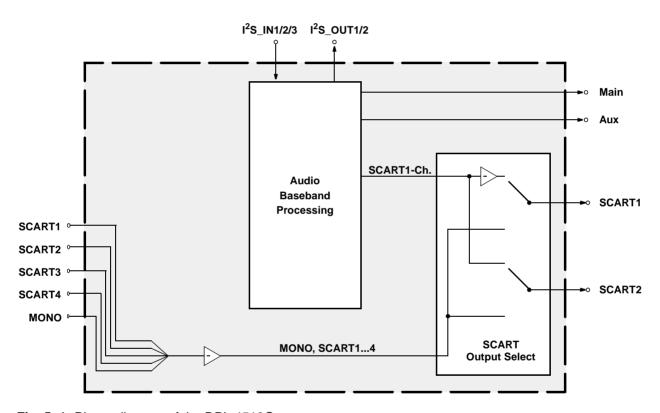

Fig. 1–1 shows a simplified functional block diagram of the DPL 4519G.

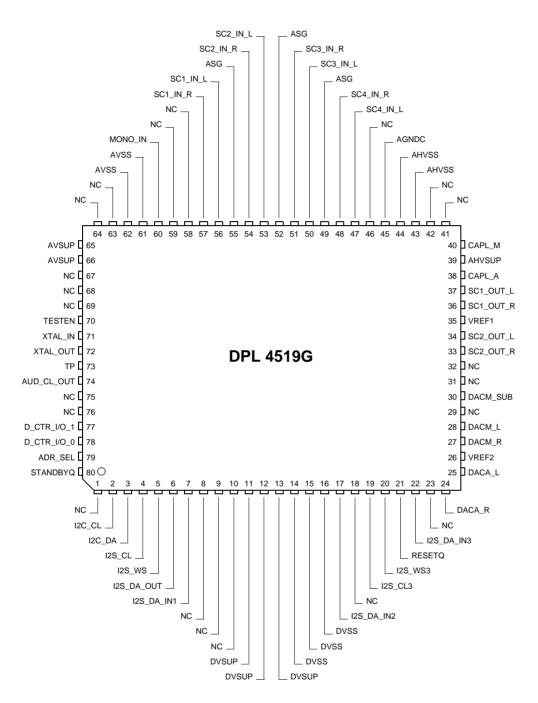

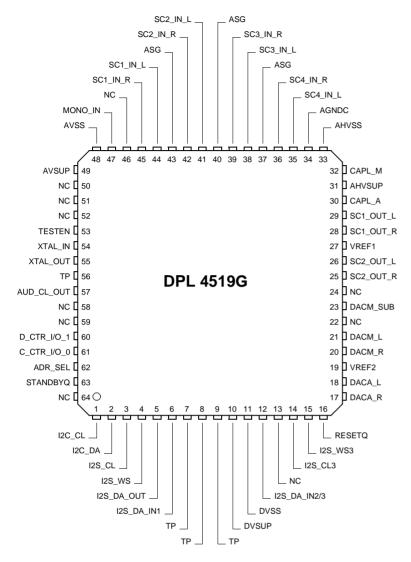

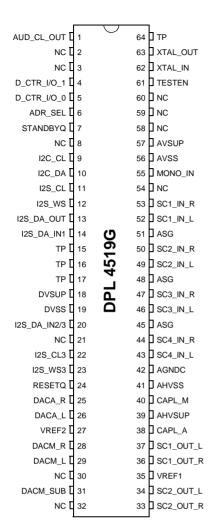

The DPL 4519G is pin-compatible to members of the MSP 34xx family. This speeds up PCB development for customers using MSPs.

The software interface of the DPL 4519G is also largely the same as for members of the MSP family.

The ICs are produced in submicron CMOS technology and are available in PQFP80, PLQFP64 and in PSDIP64 packages.

Micronas

Fig. 1-1: Simplified block diagram of the DPL 4519G

4

PRELIMINARY DATA SHEET DPL 4519G

#### 1.1. Features of the DPL 4519G

- 8-channel asynchonous I<sup>2</sup>S input interface (multichannel mode)

- + 2 synchronous I<sup>2</sup>S input channels (e.g. for MSP and ADR)

#### or

- 3 asynchronous two-channel I<sup>2</sup>S input interfaces

- Main and AUX channel with balance, bass, treble, loudness, volume

- 5-band graphic equalizer for Main channel

- Dolby Surround Pro Logic Adaptive Matrix

- Micronas Effect Matrix

- Micronas "3D-Panorama" virtualizer compliant to "Virtual Dolby Surround" technology

- Micronas Panorama sound mode (3D Surround sound via two loudspeakers)

- Noise Generator

- Spatial Effect for Surround

- 30-ms Surround delay

- Surround matrix control: Adaptive/Passive/Effect

- Center mode control: Normal/Phantom/Wide/Off

- Surround reproduction control: Rear speaker, Front speaker, Panorama, 3D-Panorama

- Two digital input/output pins controlled by I<sup>2</sup>C bus

Fig. 1–2 shows a typical Dolby Digital application using DPL 4519G, MSP 4450G, and MAS 3528E.

#### 1.2. Application Fields of the DPL 4519G

Fig. 1-2: Typical DPL 4519G application

# 2. Functional Description

# 2.1. Architecture of the DPL 4519G Family

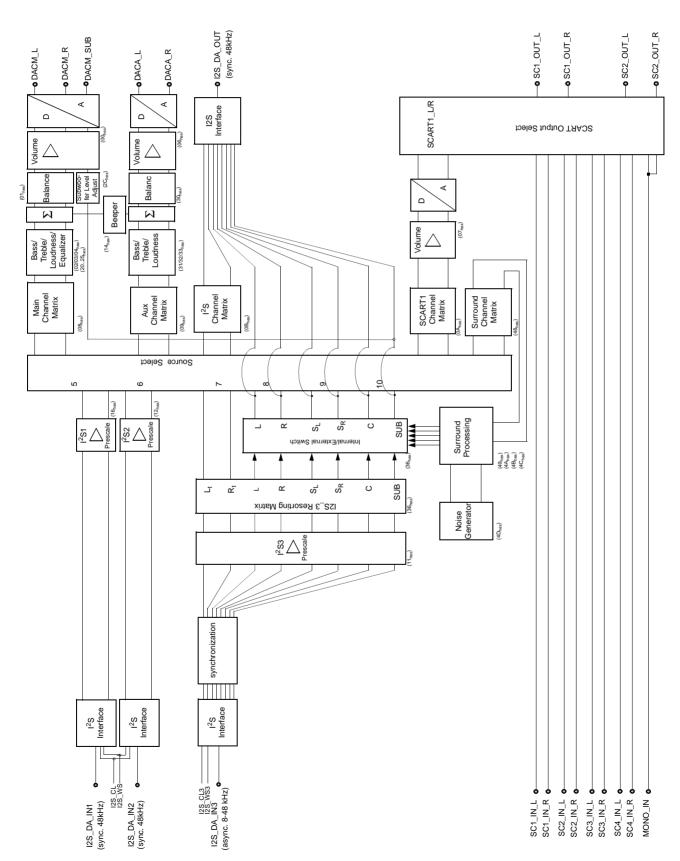

Fig. 2-1 shows a simplified block diagram of the IC.

Fig. 2-1: Signal flow block diagram of the DPL 4519G (input and output names correspond to pin names)

DPL 4519G PRELIMINARY DATA SHEET

# 2.2. Preprocessing I<sup>2</sup>S Input Signals

The I<sup>2</sup>S inputs can be adjusted in level by means of the I<sup>2</sup>S prescale registers.

The I<sup>2</sup>S<sub>\_3</sub> interface is able to receive more than two channels (see Section 2.6. on page 8). The incoming signals can be resorted by a programmable matrix in order to obtain a certain order, which means an unified postprocessing afterwards.

Since the I<sup>2</sup>S<sub>3</sub> interface is asynchronous, incoming sound signals with arbitrary sample rates in the range of 8-48 kHz are interpolated to 48 kHz by means of an adaptive high quality sample rate converter. Therefore all subsequent processing is calculated on a fixed sampling rate, which even can be synchronized to I2S<sub>WS</sub> e.g. to a MSP 4450 being locked to an incoming NICAM signal.

# 2.3. Selection of Internal Processed Surround Signals

Instead of having an multichannel input via the I<sup>2</sup>S\_3 interface, a multichannel signal can be created by an internal Dolby Pro Logic decoder. In that case channels 3..8 of the multichannel input are replaced by the internally generated signals.

#### 2.4. Source Selection and Output Channel Matrix

The Source Selector makes it possible to distribute all source signals (I<sup>2</sup>S input signals) to the desired output channels (Main, Aux, etc.). All input and output signals can be processed simultaneously. Each source channel is identified by a unique source address.

For each output channel, the output channel matrix can be set to sound A (left mono), sound B (right mono), stereo, or mono (sound left and right).

# 2.5. Audio Baseband Processing

#### 2.5.1. Main and Aux Outputs

The following baseband features are implemented in the Main and Aux output channels: bass/treble, loudness, balance, and volume. A square wave beeper can be added to these outputs. The Main channel additionally supports an equalizer function (this is not simultaneously available with bass/treble).

#### 2.6. Surround Processing

#### 2.6.1. Surround Processing Mode

Surround sound processing is controlled by three functions:

The "Decoder Matrix" defines which method is used to create a multichannel signal (L, C, R, S) out of a stereo input.

The "Surround Reproduction" determines whether the surround signal "S" is fed to surround speakers. If no surround speaker is actually connected, it defines the method that is used to create surround effects.

The "Center Mode" determines how the center signal "C" is to be processed. It can be left unmodified, distributed to left and right, discarded or high pass filtered, whereby the low pass signals are distributed to left and right.

#### 2.6.1.1. Decoder Matrix

The Decoder Matrix allows three settings:

#### - ADAPTIVE:

The Adaptive Matrix is used for Dolby Surround Pro Logic. Even sound material not encoded in Dolby Surround will produce good surround effects in this mode. The use of the Adaptive Matrix requires a license from Dolby Laboratories (See License Notice on page 3).

#### - PASSIVE:

A simple fixed matrix is used for surround sound.

#### - FFFFCT

A fixed matrix that is used for mono sound and special effects. With Adaptive or Passive Matrix no surround signal is present in case of mono, moreover in Adaptive mode even the left and right output channels carry no signal (or just low frequency signals in case of Center Mode = NORMAL). If surround sound is still required for mono signals, the Effect Matrix can be used. This forces the surround channel to be active. The Effect Matrix can be used together with 3D-PANORAMA. The result will be a pseudo stereo effect or a broadened stereo image respectively.

#### 2.6.1.2. Surround Reproduction

Surround sound can be reproduced with four choices:

#### - REAR SPEAKER:

If there are any surround speakers connected to the system, this mode should be used. Useful loud-speaker combinations are (L, C, R, S) or (L, R, S).

#### - FRONT SPEAKER:

If there is no surround speaker connected, this mode can be used. Surround information is mixed to left and right output but without creating the illusion of a virtual speaker. It is similar to stereo but an additional center speaker can be used. This mode should be used with the Adaptive decoder Matrix only. Useful loudspeaker combinations are (L, C, R) (Note: the surround output channel is muted).

#### - PANORAMA:

The surround information is mixed to left and right in order to create the illusion of a virtual surround speaker. Useful loudspeaker combinations are (L, C, R) or (L, R) (Note: the surround output channel is muted).

#### - 3D-PANORAMA:

Like PANORAMA with improved effect. This algorithm has been approved by the Dolby Laboratories for compliance with the "Virtual Dolby Surround" technology. Useful loudspeaker combinations are (L, C, R) or (L, R) (Note: the surround output channel is muted).

#### 2.6.1.3. Center Modes

Four center modes are supported:

#### – NORMAL:

small center speaker connected, L and R speakers have better bass capability. Center signal is high pass filtered.

# - WIDE:

L, R, and C speakers all have good bass capability.

#### - PHANTOM:

No center speaker used. Center signal is distributed to L and R (Note: the center output channel C is muted).

#### - OFF:

No center speaker used. Center signal C is discarded (Note: the center output channel C is muted).

#### 2.6.1.4. Useful Combinations of Surround Processing Modes

In principle, "Decoder Matrix", "Surround Reproduction", and "Center Modes" are independent settings (all "Decoder Matrix" settings can be used with all "Surround Reproduction" and "Center Modes") but there are some combinations that do not create "good" sound. Useful combinations are

#### **Surround Reproduction and Center Modes**

#### - REAR SPEAKER:

This mode is used if surround speakers are available. Useful center modes are NORMAL, WIDE, PHANTOM, and OFF.

#### - FRONT SPEAKER:

This mode can be used if no surround speaker but a center speaker is connected. Useful center modes are NORMAL and WIDE.

#### PANORAMA or 3D-PANORAMA:

No surround speaker used. Two (L and R) or three (L, R, and C) loudspeakers can be used. Useful center modes are NORMAL, WIDE, PHANTOM, and OFF.

#### **Center Modes and Decoder Matrix**

#### - PHANTOM:

Should only be used together with ADAPTIVE Decoder Matrix.

#### - NORMAL and WIDE:

Can be used together with any Surround Decoder Matrix.

#### - OFF:

This mode can be used together with the PASSIVE and EFFECT Decoder Matrix (no center speaker connected).

# 2.6.2. Examples

Table 2-1 shows some examples of how these modes can be used to configure the IC. The list is not intended to be complete, more modes are possible.

Table 2-1: Examples of Surround Configurations

| Configurations                                | Speaker<br>Config-<br>uration <sup>1)</sup> | Surround Proc<br>Register (4B <sub>hex</sub> ) | essing Mode                       |                      |

|-----------------------------------------------|---------------------------------------------|------------------------------------------------|-----------------------------------|----------------------|

|                                               |                                             | Decoder Matrix<br>[15:8]                       | Surround<br>Reproduction<br>[7:4] | Center Mode<br>[3:0] |

| Stereo                                        |                                             |                                                |                                   |                      |

| Stereo                                        | (L,R)                                       | -                                              | _                                 | _                    |

| Surround Modes as defined by Dolby Laboratori | es <sup>2)</sup>                            |                                                |                                   |                      |

| Dolby Surround Pro Logic                      | (L,C,R,S)                                   | ADAPTIVE                                       | REAR_<br>SPEAKER                  | NORMAL<br>WIDE       |

|                                               | (L,R,S)                                     | ADAPTIVE                                       | REAR_<br>SPEAKER                  | PHANTOM              |

| Dolby 3 Stereo                                | (L,C,R)                                     | ADAPTIVE                                       | FRONT_<br>SPEAKER                 | NORMAL<br>WIDE       |

| Virtual Dolby Surround                        | (L,R)                                       | ADAPTIVE                                       | 3D_PANORAMA                       | PHANTOM              |

| Surround Modes that use the Dolby Adaptive Ma | ıtrix <sup>2)</sup>                         |                                                |                                   |                      |

| 3-Channel Virtual Surround                    | (L,C,R)                                     | ADAPTIVE                                       | 3D_PANORAMA                       | NORMAL<br>WIDE       |

| Passive Matrix Surround Sound                 |                                             |                                                |                                   |                      |

| 4-Channel Surround                            | (L,C,R,S)                                   | PASSIVE                                        | REAR_<br>SPEAKER                  | NORMAL<br>WIDE       |

| 3-Channel Surround                            | (L,R,S)                                     | PASSIVE                                        | REAR_<br>SPEAKER                  | OFF                  |

| 2-Channel Micronas 3D Surround Sound (MSS)    | (L,R)                                       | PASSIVE                                        | 3D_PANORAMA                       | OFF                  |

| 3-Channel Micronas 3D Surround Sound (MSS)    | (L,C,R)                                     | PASSIVE                                        | 3D_PANORAMA                       | NORMAL<br>WIDE       |

| Special Effects Surround Sound                |                                             |                                                |                                   |                      |

| 4-Channel Surround for mono                   | (L,C,R,S)                                   | EFFECT                                         | REAR_<br>SPEAKER                  | NORMAL<br>WIDE       |

| 2-Channel Virtual Surround for mono           | (L,R)                                       | EFFECT                                         | 3D_PANORAMA                       | OFF                  |

| 3-Channel Virtual Surround for mono           | (L,C,R)                                     | EFFECT                                         | 3D_PANORAMA                       | NORMAL<br>WIDE       |

<sup>1)</sup> Speakers not in use are muted automatically.

2) The implementation in products requires a license from Dolby Laboratories Licensing Corporation (see note on page 3).

PRELIMINARY DATA SHEET DPL 4519G

#### 2.6.3. Application Tips for using 3D-PANORAMA

#### 2.6.3.1. Sweet Spot

Good results are only obtained in a rather close area along the middle axis between the two loudspeakers: the sweet spot. Moving away from this position degrades the effect.

# 2.6.3.2. Clipping

For the test at Dolby Labs, it is very important to have no clipping effects even with worst case signals. The  $I^2S$ -prescale register has to be set to values of max  $10_{hex}$  ( $16_{dec}$ ). This is sufficient in terms of clipping.

However, it was found, that by reducing the prescale to a value lower than  $16_{dec}$  more convincing effects are generated in case of very high dynamic signals. A value of  $10_{dec}$  is a good compromise between overall volume and additional headroom.

Test signals: sine sweep with 0 dBFS; L only, R only, L&R equal phase, L&R anti phase.

Listening tests: Dolby Trailers (train trailer, city trailer, canyon trailer...)

#### 2.6.3.3. Loudspeaker Requirements

The loudspeakers used and their positioning inside the TV set will greatly influence the performance of the virtualizer. The algorithm works with the direct sound path. Reflected sound waves reduce the effect. So it's most important to have as much direct sound as possible, compared to indirect sound.

To obtain the approval for a TV set, Dolby Laboratories require mounting the loudspeakers at the front of the set. Loudspeakers radiating to the side of the TV set will not produce convincing effects. Good directionality of the loudspeakers towards the listener is optimal.

The virtualizer was specially developed for implementation in TV sets. Even for rather small stereo TV's, sufficient sound effects can be obtained. For small sets, the loudspeaker placement should be to the side of the CRT; for large screen sets (or 16:9 sets), mounting the loudspeakers below the CRT is acceptable (large separation is preferred, low frequency speakers should be outmost to avoid cancellation effects). Using external loudspeakers with a large stereo base will not create optimal effects.

The loudspeakers should be able to reproduce a wide frequency range. The most important frequency range starts from 160 Hz and ranges up to 5 kHz.

Great care has to be taken with systems that use one common subwoofer: A single loudspeaker cannot reproduce virtual sound locations. The crossover frequency must be lower than 120 Hz.

#### 2.6.3.4. Cabinet Requirements

During listening tests at Dolby Laboratories, no resonances in the cabinet should occur.

Good material to check for resonances are the Dolby Trailers or other dynamic sound tracks.

## 2.6.4. Input and Output Levels for Dolby Surround Pro Logic

The nominal input level (input sensitivity) for the  $I^2S$ -Inputs is -15 dBFS. The highest possible input level of 0 dBFS is accepted without internal overflow. The  $I^2S$ -prescale value should be set to values of max 0 dB ( $16_{dec}$ ).

With higher prescale values lower input sensitivities can be accommodated. A higher input sensitivity is not possible, because at least 15 dB headroom is required for every input according to the Dolby specifications.

A full-scale left only input (0 dBFS) will produce a full-scale left only output (at 0 dB volume). The typical output level is 1.37 Vrms for DACM\_L. The same holds true for right only signals (1.37 Vrms for DACM\_R). A full-scale input level on both inputs (Lin=Rin=0 dBFS) will give a center only output with maximum level. A full-scale input level on both inputs (but Lin and Rin with inverted phases) will give a surround-only signal with maximum level.

For reproducing Dolby Pro Logic according to its specifications, the center and surround outputs must be amplified by 3 dB with respect to the L and R output signals. This can be done in two ways:

- 1. By implementing 3 dB more amplification for center and surround loudspeaker outputs.

- By always selecting volume for L and R 3 dB lower than center and surround. Method 1 is preferable, as method 2 lowers the achievable SNR for left and right signals by 3 dB.

#### 2.7. SCART Signal Routing

### 2.7.1. SCART Out Select

The SCART Output Select block includes full matrix switching facilities. The switches are controlled by the ACB user register (see page page 30).

DPL 4519G PRELIMINARY DATA SHEET

#### 2.7.2. Stand-by Mode

If the DPL 4519G is switched off by first pulling STANDBYQ low and then (after >1  $\mu$ s delay) switching off DVSUP and AVSUP, but keeping AHVSUP ('**Standby'-mode**), the SCART switches maintain their position and function. This allows the copying from selected SCART-inputs to SCART-outputs in the TV set's stand-by mode.

In case of power on or starting from stand-by (see details on the power-up sequence in Fig. 4–19 on page 52), all internal registers except the ACB register (page 30) are reset to the default configuration (see Table 3–5 on page 17). The reset position of the ACB register becomes active after the first  $I^2C$  transmission into the Baseband Processing part (subaddress  $12_{\rm hex}$ ). By transmitting the ACB register first, the reset state can be redefined.

#### 2.8. I<sup>2</sup>S Bus Interfaces

The DPL 4519G has two kinds of interfaces: synchron master/slave input/output interfaces running on 48 kHz and an asynchron slave interface.

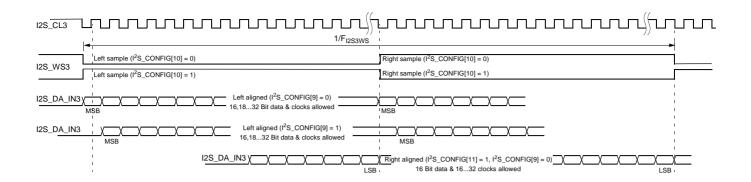

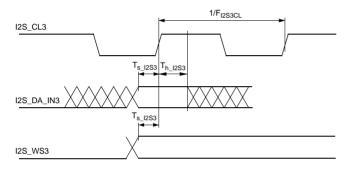

The interfaces accept a variety of formats with different sample width, bit-orientation, and wordstrobe timing. All  $I^2S$  options are set by means of the MODUS or  $I^2S$ \_CONFIG register.

# 2.8.1. Synchronous I<sup>2</sup>S-Interface(s)

The synchronous I<sup>2</sup>S bus interface consists of the pins:

- I2S\_DA\_IN1, I2S\_DA\_IN2/3 (I2S\_DA\_IN2 in PQFP80 package):

I<sup>2</sup>S serial data input, 16, 18...32 bits per sample.

- I2S\_DA\_OUT:

I<sup>2</sup>S serial data output, 16, 18...32 bits per sample.

- I2S\_CL:

I<sup>2</sup>S serial clock.

- I2S\_WS:

I<sup>2</sup>S word strobe signal defines the left and right sample.

If the DPL 4519G serves as the master on the  $I^2S$  interface, the clock and word strobe lines are driven by the DPL 4519G. In this mode, only 16, 32 bits per sample can be selected. In slave mode, these lines are input to the DPL 4519G and the DPL 4519G clock is synchronized to 384 times the  $I^2S$ \_WS rate (48 kHz). An  $I^2S$  timing diagram is shown in Fig. 4–21 on page 55.

# 2.8.2. Asynchronous I<sup>2</sup>S-Interface

The asynchronous I<sup>2</sup>S slave interface allows the reception of digital audio signals with arbitrary sample rates from 5 to 50 kHz. The synchronization is performed by means of an adaptive sample rate converter. No oversampling clock is required.

The following pins are used for the asynchronous I<sup>2</sup>S bus interface (serve only as input):

- I2S WS3

- I2S CL3

- I2S\_DA\_IN2/3 (I2S\_DA\_IN3 in PQFP80 package).

The interface accepts I<sup>2</sup>S-input streams with MSB first and with sample widths of 16,18...32 bits. With left/right alignment and wordstrobe timing polarity, there are additional parameters available for the adaption to a variety of formats in the I2S CONFIGURATION register.

# 2.8.3. Multichannel I<sup>2</sup>S-Output

Bit[0:1] of the I2S CONFIGURATION register (see page 20) switches the output to 8 channel multichannel output mode. The bit resolution per channel is 32 bit in master mode. While the first two channels can be selected on the source select matrix, channels 3-8 are always connected to the I2S\_3 input channels 3-8. Both, master and slave mode is possible, as long as as the wordstrobe has only one positive edge per frame in slave mode.

# 2.8.4. Asynchronous Multichannel I<sup>2</sup>S-Input

The DPL 4519G supports two kinds of asynchronous multichannel input:

- the asynchronous I2S\_3 interface can be switched to multichannel mode (bit [8] of the I2S CONFIGU-RATION register is set to 1. The number of channels must be even and less or equal eight.

- All I2S input lines (I2S\_DA\_IN1, I2S\_DA\_IN2 and I2S\_DA\_IN3 in PQFP80 package) can be switched to asynchronous two channel mode (bit[2] set to 1 in the I2S CONFIGURATION register). The common clock is I2S\_WS3 and I2S\_CL3. No synchronous I2S interfaces are available in this mode.

### 2.9. Digital Control I/O Pins

The static level of the digital input/output pins D\_CTR\_I/O\_0/1 is switchable between HIGH and LOW via the I<sup>2</sup>C-bus by means of the ACB register (see page 30). This enables the controlling of external hardware switches or other devices via I<sup>2</sup>C-bus.

The Modus Register can set the digital input/output pins to high impedance (see page 19). So the pins can be used as input. The current state can be read out of the STATUS register (see page page 21).

# 2.10. Clock PLL Oscillator and Crystal Specifications

The DPL 4519G derives all internal system clocks from the 18.432 MHz oscillator. In I<sup>2</sup>S-slave mode of the synchronous interface, the clock is phase-locked to the corresponding source.

For proper performance, the DPL clock oscillator requires a 18.432-MHz crystal. Note that for the phase-locked modes (I<sup>2</sup>S-slave), crystals with tighter tolerance are required. The asynchronous I<sup>2</sup>S3 slave interface uses a different locking mechanism and does not require tighter crystal tolerances.

#### 3. Control Interface

### 3.1. I<sup>2</sup>C Bus Interface

#### 3.1.1. Device and Subaddresses

The DPL 4519G is controlled via the I<sup>2</sup>C bus slave interface.

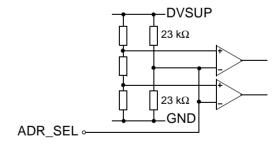

The IC is selected by transmitting one of the DPL 4519G device addresses. In order to allow up to three DPL or MSP ICs to be connected to a single bus, an address select pin (ADR\_SEL) has been implemented. With ADR\_SEL pulled to high, low, or left open, the DPL 4519G responds to different device addresses. A device address pair is defined as a write address and a read address (see Table 3–1).

Writing is done by sending the device write address, followed by the subaddress byte, two address bytes, and two data bytes. Reading is done by sending the write device address, followed by the subaddress byte and two address bytes. Without sending a stop condition, reading of the addressed data is completed by sending the device read address and reading two bytes of data. Refer to Section 3.1.4. for the I<sup>2</sup>C bus protocol and to Section 3.4. "Programming Tips" on page 34 for proposals of DPL 4519G I<sup>2</sup>C telegrams. See Table 3–2 for a list of available subaddresses.

Besides the possibility of hardware reset, the DPL can also be reset by means of the RESET bit in the CONTROL register by the controller via I<sup>2</sup>C bus.

Due to the internal architecture of the DPL 4519G, the IC cannot react immediately to an I<sup>2</sup>C request. The

typical response time is about 0.3 ms. If the DPL cannot accept another complete byte of data until it has performed some other function (for example, servicing an internal interrupt), it will hold the clock line I2C\_CL LOW to force the transmitter into a wait state. The positions within a transmission where this may happen are indicated by "Wait" in Section 3.1.4. The maximum wait period of the DPL during normal operation mode is less than 1 ms.

#### 3.1.2. Internal Hardware Error Handling

In case of any internal hardware error (e.g. interruption of the power supply of the DPL), the DPL's wait period is extended to 1.8 ms. After this time period elapses, the DPL releases data and clock lines.

#### Indicating and solving the error status:

To indicate the error status, the remaining acknowledge bits of the actual I<sup>2</sup>C-protocol will be left high. Additionally, bit[14] of CONTROL is set to one. The DPL can then be reset via the I<sup>2</sup>C bus by transmitting the reset condition to CONTROL.

#### Indication of reset:

Any reset, even caused by an unstable reset line etc., is indicated in bit[15] of CONTROL.

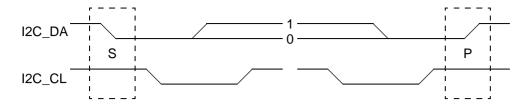

A general timing diagram of the  $I^2C$  bus is shown in Fig. 4–21 on page 55.

Table 3-1: I<sup>2</sup>C Bus Device Addresses

| ADR_SEL            |                   | ow<br>d to DVSS)  |                   | gh<br>l to DVSUP) | Left Open         |                   |  |

|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|

| Mode               | Write             | Read              | Write             | Read              | Write             | Read              |  |

| DPL device address | 80 <sub>hex</sub> | 81 <sub>hex</sub> | 84 <sub>hex</sub> | 85 <sub>hex</sub> | 88 <sub>hex</sub> | 89 <sub>hex</sub> |  |

Table 3-2: I<sup>2</sup>C Bus Subaddresses

| Name    | Binary Value | Hex Value | Mode       | Function                                                                        |

|---------|--------------|-----------|------------|---------------------------------------------------------------------------------|

| CONTROL | 0000 0000    | 00        | Read/Write | Write: Software reset of DPL (see Table 3–3) Read: Hardware error status of DPL |

| WR_DEM  | 0001 0000    | 10        | Write      | write address demodulator                                                       |

| RD_DEM  | 0001 0001    | 11        | Write      | read address demodulator                                                        |

| WR_DSP  | 0001 0010    | 12        | Write      | write address DSP                                                               |

| RD_DSP  | 0001 0011    | 13        | Write      | read address DSP                                                                |

# 3.1.3. Description of CONTROL Register

# Table 3-3: CONTROL as a Write Register

| Name    | Subaddress | Bit[15] (MSB)           | Bits[14:0] |

|---------|------------|-------------------------|------------|

| CONTROL | 00 hex     | 1 : RESET<br>0 : normal | 0          |

# Table 3-4: CONTROL as a Read Register (only DPL 4519G-versions from A2 on)

| Name                                                                                                                | Subaddress | Bit[15] (MSB)                                                                      | Bit[14]                                                                         | Bits[13:0]      |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|--|--|--|

| CONTROL                                                                                                             | 00 hex     | Reset status after last reading of CONTROL: 0 : no reset occured 1 : reset occured | Internal hardware status:<br>0 : no error occured<br>1 : internal error occured | not of interest |  |  |  |

| Reading of CONTROL will reset the bits[15.14] of CONTROL After Power-on, bit[15] of CONTROL will be set: it must be |            |                                                                                    |                                                                                 |                 |  |  |  |

Reading of CONTROL will reset the bits[15,14] of CONTROL. After Power-on, bit[15] of CONTROL will be set; it must be read once to be resetted.

# 3.1.4. Protocol Description

#### Write to DSP

| Ī | S | write   | Wait | ACK | sub-addr | ACK | addr-byte | ACK | addr-byte | ACK | data-byte- | ACK | data-byte | ACK | Р |

|---|---|---------|------|-----|----------|-----|-----------|-----|-----------|-----|------------|-----|-----------|-----|---|

|   |   | device  |      |     |          |     | high      |     | low       |     | high       |     | low       |     | 1 |

|   |   | address |      |     |          |     |           |     |           |     |            |     |           |     | l |

# Read from DSP

| s | write   | Wait | ACK | sub-addr | ACK | addr-byte | ACK | addr-byte | ACK | S | read    | Wait | ACK | data-byte- | ACK | data-byte | NAK | Р |  |

|---|---------|------|-----|----------|-----|-----------|-----|-----------|-----|---|---------|------|-----|------------|-----|-----------|-----|---|--|

|   | device  |      |     |          |     | high      |     | low       |     |   | device  |      |     | high       |     | low       |     |   |  |

|   | address |      |     |          |     | _         |     |           |     |   | address |      |     | _          |     |           |     |   |  |

|   |         |      |     |          |     |           |     |           |     |   |         |      |     |            |     |           |     |   |  |

#### Write to Control

| S | write<br>device | ACK | sub-addr | ACK | data-byte<br>high | ACK | data-byte<br>low | ACK | Р |   |

|---|-----------------|-----|----------|-----|-------------------|-----|------------------|-----|---|---|

|   | address         |     |          |     |                   |     |                  |     | İ | l |

#### Read from Control

| S | write<br>device | Wait | ACK | 00hex | ACK | S | read<br>device | Wait | ACK | data-byte-<br>high | ACK | data-byte<br>low | NAK | Р |

|---|-----------------|------|-----|-------|-----|---|----------------|------|-----|--------------------|-----|------------------|-----|---|

|   | address         |      |     |       |     |   | address        |      |     | 9                  |     |                  |     |   |

**Note:**  $S = I^2C$ -Bus Start Condition from master

$P = I^2C$ -Bus Stop Condition from master

ACK = Acknowledge-Bit: LOW on I2C\_DA from slave (= DPL, light gray) or master (= controller dark gray)

NAK = Not Acknowledge-Bit: HIGH on I2C\_DA from master (dark gray) to indicate 'End of Read'

or from DPL indicating internal error state

Wait =  $I^2$ C-Clock line is held low, while the DPL is processing the  $I^2$ C command.

This waiting time is max. 1 ms

Fig. 3–1: I<sup>2</sup>C bus protocol (MSB first; data must be stable while clock is high)

# 3.1.5. Proposals for General DPL 4519G I<sup>2</sup>C Telegrams

#### 3.1.5.1. Symbols

| daw | write device address (80 <sub>hex</sub> , 84 <sub>hex</sub> or 88 <sub>hex</sub> ) |

|-----|------------------------------------------------------------------------------------|

| dar | read device address (81 <sub>hex</sub> , 85 <sub>hex</sub> or 89 <sub>hex</sub> )  |

| <   | Start Condition                                                                    |

| >   | Stop Condition                                                                     |

| aa  | Address Byte                                                                       |

| dd  | Data Byte                                                                          |

# 3.1.5.2. Write Telegrams

| <daw 00="" d0=""></daw>       | write to CONTROL register   |

|-------------------------------|-----------------------------|

| <daw 10="" aa="" dd=""></daw> | write data into demodulator |

| <daw 12="" aa="" dd=""></daw> | write data into DSP         |

# 3.1.5.3. Read Telegrams

| <daw< th=""><th>00</th><th><da< th=""><th>ar c</th><th>dd dd:</th><th>&gt;</th><th></th><th>read data from</th></da<></th></daw<>             | 00 | <da< th=""><th>ar c</th><th>dd dd:</th><th>&gt;</th><th></th><th>read data from</th></da<> | ar c | dd dd:                                                                           | >  |     | read data from             |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------|----|-----|----------------------------|

|                                                                                                                                               |    |                                                                                            |      |                                                                                  |    |     | CONTROL register           |

| <daw< td=""><td>11</td><td>aa</td><td>aa</td><td><dar< td=""><td>dd</td><td>dd&gt;</td><td>read data from demodulator</td></dar<></td></daw<> | 11 | aa                                                                                         | aa   | <dar< td=""><td>dd</td><td>dd&gt;</td><td>read data from demodulator</td></dar<> | dd | dd> | read data from demodulator |

| <daw< td=""><td>13</td><td>aa</td><td>aa</td><td><dar< td=""><td>dd</td><td>dd&gt;</td><td>read data from DSP</td></dar<></td></daw<>         | 13 | aa                                                                                         | aa   | <dar< td=""><td>dd</td><td>dd&gt;</td><td>read data from DSP</td></dar<>         | dd | dd> | read data from DSP         |

#### 3.1.5.4. Examples

| <80 | 00 | 80 | 00> | >  |     | RESET DPL statically    |

|-----|----|----|-----|----|-----|-------------------------|

| <80 | 00 | 00 | 00> | >  |     | Clear RESET             |

| <80 | 12 | 00 | 08  | 08 | 20> | Set Main channel        |

|     |    |    |     |    |     | source to I2S3 - L/R    |

| <80 | 12 | 00 | 00  | 73 | 00> | Set Main volume to 0 dB |

|     |    |    |     |    |     |                         |

More examples of typical application protocols are listed in Section 3.4. "Programming Tips" on page 34.

# 3.2. Start-Up Sequence: Power-Up and I<sup>2</sup>C Controlling

After POWER ON or RESET (see Fig. 4–21), the IC is in an inactive state. All registers are in the reset position, the analog outputs are muted. The controller has to initialize all registers for which a non-default setting is necessary.

## 3.3. DPL 4519G Programming Interface

#### 3.3.1. User Registers Overview

The DPL 4519G is controlled by means of user registers. The complete list of all user registers is given in the following tables. The registers are partitioned into two sections:

- 1. Subaddress 10<sub>hex</sub> for writing, 11<sub>hex</sub> for reading and

- 2. Subaddress 12<sub>hex</sub> for writing, 13<sub>hex</sub> for reading.

Write and read registers are 16-bit wide, whereby the MSB is denoted bit[15]. Transmissions via I<sup>2</sup>C bus have to take place in 16-bit words (two byte transfers, with the most significant byte transferred first). All write registers, except MODUS and I2S CONFIGURATION, are readable.

Unused parts of the 16-bit write registers must be zero. Addresses not given in this table must not be accessed.

Table 3-5: List of DPL 4519G Write Registers

| Write Register                                                  | Address<br>(hex) | Bits           | Description and Adjustable Range                                                          | Reset                                      | See<br>Page |

|-----------------------------------------------------------------|------------------|----------------|-------------------------------------------------------------------------------------------|--------------------------------------------|-------------|

| I <sup>2</sup> C Subaddress = 10 <sub>hex</sub> ; Registers are | not readal       | ole            |                                                                                           |                                            |             |

| MODUS                                                           | 00 30            | [15:0]         | I <sup>2</sup> S options, D_CTR_I/O modes                                                 | 00 00                                      | 19          |

| I2S CONFIGURATION                                               | 00 40            | [15:0]         | Configuration of I <sup>2</sup> S format                                                  | 00 00                                      | 20          |

| I <sup>2</sup> C Subaddress = 12 <sub>hex</sub> ; Registers are | e all readabl    | e by usin      | g I <sup>2</sup> C Subaddress = 13 <sub>hex</sub>                                         |                                            |             |

| Volume Main channel                                             | 00 00            | [15:8]         | [+12 dB –114 dB, MUTE]                                                                    | MUTE                                       | 24          |

|                                                                 |                  | [7:5]<br>[4:0] | 1/8 dB Steps<br>must be set to 0                                                          | 000 <sub>bin</sub><br>00000 <sub>bin</sub> |             |

| Balance Main channel [L/R]                                      | 00 01            | [15:8]         | [0100 / 100% and 100 / 0100%]<br>[-1270 / 0 and 0 / -1270 dB]                             | 100%/100%                                  | 25          |

| Balance mode Main                                               |                  | [7:0]          | [Linear / logarithmic mode]                                                               | linear mode                                |             |

| Bass Main channel                                               | 00 02            | [15:8]         | [+20 dB12 dB]                                                                             | 0 dB                                       | 26          |

| Treble Main channel                                             | 00 03            | [15:8]         | [+15 dB –12 dB]                                                                           | 0 dB                                       | 27          |

| Loudness Main channel                                           | 00 04            | [15:8]         | [0 dB +17 dB]                                                                             | 0 dB                                       | 28          |

| Loudness filter characteristic                                  | =                | [7:0]          | [NORMAL, SUPER_BASS]                                                                      | NORMAL                                     |             |

| Volume Aux channel                                              | 00 06            | [15:8]         | [+12 dB –114 dB, MUTE]                                                                    | MUTE                                       | 24          |

|                                                                 |                  | [7:5]<br>[4:0] | 1/8 dB Steps<br>must be set to 0                                                          | 000 <sub>bin</sub><br>00000 <sub>bin</sub> |             |

| Volume SCART1 output channel                                    | 00 07            | [15:8]         | [+12 dB –114 dB, MUTE]                                                                    | MUTE                                       | 29          |

| Main source select                                              | 00 08            | [15:8]         | [I <sup>2</sup> S1, I <sup>2</sup> S2, I <sup>2</sup> S3 ch1&2, I <sup>2</sup> S3 ch3&4,] | undefined                                  | 23          |

| Main channel matrix                                             |                  | [7:0]          | [SOUNDA, SOUNDB, STEREO, MONO]                                                            | SOUNDA                                     | 23          |

| Aux source select                                               | 00 09            | [15:8]         | [I <sup>2</sup> S1, I <sup>2</sup> S2, I <sup>2</sup> S3 ch1&2, I <sup>2</sup> S3 ch3&4,] | undefined                                  | 23          |

| Aux channel matrix                                              |                  | [7:0]          | [SOUNDA, SOUNDB, STEREO, MONO]                                                            | SOUNDA                                     | 23          |

| SCART1 source select                                            | 00 0A            | [15:8]         | [I <sup>2</sup> S1, I <sup>2</sup> S2, I <sup>2</sup> S3 ch1&2, I <sup>2</sup> S3 ch3&4,] | undefined                                  | 23          |

| SCART1 channel matrix                                           |                  | [7:0]          | [SOUNDA, SOUNDB, STEREO, MONO]                                                            | SOUNDA                                     | 23          |

| I <sup>2</sup> S source select                                  | 00 0B            | [15:8]         | [I <sup>2</sup> S1, I <sup>2</sup> S2, I <sup>2</sup> S3 ch1&2, I <sup>2</sup> S3 ch3&4,] | undefined                                  | 23          |

| I <sup>2</sup> S channel matrix                                 |                  | [7:0]          | [SOUNDA, SOUNDB, STEREO, MONO]                                                            | SOUNDA                                     | 23          |

| Prescale I <sup>2</sup> S3                                      | 00 11            | [15:8]         | [00 <sub>hex</sub> 7F <sub>hex</sub> ]                                                    | 10 <sub>hex</sub>                          | 21          |

| Prescale I <sup>2</sup> S2                                      | 00 12            | [15:8]         | [00 <sub>hex</sub> 7F <sub>hex</sub> ]                                                    | 10 <sub>hex</sub>                          | 21          |

| ACB: SCART Switches a. D_CTR_I/O                                | 00 13            | [15:0]         | Bits [15:0]                                                                               | 00 <sub>hex</sub>                          | 30          |

| Beeper                                                          | 00 14            | [15:0]         | [00 <sub>hex</sub> 7F <sub>hex</sub> ]/[00 <sub>hex</sub> 7F <sub>hex</sub> ]             | 00/00 <sub>hex</sub>                       | 30          |

| Prescale I <sup>2</sup> S1                                      | 00 16            | [15:8]         | [00 <sub>hex</sub> 7F <sub>hex</sub> ]                                                    | 10 <sub>hex</sub>                          | 21          |

| Mode tone control                                               | 00 20            | [15:8]         | [BASS/TREBLE, EQUALIZER]                                                                  | BASS/TREB                                  | 26          |

| Equalizer Main ch. band 1                                       | 00 21            | [15:8]         | [+12 dB –12 dB]                                                                           | 0 dB                                       | 27          |

| Equalizer Main ch. band 2                                       | 00 22            | [15:8]         | [+12 dB –12 dB]                                                                           | 0 dB                                       | 27          |

| Equalizer Main ch. band 3                                       | 00 23            | [15:8]         | [+12 dB12 dB]                                                                             | 0 dB                                       | 27          |

| Equalizer Main ch. band 4                                       | 00 24            | [15:8]         | [+12 dB –12 dB]                                                                           | 0 dB                                       | 27          |

| Equalizer Main ch. band 5                                       | 00 25            | [15:8]         | [+12 dB –12 dB]                                                                           | 0 dB                                       | 27          |

| Subwoofer level adjust                                          | 00 2C            | [15:8]         | [0 dB –30 dB, mute]                                                                       | 0 dB                                       | 29          |

Table 3-5: List of DPL 4519G Write Registers, continued

| Write Register                         | Address<br>(hex) | Bits   | Description and Adjustable Range                                                          | Reset             | See<br>Page |

|----------------------------------------|------------------|--------|-------------------------------------------------------------------------------------------|-------------------|-------------|

| Balance Aux channel [L/R]              | 00 30            | [15:8] | [0100 / 100% and 100 / 0100%]<br>[-1270 / 0 and 0 / -1270 dB]                             | 100 %/100 %       | 25          |

| Balance mode Aux                       |                  | [7:0]  | [Linear mode / logarithmic mode]                                                          | linear mode       |             |

| Bass Aux channel                       | 00 31            | [15:8] | [+20 dB –12 dB]                                                                           | 0 dB              | 26          |

| Treble Aux channel                     | 00 32            | [15:8] | [+15 dB –12 dB]                                                                           | 0 dB              | 27          |

| Loudness Aux channel                   | 00 33            | [15:8] | [0 dB +17 dB]                                                                             | 0 dB              | 28          |

| Loudness filter characteristic         |                  | [7:0]  | [NORMAL, SUPER_BASS]                                                                      | NORMAL            |             |

| I <sup>2</sup> S3 Resorting            | 00 36            | [15:8] | through, straight eight, I/r eight, I/r six, I/r four, 2ch through                        | 00 <sub>hex</sub> | 22          |

| Surround source select                 | 00 48            | [15:8] | [I <sup>2</sup> S1, I <sup>2</sup> S2, I <sup>2</sup> S3 ch1&2, I <sup>2</sup> S3 ch3&4,] | undefined         | 23          |

| Surround channel matrix                |                  | [7:0]  | [SOUNDA, SOUNDB, STEREO, MONO]                                                            | SOUNDA            | 23          |

| Spatial effect for surround processing | 00 49            | [15:8] | [0% - 100%]                                                                               | 00 <sub>hex</sub> | 31          |

| Virtual surround effect strength       | 00 4A            | [15:8] | [0% - 100%]                                                                               | 00 <sub>hex</sub> | 31          |

| Decoder matrix                         | 00 4B            | [15:8] | [ADAPTIVE/PASSIVE/EFFECT]                                                                 | 00 <sub>hex</sub> | 32          |

| Surround reproduction                  |                  | [7:4]  | [REAR_SPEAKER/FRONT_SPEAKER/PANORAMA/<br>3D_PANORAMA]                                     | 0 <sub>hex</sub>  | 32          |

| Center mode                            |                  | [3:0]  | [PHANTOM/NORMAL/WIDE/OFF]                                                                 | 0 <sub>hex</sub>  | 32          |

| Surround delay                         | 00 4C            | [15:0] | [531ms]                                                                                   | 00 <sub>hex</sub> | 32          |

| Noise Generator                        | 00 4D            | [15:0] | [NOISEL, NOISEC, NOISER, NOISES]                                                          | 00 <sub>hex</sub> | 32          |

Table 3-6: List of DPL 4519G Read Registers

| Read Register                                                                       | Address<br>(hex)                                                                    | Bits   | Description and Adjustable Range       | See<br>Page |  |  |  |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------|----------------------------------------|-------------|--|--|--|

| I <sup>2</sup> C Subaddress = 11 <sub>hex</sub> ; Registers are <i>not</i> writable |                                                                                     |        |                                        |             |  |  |  |

| STATUS                                                                              | 02 00                                                                               | [15:0] | Monitoring of settings e.g. D_CTR_I/O  | 21          |  |  |  |

| I <sup>2</sup> C Subaddress = 13 <sub>hex</sub> ; Registers are                     | I <sup>2</sup> C Subaddress = 13 <sub>hex</sub> ; Registers are <i>not</i> writable |        |                                        |             |  |  |  |

| DPL hardware version code                                                           | 00 1E                                                                               | [15:8] | [00 <sub>hex</sub> FF <sub>hex</sub> ] | 33          |  |  |  |

| DPL major revision code                                                             |                                                                                     | [7:0]  | [00 <sub>hex</sub> FF <sub>hex</sub> ] | 33          |  |  |  |

| DPL product code                                                                    | 00 1F                                                                               | [15:8] | [00 <sub>hex</sub> FF <sub>hex</sub> ] | 33          |  |  |  |

| DPL ROM version code                                                                |                                                                                     | [7:0]  | [00 <sub>hex</sub> FF <sub>hex</sub> ] | 33          |  |  |  |

# 3.3.2. Description of User Registers

# 3.3.2.1. Write Registers on I<sup>2</sup>C Subaddress 10<sub>hex</sub>

**Table 3–7:** Write Registers on I<sup>2</sup>C Subaddress 10<sub>hex</sub>

| Register<br>Address  | Function  | Function |                                                                                                                                                                                                                         |       |  |  |  |  |  |

|----------------------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| MODUS                |           |          |                                                                                                                                                                                                                         |       |  |  |  |  |  |

| 00 30 <sub>hex</sub> | MODUS     | Register |                                                                                                                                                                                                                         | MODUS |  |  |  |  |  |

|                      | bit[15:8] | 0        | undefined, must be 0                                                                                                                                                                                                    |       |  |  |  |  |  |

|                      | bit[7]    | 0/1      | active/tristate state of audio clock output pin AUD_CL_OUT                                                                                                                                                              |       |  |  |  |  |  |

|                      | bit[6]    | 0<br>1   | word strobe alignment (synchronous I <sup>2</sup> S) WS changes at data word boundary WS changes one clock cycle in advance                                                                                             |       |  |  |  |  |  |

|                      | bit[5]    | 0/1      | master/slave mode of I <sup>2</sup> S interface                                                                                                                                                                         |       |  |  |  |  |  |

|                      | bit[4]    | 0/1      | active/tristate state of I <sup>2</sup> S output pins                                                                                                                                                                   |       |  |  |  |  |  |

|                      | bit[3]    | 0        | state of digital output pins D_CTR_I/O_0 and _1 active: D_CTR_I/O_0 and _1 are output pins (can be set by means of the ACB register) tristate: D_CTR_I/O_0 and _1 are input pins (level can be read out of STATUS[4,3]) |       |  |  |  |  |  |

|                      | bit[2:0]  | 0        | undefined, must be 0                                                                                                                                                                                                    |       |  |  |  |  |  |

**Table 3–7:** Write Registers on I<sup>2</sup>C Subaddress 10<sub>hex</sub>, continued

| Register<br>Address  | Function                        |                                                                                                                      | Name         |  |  |  |  |  |  |  |

|----------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|--|

| I2S CONFIGURATION    |                                 |                                                                                                                      |              |  |  |  |  |  |  |  |

| 00 40 <sub>hex</sub> | I2S CON                         | FIGURATION Register                                                                                                  | I2S_CONFIG   |  |  |  |  |  |  |  |

|                      | I2S3 <sup>1)</sup>              |                                                                                                                      |              |  |  |  |  |  |  |  |

|                      | bit[11]                         | I <sup>2</sup> S data alignment (must be 0 if bit[2] = 1)<br>0/1 left/right aligned                                  | I2S3_ALIGN   |  |  |  |  |  |  |  |

|                      | bit[10]                         | wordstrobe polarity (must be 0 if bit[2] = 1)  1                                                                     | I2S3_WS_POL  |  |  |  |  |  |  |  |

|                      | bit[9]                          | wordstrobe alignment (asynchronous I2S_3) 0 WS changes at data word boundary 1 WS changes one clock cycle in advance | I2S3_WS_MODE |  |  |  |  |  |  |  |

|                      | bit[8]                          | Sample Mode<br>0/1 Two/Multi sample                                                                                  | I2S3_MSAMP   |  |  |  |  |  |  |  |

|                      | bit[7:4]                        | Word length of each data packet = (n-2)/2 bit[3]=0, bit[8]=1 (multi-sample input mode) 0111 16 bit 1000 18 bit       | I2S3_MBIT    |  |  |  |  |  |  |  |

|                      |                                 | <br>1111 32 bit                                                                                                      |              |  |  |  |  |  |  |  |

|                      |                                 | bit[3]=0, bit[8]=0 (two-sample input mode)<br>xxxx 1632 bit, 18-bit valid                                            |              |  |  |  |  |  |  |  |

|                      |                                 | bit[3]=1, bit[8]=1 (multi-sample output mode) 1111 32 bit                                                            |              |  |  |  |  |  |  |  |

|                      |                                 | bit[3]=1, bit[8]=0 (two-sample output mode)<br>0111                                                                  |              |  |  |  |  |  |  |  |

|                      | bit[3]                          | I <sup>2</sup> S3 Mode 1 output (I2S3 CL/WS active) 0 input (I2S3 CL/WS tristate)                                    | I2S3_MODE    |  |  |  |  |  |  |  |

|                      | I <sup>2</sup> S1/2/3           |                                                                                                                      |              |  |  |  |  |  |  |  |

|                      | bit[2]                          | I <sup>2</sup> S1/2/3 Timing 1 I <sup>2</sup> S3 timing for all I <sup>2</sup> S inputs (1/2/3) 0 default mode       | I2S_TIMING   |  |  |  |  |  |  |  |

|                      | I <sup>2</sup> S Out            |                                                                                                                      |              |  |  |  |  |  |  |  |

|                      | bit[1:0]                        | I2S_CL frequency and I2S_DA_OUT sample length 00                                                                     |              |  |  |  |  |  |  |  |

| [8] = 0              | , [7:4] = 011<br>, [7:4] = else |                                                                                                                      |              |  |  |  |  |  |  |  |

# 3.3.2.2. Read Registers on I<sup>2</sup>C Subaddress 11<sub>hex</sub>

**Table 3–8:** Read Registers on I<sup>2</sup>C Subaddress 11<sub>hex</sub>

| Register<br>Address  | Functio   | n               |                                               | Name |  |  |  |  |

|----------------------|-----------|-----------------|-----------------------------------------------|------|--|--|--|--|

| 02 00 <sub>hex</sub> | STATUS    | STATUS Register |                                               |      |  |  |  |  |

|                      | Contains  | s the statu     | us of the D_CTR_I/O pins                      |      |  |  |  |  |

|                      | bit[15:5] |                 | undefined                                     |      |  |  |  |  |

|                      | bit[4]    | 0/1             | low/high level of digital I/O pin D_CTR_I/O_1 |      |  |  |  |  |

|                      | bit[3]    | 0/1             | low/high level of digital I/O pin D_CTR_I/O_0 |      |  |  |  |  |

|                      | bit[2:0]  |                 | undefined                                     |      |  |  |  |  |

# 3.3.2.3. Write Registers on I<sup>2</sup>C Subaddress 12<sub>hex</sub>

**Table 3–9:** Write Registers on I<sup>2</sup>C Subaddress 12<sub>hex</sub>

| Register<br>Address                                                  | Function                            | Function                                                    |                                                                 |                                  |  |  |  |  |  |  |

|----------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------|--|--|--|--|--|--|

| PREPROC                                                              | PREPROCESSING                       |                                                             |                                                                 |                                  |  |  |  |  |  |  |

| 00 16 <sub>hex</sub><br>00 12 <sub>hex</sub><br>00 11 <sub>hex</sub> | I2S1 Pres<br>I2S2 Pres<br>I2S3 Pres | scale<br>scale                                              | e value for digital I <sup>2</sup> S input signals              | PRE_I2S1<br>PRE_I2S2<br>PRE_I2S3 |  |  |  |  |  |  |

|                                                                      | bit[15:8]                           | 00 <sub>hex</sub><br>10 <sub>hex</sub><br>7F <sub>hex</sub> | off<br>0 dB gain (recommendation)<br>+18 dB gain (maximum gain) |                                  |  |  |  |  |  |  |

**Table 3–9:** Write Registers on I<sup>2</sup>C Subaddress 12<sub>hex</sub>, continued

| Register<br>Address  | Function                                                                                                                                                                                                                                                                                                                                                                                             | Name      |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| I2S3 RES             | ORTING MATRIX                                                                                                                                                                                                                                                                                                                                                                                        |           |

| 00 36 <sub>hex</sub> | I2S3 Resorting Matrix (not mentioned bit combinations must not be used)                                                                                                                                                                                                                                                                                                                              | I2S3_Sort |

|                      | Resorting of multichannel inputs                                                                                                                                                                                                                                                                                                                                                                     |           |

|                      | bit[15:8]                                                                                                                                                                                                                                                                                                                                                                                            |           |

|                      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                 |           |

|                      | $\begin{array}{ccccc} \text{0001}_{\text{hex}}: & \text{8 channel, "straight eight"} \\ & & \text{1,2,3,4,5,6,7,8} & \rightarrow & \text{7,8,1,2,3,4,5,6} \\ & & & \text{L,R,S}_{\text{L}}, \text{S}_{\text{R}}, \text{C,LFE,L}_{\text{t}}, \text{R}_{\text{t}} & \rightarrow & \text{L}_{\text{t}}, \text{R}_{\text{t}}, \text{L,R,S}_{\text{L}}, \text{S}_{\text{R}}, \text{C,LFE} \\ \end{array}$ |           |

|                      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                 |           |

|                      | $\begin{array}{cccc} \text{0003}_{\text{hex}}: & \text{6 channel, "left/right six"} \\ & & 1,2,3,4,5,6 & \rightarrow & \text{-,-,1,4,2,5,3,6} \\ & & & L,S_{\text{L}},C,R,S_{\text{R}},LFE & \rightarrow & \text{,,L,R,S}_{\text{L}},S_{\text{R}},C,LFE \end{array}$                                                                                                                                 |           |

|                      | 0004 <sub>hex</sub> : 4 channel, "left/right four", "External ProLogic" $\begin{array}{ccc} & & & \\ & 1,2,3,4 & \rightarrow & \text{-,-,1,3,4,4,2,-} \\ & & L,C,R,S & \rightarrow & \text{,,L,R,S}_L,S_R,C, \end{array}$                                                                                                                                                                            |           |

|                      | $\begin{array}{lll} 0010_{hex}: & 2 \; channel, \; "through"; \; "Internal \; ProLogic" \\ & 1,2 & \rightarrow 1,2,+,+,+,+,+ \\ & L_t, R_t & \rightarrow L_t, R_t, L_{PL}, R_{PL}, S_{PL}, C_{PL}, SUB_{PL} \\ & "+": \; channel \; will \; be \; replaced \; by \; internally \; generated \; signal \\ & "X_{PL}": \; internally \; generated \; signal \end{array}$                               |           |

**Table 3–9:** Write Registers on I<sup>2</sup>C Subaddress 12<sub>hex</sub>, continued

| Register<br>Address                                                                                                  | Function                                | ı                                                                                |                                                                                                                            | Name |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|--|--|