# DP8402A,DP8403,DP8404,DP8405

DP8402A/DP8403/DP8404/DP8405 32-Bit Parallel Error Detection and

Correction Circuits (EDAC's)

Literature Number: SNOSBX3A

National Semiconductor

# DP8402A/DP8403/DP8404/DP8405 32-Bit Parallel **Error Detection and Correction Circuits (EDAC's)**

#### **General Description**

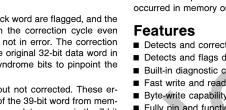

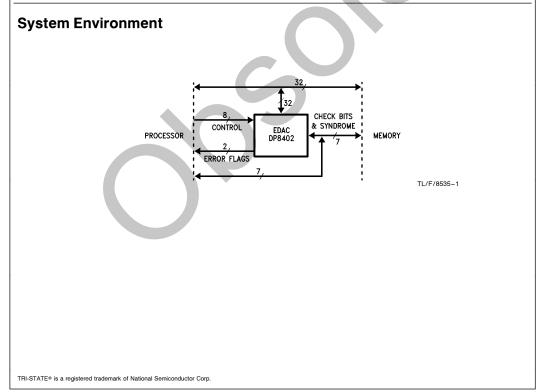

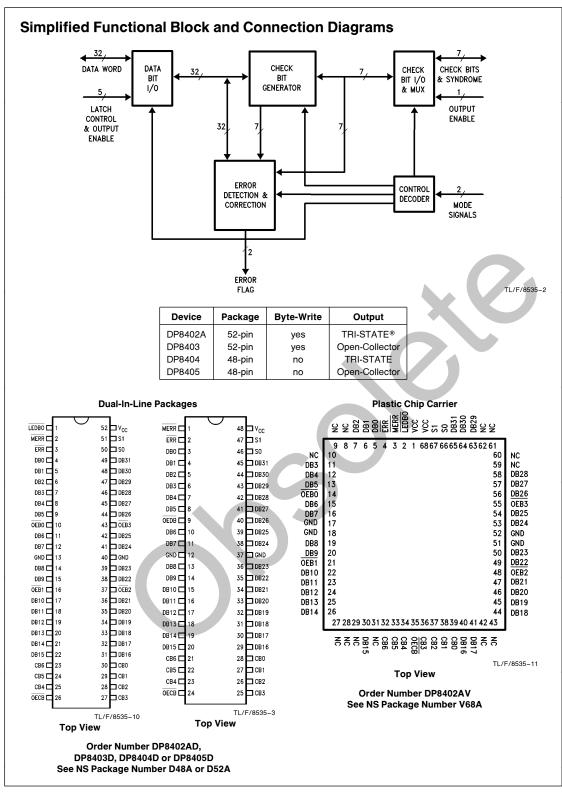

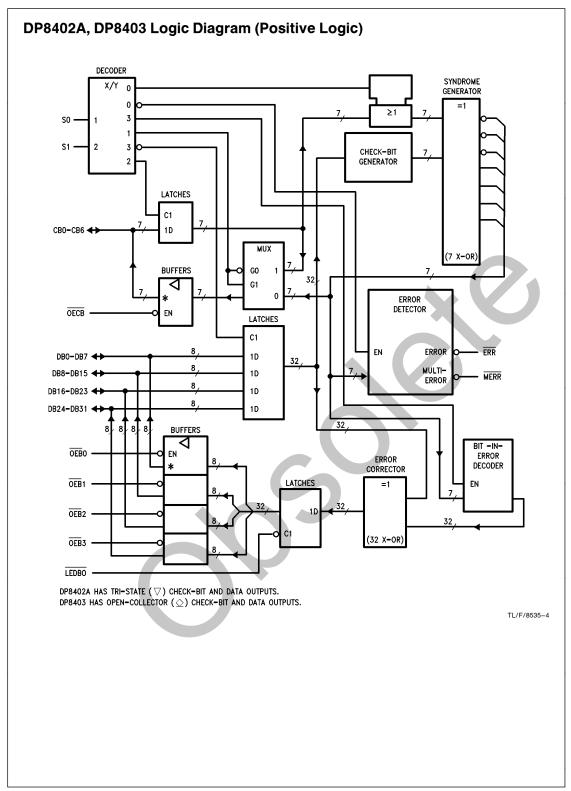

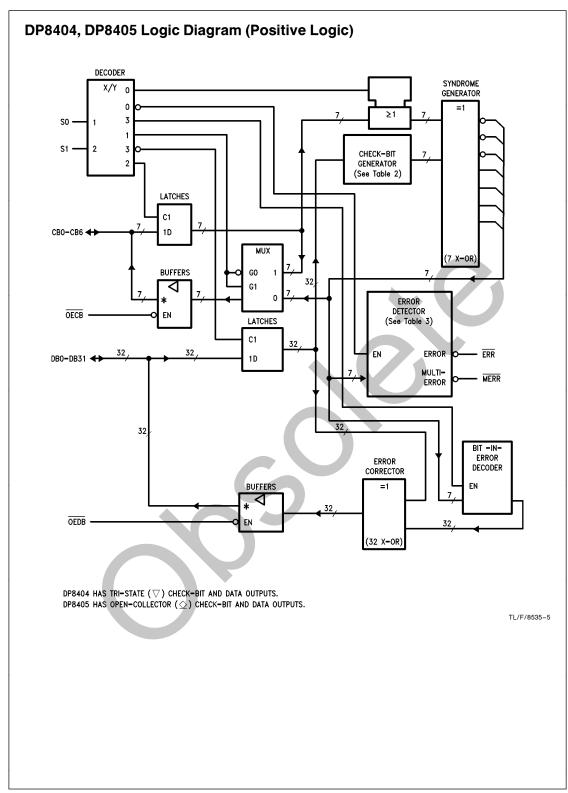

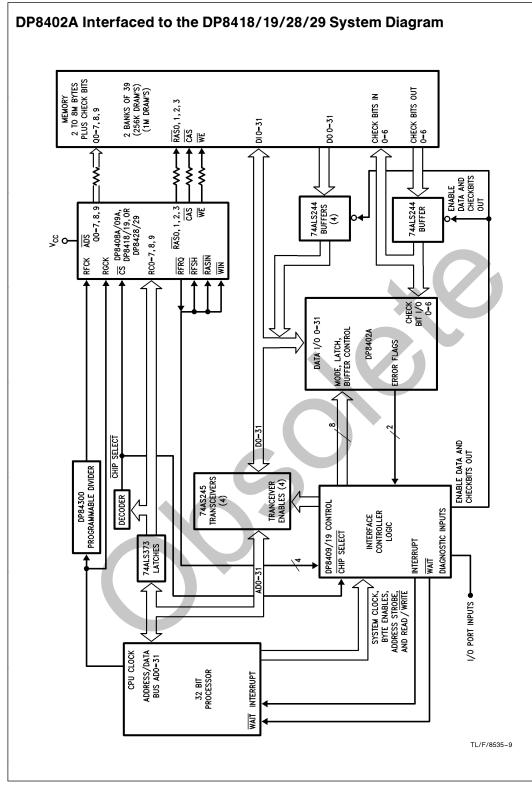

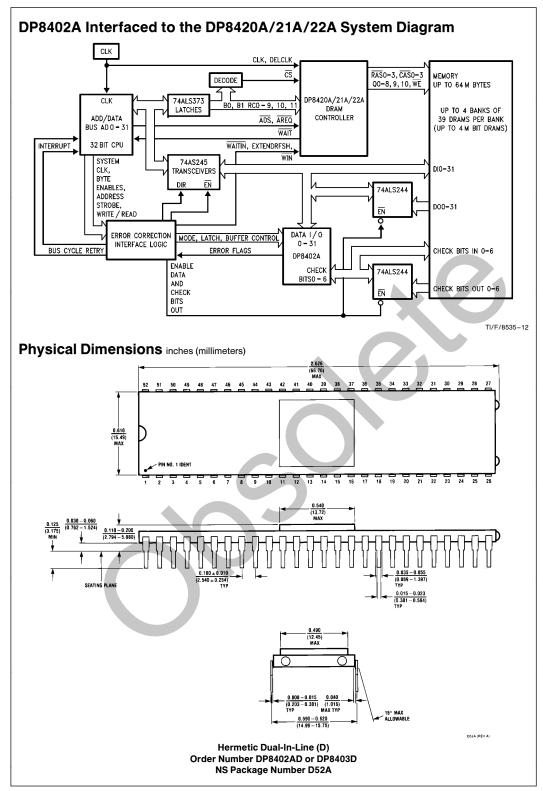

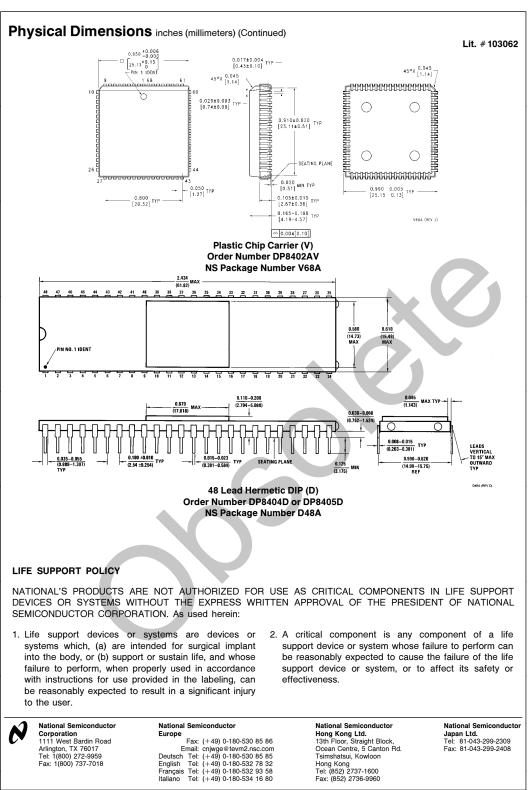

The DP8402A, DP8403, DP8404 and DP8405 devices are 32-bit parallel error detection and correction circuits (EDACs) in 52-pin DP8402A and DP8403 or 48-pin DP8404 and DP8405 600-mil packages. The EDACs use a modified Hamming code to generate a 7-bit check word from a 32-bit data word. This check word is stored along with the data word during the memory write cycle. During the memory read cycle, the 39-bit words from memory are processed by the EDACs to determine if errors have occurred in memory. Single-bit errors in the 32-bit data word are flagged and corrected.

Single-bit errors in the 7-bit check word are flagged, and the CPU sends the EDAC through the correction cycle even though the 32-bit data word is not in error. The correction cycle will simply pass along the original 32-bit data word in this case and produce error syndrome bits to pinpoint the error-generating location.

Double bit errors are flagged but not corrected. These errors may occur in any two bits of the 39-bit word from memory (two errors in the 32-bit data word, two errors in the 7-bit check word, or one error in each word). The gross-error

condition of all lows or all highs from memory will be detected. Otherwise, errors in three or more bits of the 39-bit word are beyond the capabilities of these devices to detect.

PRELIMINARY

August 1989

Read-modify-write (byte-control) operations can be performed with the DP8402A and DP8403 EDACs by using output latch enable, LEDBO, and the individual OEB0 thru OEB3 byte control pins.

Diagnostics are performed on the EDACs by controls and internal paths that allow the user to read the contents of the DB and CB input latches. These will determine if the failure occurred in memory or in the EDAC.

- Detects and corrects single-bit errors

- Detects and flags double-bit errors

- Built-in diagnostic capability

- Fast write and read cycle processing times

- Byte-write capability . . . DP8402A and DP8403

- Fully pin and function compatible with TI's SN74ALS632A thru SN74ALS635 series

© 1995 National Semiconductor Corporation TL/F/8535 RRD-B30M105/Printed in U. S. A.

| mou      | e De   | enn             | itions        |          |                                |                 | PCC Pin D                |                       | DF040           | ZA              |

|----------|--------|-----------------|---------------|----------|--------------------------------|-----------------|--------------------------|-----------------------|-----------------|-----------------|

| MODE     |        |                 | DESCRI        |          |                                |                 | pin 1                    | V <sub>CC</sub>       | pin 35          | OECB            |

|          | S1     | S0              | MOD           | E        |                                | RATION          | 2                        | LEDBO                 | 36              | CB3             |

| 0        | L      | L               | WRITE         |          |                                | vord and output | 3                        | MERR                  | 37              | CB2             |

|          |        |                 |               | TIOO     | checkword                      |                 | 4                        | ERR                   | 38              | CB1             |

| 1        | L      | Н               | DIAGNOS       | nus      | against late                   | us data words   | 5                        | DB0                   | 39              | CB0             |

|          |        |                 |               |          | 0                              | /output valid   | 6                        | DB1                   | 40              | DB16            |

|          |        |                 |               |          | error flags.                   | / output valid  | 7                        | DB2                   | 41              | DB17            |

| 2        | н      | L               | READ & F      | LAG      |                                | ord and output  | 8                        | NC                    | 42              | NC              |

|          |        |                 |               |          | error flags                    |                 | 9                        | NC                    | 43              | NC              |

| 3        | н      | н               | CORREC        | Г        | Latched inp                    | out data and    | 10                       | NC                    | 44              | DB18            |

|          |        |                 |               |          | checkword                      | /output         | 11                       | DB3                   | 45              | DB19            |

|          |        |                 |               |          | corrected c                    |                 | 12                       | DB4                   | 46              | DB20            |

|          |        |                 |               |          | syndrome of                    | code            | 13                       | DB5                   | 47              | DB21            |

| <u>.</u> |        |                 |               |          |                                |                 | 14                       | <b>OEBO</b>           | 48              | OEB2            |

|          | Defi   |                 |               |          |                                |                 | 15                       | DB6                   | 49              | DB22            |

| 50, S1   |        |                 |               |          | ode, see prec                  | eding           | 16                       | DB7                   | 49<br>50        | DB22<br>DB23    |

|          |        |                 | de Definiti   |          |                                |                 | 10                       | GND                   | 51              | GND             |

|          |        |                 | port for 3    |          |                                |                 | 18                       | GND                   | 52              | GND             |

| BO IN    | ru CB6 |                 |               |          | eckword. Also<br>ne error code |                 | 18                       | DB8                   | 53              | DB24            |

|          |        |                 | or correction |          |                                | uunng           | 19<br>20                 | DB8<br>DB9            | 53<br>54        | DB24<br>DB25    |

| DEBO t   | hru    |                 |               |          | ffer enable. V                 | Vhen high       |                          | OEB1                  |                 | OEB3            |

| DEB3     | a      |                 |               |          | t TRI-STATE                    |                 | 21                       |                       | 55              |                 |

| DP840    | )2A,   |                 |               |          | . OEB0 contr                   |                 | 22                       | DB10                  | 56              | DB26            |

| DP840    | 3)     | thru            | I DB7, OE     | B1 cor   | ntrols DB8 th                  | ru DB15,        | 23                       | DB11                  | 57              | DB27            |

|          |        | OE              | B2 control    | ls DB1   | 6 thru DB23                    | and OEB3        | 24                       | DB12                  | 58              | DB28            |

|          | _      |                 | trols DB2     |          |                                |                 | 25                       | DB13                  | 59              | NC              |

| EDBC     |        |                 |               |          | atch enable.                   |                 | 26                       | DB14                  | 60              | NC              |

| DP840    | ,      |                 |               |          | e Latch. Ope                   | rates on all    | 27                       | NC                    | 61              | NC              |

| DP840    | 3)     |                 | bits of the   |          | ora.<br>for the data l         | (O port         | 28                       | NC                    | 62              | NC              |

| DP840    | 14     |                 |               |          | uffers are at                  | 70 port.        | 29                       | NC                    | 63              | DB29            |

| DP840    |        |                 | -STATE.       | iipui b  | uners are at                   |                 | 30                       | DB15                  | 64              | DB30            |

| DECB     | 0)     |                 |               | utput b  | ouffer enable.                 | When            | 31                       | NC                    | 65              | DB31            |

|          |        |                 |               |          | ers are in TR                  |                 | 32                       | CB6                   | 66              | S0              |

|          |        | mo              | de.           |          |                                |                 | 33                       | CB5                   | 67              | S1              |

| ERR      |        |                 |               |          | lag, a low ind                 | licates at      | 34                       | CB4                   | 68              | V <sub>CC</sub> |

|          |        |                 | st a single   |          |                                |                 |                          |                       |                 |                 |

| MERR     |        |                 |               |          | t flag, a low ir               | ndicates        |                          |                       |                 |                 |

|          |        | two             | or more e     | errors p | present.                       |                 |                          |                       |                 |                 |

|          |        |                 |               |          |                                |                 |                          |                       |                 |                 |

|          |        |                 |               |          | Т                              | ABLE I. Write C | Control Function         |                       |                 |                 |

| emory    |        | EDAC            | <b>C</b> 0    | ntrol    |                                | DB Control      | DB Output Latch          |                       | СВ              | Error Flag      |

| Cycle    |        | unctio          |               | SO       | Data I/O                       | OEBn or<br>OEDB | DP8402A, DP8403<br>LEDBO | 3 Check I/O           | Control<br>OECB | ERR ME          |

| Write    |        | enera<br>eck wo |               | L        | Input                          | Н               | х                        | Output<br>check bits† | L               | н               |

## Memory Write Cycle Details

During a memory write cycle, the check bits (CB0 thru CB6) are generated internally in the EDAC by seven 16-input parity generators using the 32-bit data word as defined in Table 2. These seven check bits are stored in memory along with the original 32-bit data word. This 32-bit word will later be used in the memory read cycle for error detection and correction.

|            |    |    |    |    |    |    |    |    |    | TA | ۱BL | E II. | Pari | ity A | lgo | rithr | n   |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|------------|----|----|----|----|----|----|----|----|----|----|-----|-------|------|-------|-----|-------|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Check Word |    |    |    |    |    |    |    |    |    |    |     |       | 32   | 2-Bit | Dat | a W   | ord |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Bit        | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21  | 20    | 19   | 18    | 17  | 16    | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | ( |

| CB0        | Х  |    | Х  | Х  |    | Х  |    |    |    |    | Х   |       | Х    | Х     | Х   |       |     | Х  |    |    | Х  |    | Х | Х | Х | Х |   | Х |   |   |   | 2 |

| CB1        |    |    |    | Х  |    | Х  |    | Х  |    | Х  |     | Х     |      | Х     | Х   | Х     |     |    |    | Х  |    | Х  |   | Х |   | Х |   | Х |   |   | Х | 2 |

| CB2        | X  |    | Х  |    |    | Х  | Х  |    | Х  |    |     | Х     | Х    |       |     | Х     | Х   |    | Х  |    |    | Х  | Х |   | Х |   |   | Х | Х | Х |   | 2 |

| CB3        |    |    | Х  | Х  | Х  |    |    |    | Х  | Х  | Х   |       |      |       | Х   | Х     |     |    | Х  | Х  | Х  |    |   |   | Х | Х | Х |   |   |   | Х | 2 |

| CB4        | X  | Х  |    |    |    |    |    |    | Х  | Х  | Х   | Х     | Х    | Х     |     |       | Х   | Х  |    |    |    |    |   |   | Х | Х | Х | Х | Х | Х |   |   |

| CB5        | X  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |    |     |       |      |       |     |       | Х   | Х  | Х  | Х  | Х  | Х  | Х | Х |   |   |   |   |   |   |   |   |

| CB6        | X  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |    |     |       |      |       |     |       |     |    |    |    |    |    |   |   | Х | Х | Х | Х | Х | Х | Х | 2 |

The seven check bits are parity bits derived from the matrix of data bits as indicated by "X" for each bit.

Check bits 0, 1, 2 are odd parity or the exclusive NORing of the "X"ed bits for the particular check bit. Check bits 3, 4, 5, 6 are even parity or the exclusive ORing of the "X"ed bits for the particular check bit.

### Memory Read Cycle (Error Detection & Correction Details)

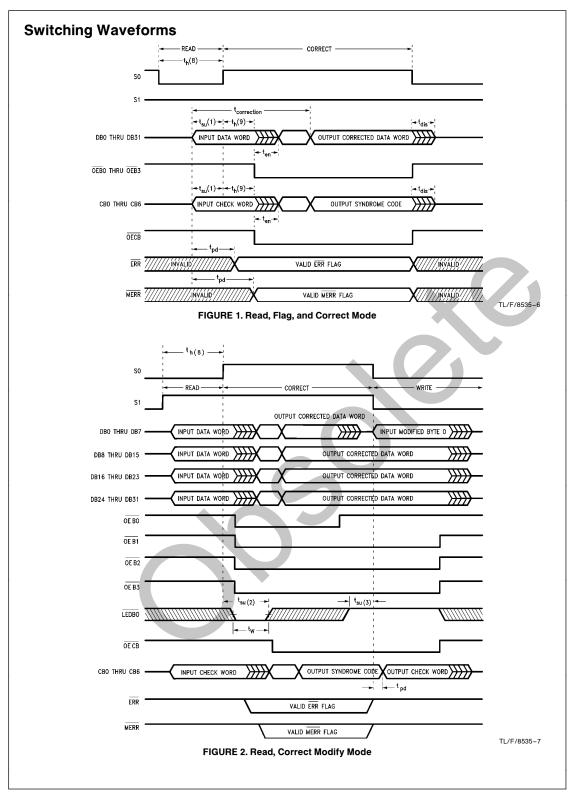

During a memory read cycle, the 7-bit check word is retrieved along with the actual data. In order to be able to determine whether the data from the memory is acceptable to use as presented on the bus, the error flags must be tested to determine if they are at the high level.

The first case in Table III represents the normal, no-error conditions. The EDAC presents highs on both flags. The

next two cases of single-bit errors give a high on  $\overline{\text{MERR}}$  and a low on  $\overline{\text{ERR}}$ , which is the signal for a correctable error, and the EDAC should be sent through the correction cycle. The last three cases of double-bit errors will cause the EDAC to signal lows on both  $\overline{\text{ERR}}$  and  $\overline{\text{MERR}}$ , which is the interrupt indication for the CPU.

TABLE III. Error Function

| Total Numb       | er of Errors     |     | r Flags | Data Correction |

|------------------|------------------|-----|---------|-----------------|

| 32-Bit Data Word | 7-Bit Check Word | ERR | MERR    | Butu Correction |

| 0                | 0                | н   | H       | Not applicable  |

| 1                | 0                | L   | н       | Correction      |

| 0                | 1                | L   | н       | Correction      |

| 1                | 1                | L   | L       | Interrupt       |

| 2                | 0                | L,  |         | Interrupt       |

| 0                | 2                | L   | L       | Interrupt       |

The DP8402 check bit syndrome matrix can be seen in TA-BLE II. The horizontal rows of this matrix generate the check bits by selecting different combinations of data bits, indicated by "X"s in the matrix, and generating parity from them. For instance, parity check bit "0" is generated by EXCLUSIVE NORing the following data bits together; 31, 29, 28, 26, 21, 19, 18, 17, 14, 11, 9, 8, 7, 6, 4, and 0. For example, the data word "0000001H" would generate the check bits CB6-0 = 48H (Check bits 0, 1, 2 are odd parity and check bits 3, 4, 5, 6 are even parity).

During a WRITE operation (mode 0) the data enters the DP8402 and check bits are generated at the check bit input/output port. Both the data word and the check bits are then written to memory. During a READ operation (mode 2, error detection) the data and check bits that were stored in memory, now possibly in error, are input through the data and check bit I/O ports. New check bits are internally generated from the data word. These new check bits are then compared, by an EXCLU-SIVE NOR operation, with the original check bits that were stored in memory. The EXCLUSIVE NOR of the original check bits, that were stored in memory, with the new check bits is called the syndrome word. If the original check bits are the same as the new check bits, a no error condition, then a syndrome word of all ones is produced and both error flags (ERR and MERR) will be high. The DP8402 matrix encodes errors as follows:

|                 |                                                        |           |             | TABLE IV.                        | Read, Flag, ar                | nd Correct Function                         |                                |                       |                         |

|-----------------|--------------------------------------------------------|-----------|-------------|----------------------------------|-------------------------------|---------------------------------------------|--------------------------------|-----------------------|-------------------------|

| Memory<br>Cycle | EDAC<br>Function                                       | Cor<br>S1 | ntrol<br>S0 | Data I/O                         | DB Control<br>OEBn or<br>OEDB | DB Output Latch<br>DP8402A, DP8403<br>LEDBO | Check I/O                      | CB<br>Control<br>OECB | Error Flags<br>ERR MERR |

| Read            | Read & flag                                            | н         | L           | Input                            | Н                             | Х                                           | Input                          | Н                     | Enabled†                |

| Read            | Latch input<br>data and check<br>bits                  | н         | н           | Input<br>data<br>latched         | Н                             | L                                           | Input<br>check word<br>latched | Н                     | Enabled†                |

| Read            | Output<br>corrected data<br>& syndrome bits            | н         | н           | Output<br>corrected<br>data word | L                             | х                                           | Output<br>syndrome<br>bits‡    | L                     | Enabled†                |

|                 | e III for error description<br>e V for error location. | I.        |             |                                  |                               |                                             |                                |                       |                         |

#### Memory Read Cycle (Error Detection & Correction Details) (Continued)

- 1) Single data bit errors cause 3 or 5 bits in the syndrome word to go low. The columns of the check bit syndrome matrix (TABLE II) are the syndrome words for all single bit data errors in the 32 bit word (also see TABLE V). The data bit in error corresponds to the column in the check bit syndrome matrix that matches the syndrome word. For instance, the syndrome word indicating that data bit 31 is in error would be (CB6-CB0) = "0001010", see the column for data bit 31 in TABLE II, or see TABLE V. During mode 3 (S0 = S1 = 1) the syndrome word is decoded, during single data bit errors, and used to invert the bit in error thus correcting the data word. The corrected word is made available on the data I/O port (DB0 thru DB31), the check word I/O port (CB0 thru CB6) presents the 7-bit syndrome error code. This syndrome error code can be used to locate the bad memory chip.

- 2) A single check bit error will cause that particular check bit to go low in the syndrome word.

- 3) A double bit error will cause an even number of bits in the syndrome word to go low. The syndrome word will then be the EXCLUSIVE NOR of the two individual syndrome words corresponding to the 2 bits in error. The two-bit error is not correctable since the parity tree can only identify single bit errors.

If any of the bits in the syndrome word are low the "ERR" flag goes low. The "MERR" (dual error) flag goes low during any double bit error conditions. (See Table III).

Three or more simultaneous bit errors can cause the EDAC to believe that no error, a correctable error, or an uncorrectable error has occurred and will produce erroneous results in all three cases. It should be noted that the gross-error conditions of all lows and all highs will be detected.

|    |     |       |       |      |       |       |       |   |    |     |    | ٦    | AE   | BLE | V. Syr | dro | me  | e D | eco | odir | ng   |      |   |

|----|-----|-------|-------|------|-------|-------|-------|---|----|-----|----|------|------|-----|--------|-----|-----|-----|-----|------|------|------|---|

|    | Sy  | nd    | ron   | ne E | Bits  | 5     | Error |   | Sy | ndı | on | ne E | Bits | ;   | Error  |     |     | Sy  | ndı | om   | ne E | Bits | ; |

| 6  | 5   | 4     | 3     | 2    | 1     | 0     | LIIO  | 6 | 5  | 4   | 3  | 2    | 1    | 0   | LIIO   |     | 6   | 5   | 4   | 3    | 2    | 1    | 0 |

| L  | L   | L     | L     | L    | L     | L     | unc   | L | н  | L   | L  | L    | L    | L   | 2-bit  |     | н   | L   | L   | L    | L    | L    | L |

| L  | L   | L     | L     | L    | L     | Н     | 2-bit | L | н  | L   | L  | L    | L    | Н   | unc    |     | н   | L   | L   | L    | L    | L    | н |

| L  | L   | L     | L     | L    | Н     | L     | 2-bit | L | Н  | L   | L  | L    | Н    | L   | DB7    |     | Н   | L   | L   | L    | L    | Н    | L |

| L  | L   | L     | L     | L    | Н     | Н     | unc   | L | Н  | L   | L  | L    | Н    | Н   | 2-bit  |     | н   | L   | L   | L    | L    | Н    | Н |

| L  | L   | L     | L     | Н    | L     | L     | 2-bit | L | Н  | L   | L  | Н    | L    | L   | DB6    |     | н   | L   | L   | L    | н    | L    | L |

| L  | L   | L     | L     | Н    | L     | Н     | unc   | L | Н  | L   | L  | Н    | L    | Н   | 2-bit  |     | Н   | Ł   | L   | L    | Н    | L    | н |

| L  | L   | L     | L     | Н    | н     | L     | unc   | L | Н  | L   | L  | н    | Н    | L   | 2-bit  |     | Н   | Ŀ   | L   | L    | Н    | Н    | L |

| L  | L   | L     | L     | Н    | Н     | Н     | 2-bit | L | Н  | L   | L  | Н    | Н    | Н   | DB5    |     | Н   | L   | Ľ   | L    | Н    | H,   | Η |

| L  | L   | L     | Н     | L    | L     | L     | 2-bit | L | Н  | L   | Н  | L    | L    | L   | DB4    |     | н   | L   | L   | Н    | L    | L    | L |

| L  | L   | L     | н     | L    | L     | Н     | unc   | L | н  | L   | Н  | L    | L    | Н   | 2-bit  |     | н   | Ŀ   | L   | н    | L    | L    | н |

| L  | L   | L     | н     | L    | Н     | L     | DB31  | L | н  | L   | Н  | L    | Н    | L   | 2-bit  |     | ľΗ. | L   | L   | н    | L    | Н    | Ľ |

| L  | L   | L     | Н     | L    | Н     | Н     | 2-bit | L | Н  | L   | Н  | L    | Н    | Н   | DB3    |     | н   | L   | L   | Н    | L    | Н    | Н |

| L  | L   | L     | Н     | Н    | L     | L     | unc   | L | Н  | L   | Н  | Н    | L    | L   | 2-bit  |     | н   | L   | L   | н    | н    | L    | L |

| L  | L   | L     | н     | Н    | L     | н     | 2-bit | L | Н  | L   | Н  | н    | L    | н   | DB2    |     | н   | L   | L   | Ή    | Н    | L    | н |

| L  | L   | L     | Н     | Н    | Н     | L     | 2-bit | L | Н  | L   | Н  | н    | Н    | L   | unc    |     | Н   | L   | L   | Н    | Н    | Н    | L |

| L  | L   | L     | Н     | Н    | Н     | Н     | DB30  | L | Н  | L   | Н  | Н    | Н    | Н   | 2-bit  |     | н   | L   | L   | Н    | Н    | Н    | Н |

| L  | L   | н     | L     | L    | L     | L     | 2-bit | L | Н  | н   | L  | Ъ    | L    | L   | DB0    |     | н   | L   | н   | L    | L    | L    | L |

| L  | L   | Н     | L     | L    | L     | н     | unc   | L | Н  | н   | L  | L    | L    | Н   | 2-bit  |     | Н   | L   | Н   | L    | L    | L    | н |

| L  | L   | Н     | L     | L    | Н     | L     | DB29  | L | н  | Н   | L. | L    | Н    | L   | 2-bit  |     | Н   | L   | Н   | L    | L    | Н    | L |

| L  | L   | Н     | L     | L    | Н     | Н     | 2-bit | L | Н  | Н   | L  | L    | Н    | Н   | unc    |     | н   | L   | Н   | L    | L    | Н    | Н |

| L  | L   | Н     | L     | Н    | L     | L     | DB28  | L | н  | н   | L  | н    | Ľ,   | L   | 2-bit  |     | н   | L   | Н   | L    | Н    | L    | L |

| L  | L   | Н     | L     | Н    | L     | Н     | 2-bit | L | н  | Н   | L  | н    | L    | Н   | DB1    |     | н   | L   | Н   | L    | Н    | L    | н |

| L  | L   | Н     | L     | Н    | Н     | L     | 2-bit | L | Н  | н   | L  | н    | Н    | L   | unc    |     | Н   | L   | Н   | L    | Н    | Н    | L |

| L  | L   | Н     | L     | Н    | Н     | н     | DB27  | L | Н  | Н   | L  | Н    | Н    | Н   | 2-bit  |     | н   | L   | Н   | L    | Н    | Н    | Н |

| L  | L   | н     | Н     | L    | L     | L     | DB26  | Ľ | н  | н   | Н  | L    | L    | L   | 2-bit  |     | н   | L   | н   | Н    | L    | L    | L |

| L  | L   | Н     | н     | L    | L     | Н     | 2-bit | Ľ | н  | Н   | Н  | L    | L    | Н   | unc    |     | н   | L   | Н   | Н    | L    | L    | н |

| L  | L   | Н     | Н     | L    | Н     | L     | 2-bit | L | Н  | н   | Н  | L    | Н    | L   | unc    |     | Н   | L   | Н   | Н    | L    | Н    | L |

| L  | L   | Н     | Н     | L    | Н     | Н     | DB25  | L | Н  | Н   | Н  | L    | Н    | Н   | 2-bit  |     | Н   | L   | Н   | Н    | L    | Н    | Н |

| L  | L   | Н     | Н     | Н    | L     | L     | 2-bit | L | н  | н   | Н  | н    | L    | L   | unc    |     | н   | L   | н   | н    | Н    | L    | L |

| L  | L   | Н     | Н     | Н    | L     | Н     | DB24  | L | Н  | Н   | Н  | Н    | L    | н   | 2-bit  |     | н   | L   | н   | Н    | Н    | L    | Н |

| L  | L   | Н     | Н     | Н    | Н     | L     | unc   | L | Н  | Н   | Н  | Н    | Н    | L   | 2-bit  |     | н   | L   | Н   | Н    | Н    | Н    | L |

| L  | L   | Н     | Н     | Н    | Н     | Н     | 2-bit | L | Н  | Н   | Н  | Н    | Н    | Н   | CB6    |     | Н   | L   | Н   | Н    | Н    | Н    | Н |

| СВ | X = | er er | ror i | n ch | eck   | bit ) | x     |   |    |     |    |      |      |     |        |     |     |     |     |      |      |      |   |

| DB | Y = | = er  | ror i | n da | ita b | it Y  |       |   |    |     |    |      |      |     |        |     |     |     |     |      |      |      |   |

| _     |   | Svi | ndr | om | e F | Bits |   |       |

|-------|---|-----|-----|----|-----|------|---|-------|

| Error | 6 | 5   | 4   | 3  | 2   | 1    | 0 | Error |

| 2-bit | н | н   | L   | L  | L   | L    | L | unc   |

| unc   | H | Н   | L   | L  | Ł   | L.   | Н | 2-bit |

| unc   | Н | н   | L   | L  | Ł   | н    | L | 2-bit |

| 2-bit | н | Н   | L   | L  | L   | Н    | Н | DB23  |

| unc   | н | Н   | L   | L  | н   | L    | L | 2-bit |

| 2-bit | н | н   | L   | L  | Н   | L    | Н | DB22  |

| 2-bit | н | н   | L   | L  | Н   | Н    | L | DB21  |

| unc   | н | Н   | L   | L  | Н   | Н    | Н | 2-bit |

| unc   | н | Н   | L   | Н  | L   | L    | L | 2-bit |

| 2-bit | н | н   | L   | н  | L   | L    | Н | DB20  |

| 2-bit | н | н   | L   | н  | L   | н    | L | DB19  |

| DB15  | н | Н   | L   | Н  | L   | Н    | Н | 2-bit |

| 2-bit | н | Н   | L   | Н  | Н   | L    | L | DB18  |

| unc   | н | Н   | L   | Н  | Н   | L    | Н | 2-bit |

| DB14  | н | Н   | L   | Н  | Н   | н    | L | 2-bit |

| 2-bit | н | Н   | L   | Н  | Н   | Н    | Н | CB4   |

| unc   | н | Н   | Н   | L  | L   | L    | L | 2-bit |

| 2-bit | н | н   | н   | L  | L   | L    | Н | DB16  |

| 2-bit | н | н   | н   | L  | L   | Н    | L | unc   |

| DB13  | Н | Н   | Н   | L  | L   | Н    | Н | 2-bit |

| 2-bit | н | Н   | Н   | L  | Н   | L    | L | DB17  |

| DB12  | н | н   | н   | L  | Н   | L    | Н | 2-bit |

| DB11  | н | н   | н   | L  | н   | н    | L | 2-bit |

| 2-bit | н | Н   | Н   | L  | Н   | Н    | Н | CB3   |

| 2-bit | н | Н   | Н   | Н  | L   | L    | L | unc   |

| DB10  | Н | Н   | Н   | Н  | L   | L    | Н | 2-bit |

| DB9   | н | Н   | Н   | Н  | L   | Н    | L | 2-bit |

| 2-bit | н | Н   | Н   | Н  | L   | Н    | Н | CB2   |

| DB8   | н | Н   | Н   | Н  | н   | L    | L | 2-bit |

| 2-bit | н | Н   | Н   | Н  | Н   | L    | Н | CB1   |

| 2-bit | н | Н   | Н   | Н  | Н   | Н    | L | CB0   |

| CB5   | н | Н   | н   | н  | н   | н    | н | none  |

2-bit = double-bit error

unc = uncorrectable multibit error

|                 |                                    |                        | ТА         | BLE VI. Read                | d-Modify | -Write Functio              | n                              |               |                        |

|-----------------|------------------------------------|------------------------|------------|-----------------------------|----------|-----------------------------|--------------------------------|---------------|------------------------|

| MEMORY<br>CYCLE | EDAC FUNCTION                      | CON <sup>-</sup><br>S1 | FROL<br>S0 | BYTEn†                      | OEBn†    | DB OUTPUT<br>LATCH<br>LEDBO | CHECK I/O                      | CB<br>CONTROL | ERROR FLAG<br>ERR MERR |

| Read            | Read & Flag                        | Н                      | L          | Input                       | Н        | Х                           | Input                          | Н             | Enabled                |

| Read            | Latch input data<br>& check bits   | Н                      | н          | Input<br>data<br>latched    | н        | L                           | Input<br>check word<br>latched | Н             | Enabled                |

|                 | Latch corrected                    |                        |            | Output                      |          |                             | Hi-Z                           | Н             |                        |

| Read            | data word into<br>output latch     | Н                      | Н          | data<br>word<br>latched     | н        | н                           | Output<br>Syndrome<br>bits     | L             | Enabled                |

| Modify          | Modify appropriate byte or bytes & |                        | 1          | Input<br>modified<br>BYTE0  | н        | н                           | Output                         | L             | нн                     |

| /write          | generate new<br>check word         | L                      | L          | Ouput<br>unchanged<br>BYTE0 | L        |                             | check word                     | Ľ             |                        |

†OEB0 controls DB₀-DB₂ (BYTE0), OEB1 controls DB₀-DB₁5 (BYTE1), OEB2 controls DB16-DB23 (BYTE2), OEB3 controls DB24-DB31 (BYTE3).

### Read-Modify-Write (Byte Control) Operations

The DP8402A and DP8403 devices are capable of bytewrite operations. The 39-bit word from memory must first be latched into the DB and CB input latches. This is easily accomplished by switching from the read and flag mode (S1 = H, SO = L) to the latch input mode (S1 = H, S0 = H). The EDAC will then make any corrections, if necessary, to the data word and place it at the input of the output data latch. This data word must then be latched into the output data latch by taking LEDBO from a low to a high.

Byte control can now be employed on the data word through the  $\overline{OEB0}$  through  $\overline{OEB3}$  controls.  $\overline{OEB0}$  controls DB0-DB7 (byte 0),  $\overline{OEB1}$  controls DB8-DB15 (byte 1),  $\overline{OEB2}$  controls DB16-DB23 (byte 2), and  $\overline{OEB3}$  controls DB24-DB31 (byte 3). Placing a high on the byte control will disable the output and the user can modify the byte. If a low is placed on the byte control, then the original byte is allowed to pass onto the data bus unchanged. If the original data word is altered through byte control, a new check word must be generated before it is written back into memory. This is easily accomplished by taking control S1 and S0 low. Table VI lists the read-modify-write functions.

#### **Diagnostic Operations**

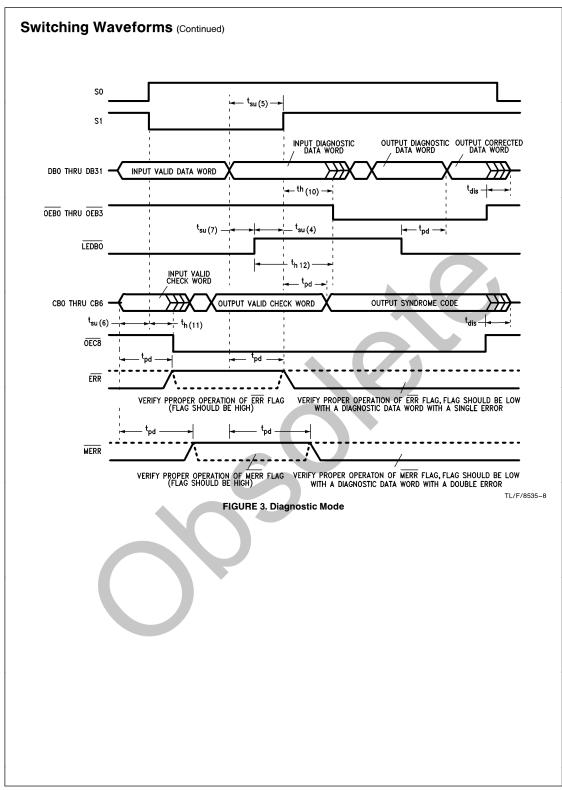

The DP8402A thru DP8405 are capable of diagnostics that allow the user to determine whether the EDAC or the memory is failing. The diagnostic function tables will help the user to see the possibilities for diagnostic control.

In the diagnostic mode (S1 = L, S0 = H), the checkword is latched into the input latch while the data input remains transparent. This lets the user apply various data words against a fixed known checkword. If the user applies a diagnostic data word with an error in any bit location, the  $\overline{\text{ERR}}$ flag should be low. If a diagnostic data word with two errors in any bit location is applied, the MERR flag should be low. After the checkword is latched into the input latch, it can be verified by taking OECB low. This outputs the latched checkword. With the DP8402A and DP8403, the diagnostic data word can be latched into the output data latch and verified. It should be noted that the DP8404 and DP8405 do not have this pass-through capability because they do not contain an output data latch. By changing from the diagnostic mode (S1 = L, S0 = H) to the correction mode (S1 = H, S0 = H), the user can verify that the EDAC will correct the diagnostic data word. Also, the syndrome bits can be produced to verify that the EDAC pinpoints the error location. Table VII DP8402A and DP8403 and Table VIII DP8404 and DP8405 list the diagnostic functions.

|                                                                            | CONT | ROL |                                                | DB BYTE<br>CONTROL | DB OUTPUT<br>LATCH | CHECK I/O                                  | CB<br>CONTROL | ERROF   | R FLAGS |

|----------------------------------------------------------------------------|------|-----|------------------------------------------------|--------------------|--------------------|--------------------------------------------|---------------|---------|---------|

| EDAC FUNCTION                                                              | S1   | S0  | DATA I/O                                       | OEBn               | LEDBO              |                                            | OECB          | ERR     | MERR    |

| Read & flag                                                                | Н    | L   | Input correct<br>data word                     | Н                  | х                  | Input correct check bits                   | Н             | н       | Н       |

| Latch input check<br>word while data<br>input latch remains<br>transparent | L    | Н   | Input<br>diagnostic<br>data word†              | Н                  | L                  | Input<br>check bits<br>latched             | Н             | Ena     | abled   |

| Latch diagnostic data word into                                            | L    | н   | Input<br>diagnostic                            | н                  | Н                  | Output latched check bits                  | L             | Ena     | abled   |

| output latch                                                               |      |     | data word†                                     |                    |                    | Hi-Z                                       | н             | Enabled |         |

| Latch diagnostic<br>data word into<br>input latch                          | Н    | Н   | Input<br>diagnostic<br>data word               | Н                  | Н                  | Output<br>syndrome<br>bits                 | L             | Ena     | abled   |

| inputiation                                                                |      |     | latched                                        |                    |                    | Hi-Z                                       | Н             |         |         |

| Output diagnostic<br>data word &<br>syndrome bits                          | Н    | н   | Output<br>diagnostic<br>data word              | L                  | Н                  | Output<br>syndrome<br>bits                 |               | Ena     | abled   |

| Output corrected<br>diagnostic data<br>word & output<br>syndrome bits      | Н    | Н   | Output<br>corrected<br>diagnostic<br>data word | L                  | L                  | Hi-Z<br>Output<br>syndrome<br>bits<br>Hi-Z | H             | Ena     | abled   |

two bit locations.

#### TABLE VIII. DP8404, DP8405 Diagnostic Function

| EDAC FUNCTION                                                              | CONT<br>S1 | FROL<br>S0 | DATA I/O                          | DB CONTROL | СНЕСК І/О                      | DB CONTROL |     | FLAGS<br>MERR |

|----------------------------------------------------------------------------|------------|------------|-----------------------------------|------------|--------------------------------|------------|-----|---------------|

| Read & flag                                                                | Н          | L          | Input correct data word           | н          | Input correct<br>check bits    | н          | Н   | н             |

| Latch input check<br>bits while data<br>input latch remains<br>transparent | L          | Н          | Input<br>diagnostic<br>data word† | Н          | Input<br>check bits<br>latched | Н          | Ena | bled          |

| Output input<br>check bits                                                 | L          | н          | Input<br>diagnostic<br>data word† | Н          | Output input check bits        | L          | Ena | bled          |

| Latch diagnostic<br>data into                                              | T          | Н          | Input<br>diagnostic               | н          | Output<br>syndrome bits        | L          | Ena | bled          |

| input latch                                                                |            |            | data word<br>latched              |            | Hi-Z                           | н          | End | 5104          |

| Output corrected diagnostic                                                | н          | н          | Output corrected diagnostic       | L          | Output<br>syndrome bits        | L          | Ena | bled          |

| data word                                                                  |            |            | data word                         |            | Hi-Z                           | Н          |     |               |

† Diagnostic data is a data word with an error in one bit location except when testing the MERR error flag. In this case, the diagnostic data word will contain errors in two bit locations.

| Supply             | Derating Free-Air Temperatu<br>Voltage, V <sub>CC</sub> (See Note 1)<br>foltage: CB and DB<br>All Others | ure Range (unless otherwise noted)<br>7V Operating Free<br>5.5V<br>7V Storage Tempe                  |     |               | Co   | ommer | rcial  | 2 to + 1<br>0° to +<br>2 to + 1 | 70°C  |

|--------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|---------------|------|-------|--------|---------------------------------|-------|

|                    | ommended Opera                                                                                           |                                                                                                      |     | Militar       | v    | Co    | omme   | rcial                           |       |

| Symbol             | Parameter                                                                                                | Conditions                                                                                           | Min | Тур           | Max  | Min   | Тур    | Мах                             | Unite |

| V <sub>CC</sub>    | Supply Voltage                                                                                           |                                                                                                      | 4.5 | 5             | 5.5  | 4.5   | 5      | 5.5                             | V     |

| V <sub>IH</sub>    | High-Level Input Voltage                                                                                 |                                                                                                      | 2   |               |      | 2     |        |                                 | V     |

| V <sub>IL</sub>    | Low-Level Input Voltage                                                                                  |                                                                                                      |     |               | 0.8  |       |        | 0.8                             | V     |

| I <sub>OH</sub>    | High-Level Output Current                                                                                | ERR Or MERR                                                                                          |     |               | -0.4 |       |        | -0.4                            | mA    |

| .011               |                                                                                                          | DB Or CB DP8402A, DP8404                                                                             |     |               | -1   |       |        | -2.6                            |       |

| IOL                | Low-Level Output Current                                                                                 | ERR Or MERR                                                                                          |     |               | 4    |       |        | 8                               | mA    |

|                    |                                                                                                          | DB or CB                                                                                             |     |               | 12   |       |        | 24                              |       |

| tw                 | Pulse Duration                                                                                           | LEDBO Low                                                                                            | 25  |               |      | 25    |        |                                 | ns    |

|                    |                                                                                                          | (1) Data And Check Word Before S0 ↑<br>(S1 = H)                                                      | 15  |               |      | 10    |        | 2                               |       |

|                    |                                                                                                          | (2) SO High Before $\overline{\text{LEDBO}} \uparrow (S1 = H)^{\dagger}$                             | 45  |               |      | 45    |        |                                 |       |

|                    | Setun Time                                                                                               | (3) $\overline{\text{LEDBO}}$ High Before The Earlier of S0 $\downarrow$ or S1 $\downarrow$ †        | 0   |               |      | 0     |        |                                 |       |

| t <sub>su</sub>    | Setup Time                                                                                               | (4) $\overline{\text{LEDBO}}$ High Before S1 $\uparrow$ (S0 = H)                                     | 0   |               |      | 0     |        |                                 | ns    |

|                    |                                                                                                          | (5) Diagnostic Data Word Before S1 $\uparrow$ (S0 = H)                                               | 15  |               |      | 10    |        |                                 |       |

|                    |                                                                                                          | (6) Diagnostic Check Word Before<br>The Later Of S1 $\downarrow$ or S0 $\uparrow$                    | 15  |               |      | 10    |        |                                 |       |

|                    |                                                                                                          | (7) Diagnostic Data Word Before<br><u>LEDBO</u> ↑ (S1 = L and S0 = H)‡                               | 25  |               |      | 20    |        |                                 |       |

|                    |                                                                                                          | (8) Read-Mode, S0 Low And S1 High                                                                    | 35  |               |      | 30    |        |                                 |       |

|                    |                                                                                                          | (9) Data And Check Word After S0 $\uparrow$ (S1 = H)                                                 | 20  |               |      | 15    |        | -                               |       |

| t <sub>h</sub>     | Hold Time                                                                                                | (10) Data Word After S1 $\uparrow$ (S0 = H)                                                          | 20  |               |      | 15    |        |                                 | ns    |

| -11                |                                                                                                          | (11) Check Word After The Later of S1 $\downarrow$ or S0 $\uparrow$                                  | 20  |               |      | 15    |        |                                 |       |

|                    |                                                                                                          | (12) Diagnostic Data Word After<br>$\overline{\text{LEDBO}} \uparrow (S1 = L \text{ And } S0 = H)$ ; | 0   |               |      | 0     |        |                                 |       |

| t <sub>corr</sub>  | Correction Time (see Figure                                                                              | 9 1)*                                                                                                | 65  |               |      | 58    |        |                                 | ns    |

| T <sub>A</sub>     | Operating Free-Air Tempera                                                                               | ature                                                                                                | -55 |               | 125  | 0     |        | 70                              | °C    |

| *This sp<br>†These | ecification may be interpreted as the<br>imes ensure that corrected data is s                            | e maximum delay to guarantee valid corrected data at the o                                           |     | <br>I include |      |       | lelay. | 70                              |       |

| 0                | Demonstern  | To at Oan ditions                         | I          | Military |      | Co         | mmercia | al   |       |

|------------------|-------------|-------------------------------------------|------------|----------|------|------------|---------|------|-------|

| Symbol           | Parameter   | Test Conditions                           | Min        | Тур†     | Max  | Min        | Тур†    | Max  | Units |

| V <sub>IK</sub>  |             | $V_{CC} = 4.5V, I_I = -18 \text{ mA}$     |            |          | -1.5 |            |         | -1.5 | V     |

|                  | All outputs | $V_{CC}=$ 4.5V to 5.5V, $I_{OH}=-$ 0.4 mA | $V_{CC}-2$ |          |      | $V_{CC}-2$ |         |      |       |

| V <sub>OH</sub>  |             | $V_{CC} = 4.5V, I_{OH} = -1 \text{ mA}$   | 2.4        | 3.3      |      |            |         |      | v     |

|                  | DB or CB    | $V_{CC} = 4.5V, I_{OH} = -2.6 \text{ mA}$ |            |          |      | 2.4        | 3.2     |      |       |

|                  | ERR or MERR | $V_{CC} = 4.5V, I_{OL} = 4 \text{ mA}$    |            | 0.25     | 0.4  |            | 0.25    | 0.4  |       |

|                  |             | $V_{CC} = 4.5V, I_{OL} = 8 \text{ mA}$    |            |          |      |            | 0.35    | 0.5  |       |

| V <sub>OL</sub>  |             | $V_{CC} = 4.5V, I_{OL} = 12 \text{ mA}$   |            | 0.25     | 0.4  |            | 0.25    | 0.4  | V     |

|                  | DB or CB    | $V_{CC} = 4.5V, I_{OL} = 24 \text{ mA}$   |            |          |      |            | 0.35    | 0.5  |       |

|                  | S0 or S1    | $V_{CC} = 5.5V, V_1 = 7V$                 |            |          | 0.1  |            |         | 0.1  |       |

| lj –             | All others  | $V_{CC} = 5.5V, V_{I} = 5.5V$             |            |          | 0.1  |            |         | 0.1  | mA    |

|                  | S0 or S1    |                                           |            |          | 20   |            |         | 20   |       |

| Ι <sub>Η</sub>   | All others‡ | $V_{CC} = 5.5V, V_{I} = 2.7V$             |            |          | 20   |            |         | 20   | μΑ    |

|                  | S0 or S1    |                                           |            |          | -0.4 |            |         | -0.4 |       |

| Ι <sub>ΙL</sub>  | All others‡ | $V_{CC} = 5.5V, V_{I} = 0.4V$             |            |          | -0.1 |            |         | -0.1 | mA    |

| l <sub>O</sub> § |             | $V_{CC} = 5.5V, V_{O} = 2.25V$            | -30        |          | -112 | -30        |         | -112 | mA    |

| Icc              |             | V <sub>CC</sub> = 5.5V, (See Note 1)      |            | 150      | 250  |            | 150     | 250  | mA    |

## DP8403, DP8405 Electrical Characteristics

Over Recommended Operating Free-Air Temperature Range (unless otherwise noted)

|                  | -           | <b>T ( 0 ) (1)</b>                          |                    | Military |      | Co         | mmerci | al   |       |

|------------------|-------------|---------------------------------------------|--------------------|----------|------|------------|--------|------|-------|

| Symbol           | Parameter   | Test Conditions                             | Min                | Тур†     | Max  | Min        | Тур†   | Max  | Units |

| V <sub>IK</sub>  |             | $V_{CC} = 4.5V, I_I = -18 \text{ mA}$       |                    |          | -1.5 |            |        | -1.5 | V     |

| V <sub>OH</sub>  | ERR or MERR | $V_{CC} = 4.5V$ to 5.5V, $I_{OH} = -0.4$ mA | V <sub>CC</sub> -2 |          |      | $V_{CC}-2$ |        |      | V     |

| I <sub>OH</sub>  | DB or CB    | $V_{CC} = 4.5V, V_{OH} = 5.5V$              |                    |          | 0.1  |            |        | 0.1  | mA    |

|                  | ERR or MERR | $V_{CC} = 4.5V, I_{OL} = 4 \text{ mA}$      |                    | 0.25     | 0.4  |            | 0.25   | 0.4  |       |

|                  | ERR OF MERR | $V_{CC} = 4.5V, I_{OL} = 8 \text{ mA}$      |                    |          |      |            | 0.35   | 0.5  |       |

| V <sub>OL</sub>  |             | $V_{CC} = 4.5V, I_{OL} = 12 \text{ mA}$     |                    | 0.25     | 0.4  |            | 0.25   | 0.4  | V     |

|                  | DB or CB    | $V_{CC} = 4.5V, I_{OL} = 24 \text{ mA}$     |                    |          |      |            | 0.35   | 0.5  |       |

|                  | S0 or S1    | $V_{CC} = 5.5V, V_I = 7V$                   |                    |          |      |            |        |      |       |

| II               | All others  | $V_{CC} = 5.5V, V_1 = 5.5V$                 |                    |          |      |            |        |      | mA    |

|                  | S0 or S1    |                                             |                    |          |      |            |        |      |       |

| Ι <sub>Η</sub>   | All others‡ | $V_{CC} = 5.5V, V_{I} = 2.7V$               |                    |          |      |            |        |      | μA    |

|                  | S0 or S1    |                                             |                    |          |      |            |        |      |       |

| IIL              | All others‡ | $V_{CC} = 5.5V, V_I = 0.4V$                 |                    |          |      |            |        |      | mA    |

| l <sub>O</sub> § | ERR or MERR | $V_{CC} = 5.5 V, V_{O} = 2.25 V$            | -30                |          | -112 | -30        |        | -112 | mA    |

| Icc              |             | V <sub>CC</sub> = 5.5V, (See Note 1)        |                    | 150      |      |            | 150    |      | mA    |

†All typical values are at V\_{CC} = 5V, T\_A = +25^{\circ}C.

$\ddagger$  For I/O ports (QA through QH), the parameters  $I_{IH}$  and  $I_{IL}$  include the off-state output current.

The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

Note 1:  $I_{\mbox{CC}}$  is measured with S0 and S1 at 4.5V and all CB and DB pins grounded.

| Symbol           | From             | То       | Test Conditions                       |     | Military |              | Commercial |      |

|------------------|------------------|----------|---------------------------------------|-----|----------|--------------|------------|------|

| oynize.          | (Input)          | (Output) |                                       | Min | Max      | Min          | Max        | Unit |

| t <sub>pd</sub>  | DB and CB        | ERR      | $S1 = H, S0 = L, R_L = 500\Omega$     | 10  | 43       | 10           | 40         | ns   |

| ۰pa              | DB               | ERR      | $S1=L,S0=H,R_{L}=500\Omega$           | 10  | 43       | 10           | 40         | 113  |

| t                | DB and CB        | MERR     | $S1 = H, S0 = L, R_L = 500\Omega$     | 15  | 67       | 15           | 55         | ns   |

| t <sub>pd</sub>  | DB               | MERR     | $S1 = L, S0 = H, R_L = 500\Omega$     | 15  | 67       | 15           | 55         |      |

| t <sub>pd</sub>  | S0↓ and S1↓      | СВ       | $R1 = R2 = 500\Omega$                 | 10  | 60       | 10           | 48         | ns   |

| t <sub>pd</sub>  | DB               | СВ       | $S1 = L, S0 = L, R1 = R2 = 500\Omega$ | 10  | 60       | 10           | 48         | ns   |

| t <sub>pd</sub>  | LEDB0↓           | DB       | $S1 = X, S0 = H, R1 = R2 = 500\Omega$ | 7   | 35       | 7            | 30         | ns   |

| t <sub>pd</sub>  | S1 ↑             | СВ       | $S0 = H, R1 = R2 = 500\Omega$         | 10  | 60       | 10           | 50         | ns   |

| t <sub>en</sub>  | <u>OECB</u> ↓    | СВ       | $S0 = H, S1 = X, R1 = R2 = 500\Omega$ | 2   | 30       | 2            | 25         | ns   |

| t <sub>dis</sub> | <u>OECB</u> ↑    | СВ       | $S0 = H, S1 = X, R1 = R2 = 500\Omega$ | 2   | 30       | 2            | 25         | ns   |

| t <sub>en</sub>  | OEB0 thru OEB3↓  | DB       | $S0 = H, S1 = X, R1 = R2 = 500\Omega$ | 2   | 30       | 2            | 25         | ns   |

| t <sub>dis</sub> | OEB0 thru OEB3 ↑ | DB       | $S0 = H, S1 = X, R1 = R2 = 500\Omega$ | 2   | 30       | 2            | 25         | ns   |

|                  |                  |          |                                       |     |          | $\mathbf{C}$ |            |      |

| Symbol           | From                                | То       | Test Conditions                   | Military |      | Commercial |     |      | Units |    |

|------------------|-------------------------------------|----------|-----------------------------------|----------|------|------------|-----|------|-------|----|

| Symbol           | (Input)                             | (Output) |                                   | Min      | Тур† | Max        | Min | Тур† | Max   |    |

| t <sub>pd</sub>  | DB and CB                           | ERR      | $S1 = H, S0 = L, R_L = 500\Omega$ |          | 26   |            |     | 26   |       | ns |

| чра              | DB                                  | ERR      | $S1 = L, S0 = H, R_L = 500\Omega$ |          | 26   |            |     | 26   |       |    |

|                  | DB and CB                           |          | $S1 = H, S0 = L, R_L = 500\Omega$ |          | 40   |            |     | 40   |       | ns |

| t <sub>pd</sub>  |                                     | MERR     | $S1 = L, S0 = H, R_L = 500\Omega$ |          | 40   |            |     | 40   |       |    |

| t <sub>pd</sub>  | S0 $\downarrow$ and S1 $\downarrow$ | СВ       | $R_L = 680\Omega$                 |          | 40   |            |     | 40   |       | ns |

| t <sub>pd</sub>  | DB                                  | СВ       | $S1 = L, S0 = L, R_L = 680\Omega$ |          | 40   |            |     | 40   |       | ns |

| t <sub>pd</sub>  | LEDB0                               | DB       | $S1 = X, S0 = H, R_L = 680\Omega$ |          | 26   |            |     | 26   |       | ns |

| t <sub>pd</sub>  | S1 ↑                                | СВ       | $S0 = H, R_L = 680\Omega$         |          | 40   |            |     | 40   |       | ns |

| t <sub>PLH</sub> | <u>OECB</u> ↑                       | СВ       | $S1 = X, S0 = H, R_L = 680\Omega$ |          | 24   |            |     | 24   |       | ns |

| t <sub>PHL</sub> | <u>OECB</u> ↓                       | СВ       | $S1 = X, S0 = H, R_L = 680\Omega$ |          | 24   |            |     | 24   |       | ns |

| t <sub>PLH</sub> | OEB0 thru OEB3 ↑                    | DB       | $S1 = X, S0 = H, R_L = 680\Omega$ |          | 24   |            |     | 24   |       | ns |

| t <sub>PHL</sub> | OEB0 thru OEB3 ↓                    | DB       | $S1 = X, S0 = H, R_L = 680\Omega$ |          | 24   |            |     | 24   |       | ns |

|                  |                                     | 1.0540   |                                   |          |      |            |     |      |       |    |

†All typical values are at  $V_{CC}$  = 5V,  $T_{A}$  = +25°C.

| Symbol           | From                                | То       | Test Conditions                       | Military |      |     | Commercial |      |     | Units |  |

|------------------|-------------------------------------|----------|---------------------------------------|----------|------|-----|------------|------|-----|-------|--|

| Cymber           | (Input)                             | (Output) |                                       |          | Тур† | Max | Min        | Тур† | Max | 0.110 |  |

| t <sub>pd</sub>  | DB and CB                           | ERR      | $S1 = H, S0 = L, R_L = 500\Omega$     |          | 26   |     |            | 26   |     | ns    |  |

| чра              |                                     | Liut     | $S1 = L, S0 = H, R_L = 500\Omega$     |          | 26   |     |            | 26   |     |       |  |

| t . DR and CR    | DB and CB                           | MERR     | $S1 = H, S0 = L, R_L = 500\Omega$     |          | 40   |     |            | 40   |     | ns    |  |

| t <sub>pd</sub>  |                                     |          | $S1 = L, S0 = H, R_L = 500\Omega$     |          | 40   |     |            | 40   |     |       |  |

| t <sub>pd</sub>  | S0 $\downarrow$ and S1 $\downarrow$ | СВ       | $R1 = R2 = 500\Omega$                 |          | 35   |     |            | 35   |     | ns    |  |

| t <sub>pd</sub>  | DB                                  | СВ       | $S1 = L, S0 = L, R1 = R2 = 500\Omega$ |          | 35   |     |            | 35   |     | ns    |  |

| t <sub>pd</sub>  | S1 ↑                                | СВ       | $S0 = H, R1 = R2 = 500\Omega$         |          | 35   |     |            | 35   |     | ns    |  |

| t <sub>en</sub>  | <u>OECB</u> ↓                       | СВ       | $S1 = X, S0 = H, R1 = R2 = 500\Omega$ |          | 18   |     |            | 18   |     | ns    |  |

| t <sub>dis</sub> | OECB ↑                              | СВ       | $S1 = X, S0 = H, R1 = R2 = 500\Omega$ |          | 18   |     |            | 18   |     | ns    |  |

| t <sub>en</sub>  | <u>OECB</u> ↓                       | DB       | $S1 = X, S0 = H, R1 = R2 = 500\Omega$ |          | 18   |     |            | 18   |     | ns    |  |

| t <sub>dis</sub> | <u>OECB</u> ↑                       | DB       | $S1 = X, S0 = H, R1 = R2 = 500\Omega$ |          | 18   |     |            | 18   |     | ns    |  |

# DP8405 Switching Characteristics, $V_{CC} = 4.5V$ to 5.5V, $C_L = 50$ pF, $T_A = Min$ to Max

|                                                                               | From                                | То       | Test Conditions                                                                   | Military |      |     | Commercial |      |     | Units |

|-------------------------------------------------------------------------------|-------------------------------------|----------|-----------------------------------------------------------------------------------|----------|------|-----|------------|------|-----|-------|

| Symbol                                                                        | (Input)                             | (Output) | Test conditions                                                                   | Min      | Тур† | Max | Min        | Тур† | Max | Units |

| t <sub>pd</sub>                                                               | DB and CB                           | ERR      | $S1 = H, S0 = L, R_L = 500\Omega$                                                 |          | 26   |     |            | 26   |     | ns    |

| чра                                                                           | DB                                  | ERR      | $S1=L,S0=H,R_{L}=500\Omega$                                                       |          | 26   |     |            | 26   |     | 115   |

| tea                                                                           | DB and CB                           | MERR     | $S1 = H, S0 = L, R_L = 500\Omega$                                                 |          | 40   |     |            | 40   |     | ns    |

| t <sub>pd</sub>                                                               | DD and OD                           |          | $\mathrm{S1}=\mathrm{L},\mathrm{S0}=\mathrm{H},\mathrm{R}_{\mathrm{L}}=500\Omega$ |          | 40   |     |            | 40   |     | 113   |

| t <sub>pd</sub>                                                               | S0 $\downarrow$ and S1 $\downarrow$ | СВ       | $R_L = 680\Omega$                                                                 |          | 40   |     |            | 40   |     | ns    |

| t <sub>pd</sub>                                                               | DB                                  | СВ       | $S1=L, S0=L, R_L=680\Omega$                                                       |          | 40   |     |            | 40   |     | ns    |

| t <sub>pd</sub>                                                               | S1 ↑                                | DB       | $SO = H, R_L = 680\Omega$                                                         |          | 40   |     |            | 40   |     | ns    |

| t <sub>PLH</sub>                                                              | <u>OECB</u> ↑                       | CB       | $\text{S1}=\text{X}, \text{S0}=\text{H}, \text{R}_{\text{L}}=500\Omega$           |          | 24   |     |            | 24   |     | ns    |

| t <sub>PHL</sub>                                                              | <u>OECB</u> ↓                       | СВ       | $S1 = X, S0 = H, R_L = 680\Omega$                                                 |          | 24   |     |            | 24   |     | ns    |

| t <sub>PLH</sub>                                                              | <u>OEDB</u> ↑                       | DB       | $S1=X,S0=H,R_{L}=680\Omega$                                                       |          | 24   |     |            | 24   |     | ns    |

| t <sub>PHL</sub>                                                              | <u>OEDB</u> ↓                       | DB       | $S1=X,S0=H,R_L=680\Omega$                                                         |          | 24   |     |            | 24   |     | ns    |

| $\dagger A \parallel$ typical values are at Voc = 5V. T <sub>A</sub> = +25°C. |                                     |          |                                                                                   |          |      |     |            |      |     |       |

†All typ

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated