# National Semiconductor

## PRELIMINARY

# DP83856 100 Mb/s Repeater Information Base

# **General Description**

The DP83856 100 Mb/s Repeater Information Base is designed specifically to meet the management demands of today's high speed Ethernet networking systems.

The DP83856 simplifies design of managed multiport repeaters. Used in conjunction with up to 16 DP83850s it enables a repeater system to become a single managed entity that is fully compatible with the IEEE 802.3u clause 30 management requirements.

The DP83856 device incorporates all the necessary functions and counters for collecting network statistics. Information is gathered on a per-packet, per-port basis: the port which is receiving the packet is the active port for statistics collection.

## **Features**

- Supports up to 16 DP83850 Repeater Interface Controllers (192, 100 Mb/s ports on one segment)

- Fully IEEE 802.3u clause 30 compatible

- Network management statistics processed on a per activity (per packet) basis

- Programmed I/O interface for statistics reporting

- Uses external SRAM to maintain per port network management statistics counters

- Single interrupt acknowledgement provides report on all per port SRAM based and DP83856 based statistics

- Parallel register interface to CPU (16-bit)

- Allows indirect access to the DP83850 Repeater Interface Controller and DP83840 Physical Layer Device serial registers through a parallel register interface

- 132-pin PQFP

#### System Diagram MANAGEMENT MANAGEMENT MANAGEMENT MEMORY/CODE I/O DEVICE/S CPU CPU BUS DP83856 STATISTICS 100 Mb/s SRAM REPEATER INFORMATION BASE INTER REPEATER BUS, TX BUS AND SERIAL MANAGEMENT BUS SIGNALS DP83850 100 Mb/s REPEATER DP83850 100 Mb/s REPEATER INTERFACE CONTROL INTERFACE CONTROL 100 Mb/s 100 Mb/s 100 Mb/s 100 Mb/s 100 Mb/s 100 Mb/s **PHY #1** PHY #2 PHY #12 PHY #13 PHY #14 PHY #24 TL/F/12392-1

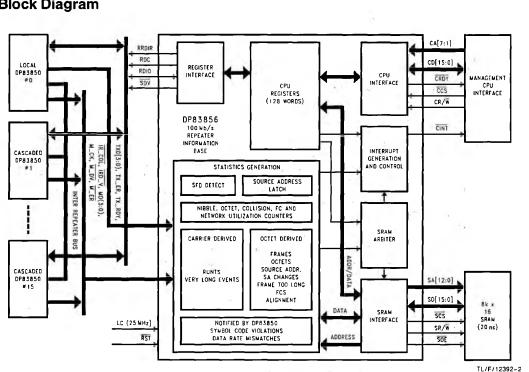

## **Block Diagram**

## **Table of Contents**

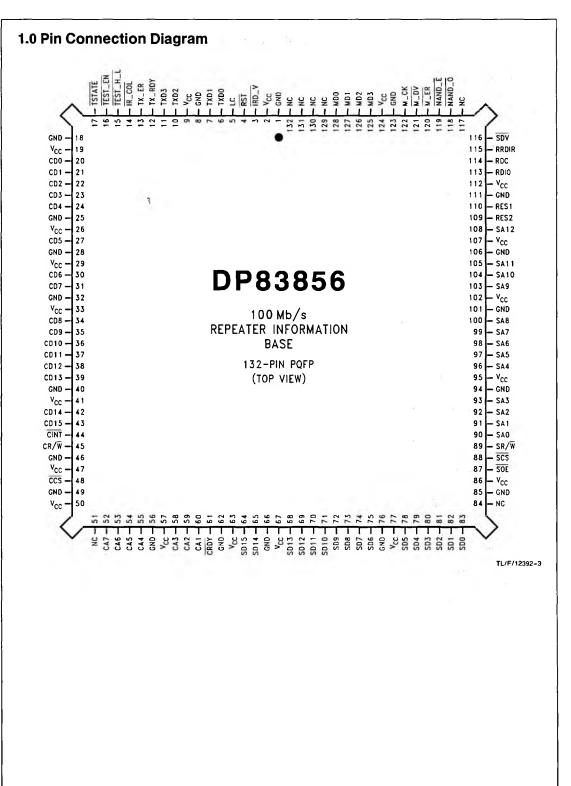

#### **1.0 PIN CONNECTION DIAGRAM**

#### 2.0 PIN DESCRIPTION

- 2.1 CPU Interface

- 2.2 SRAM Interface

- 2.3 Transmit Bus and Management Bus

- 2.4 MII Interface

- 2.5 Test Interface

- 2.6 Miscellaneous Pins

- 2.7 Pin Type Designation

## **3.0 FUNCTIONAL DESCRIPTION**

- 3.1 Statistics Generation

- 3.2 SRAM Interface

- 3.3 SRAM Arbiter

- 3.4 Interrupt Generation and Control

- 3.5 MII Register Interface

- 3.6 CPU Register Block

- 3.7 Management Data Interface

## 4.0 REGISTERS

- 4.1 Register Memory Map

- 4.2 Configuration Register

- 4.3 Interrupt Register

- 4.4 SRAM Interface Register

- 4.5 MII Management Interface Register

- 4.6 SRAM Write Data Register

- 4.7 MII Write Data Register

- 4.8 Device ID Register

- 4.9 SRAM Read Data Registers

- 4.10 Carrier Count Register

- 4.11 Oct\_Nib Count Register

- 4.12 Network Counters

- 4.13 MII Read Data Registers

#### 5.0 DP83956 Initialization

- 5.1 SRAM Test and Initialization

- 5.2 Network Counter Initialization

- 5.3 Interrupt Initialization and Usage

#### 6.0 Repeater MIB Support

6.1 Repeater MIB Support

## 7.0 AC AND DC SPECIFICATIONS

- 7.1 DC Specifications

- 7.2 AC Specifications

4-112

# DP83856

# 2.0 Pin Description

## 2.1 CPU INTERFACE

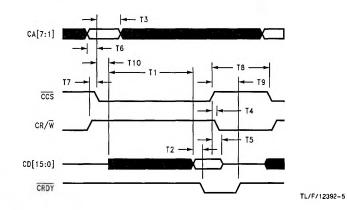

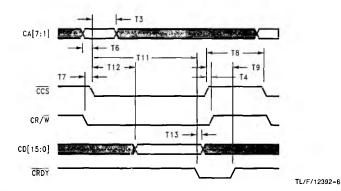

The CPU interface pins are a set of generic interface signals designed to accommodate many different CPU types with minimal external logic. The data interface is 16-bits wide and does not provide any steering capabilities. Furthermore, all accesses must be aligned on 16-bit boundaries, as indicated in the CPU Register Map Section 4.

| Signal Name | Туре     | Active | Description                                                                                                                                                                                                                                                                         |

|-------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CINT        | 0/Z, L   | Low    | CPU INTERRUPT: Indicates that the DP83856 has at least one interrupt pending. The CINT signal will remain active until the CPU reads the Interrupt Register. It is software's responsibility to keep track of multiple interrupts pending, and service all of the interrupts.       |

| CRDY        | 0/Z, L   | Low    | CPU READY: Indicates that the DP83856 is ready to terminate the current cycle. The DP83856 asserts CRDY on writes once it has strobed the data into its write data holding register. The DP83856 asserts CRDY on reads once it has strobed data into its read data output register. |

| CCS         | 1        | Low    | CPU CHIP SELECT: Chip select for internal DP83856 registers. Generated by external logic<br>as an address decode of the DP83856 register space. CCS must remain valid for the entire<br>cycle.                                                                                      |

| CR/W        | I        |        | <b>CPU READ-WRITE:</b> Read/Write strobe for DP83856 internal registers.<br>Read = 1, Write = 0.                                                                                                                                                                                    |

| CA[7:1]     | I        |        | CPU ADDRESS [7:1]: Address bus for DP83856 register accesses. The DP83856 latches the address for internal use within 45 ns of CCS being asserted.                                                                                                                                  |

| CD[15:0]    | 1/O/Z, M |        | CPU DATA [15:0]: 16-bit data bus for DP83856 register accesses. CD[15:0] correspond to the low 16-bits of data on the CPU. The DP83856 implements <b>Big Endian</b> convention for data storage. All CPU register accesses should be 16-bit accesses aligned on 16-bit boundaries.  |

## 2.2 SRAM INTERFACE

The SRAM interface pins are used to connect the DP83856 to a fast (20 ns) external SRAM. The DP83856 supports up to an 8k x 16-bit SRAM configuration. This configuration provides a maximum of 16, 32-bit statistics values per port.

| Signal Name | Туре       | Active | Description                                                                                                           |

|-------------|------------|--------|-----------------------------------------------------------------------------------------------------------------------|

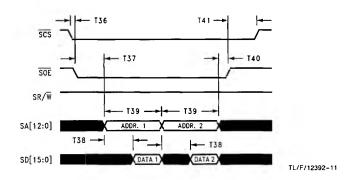

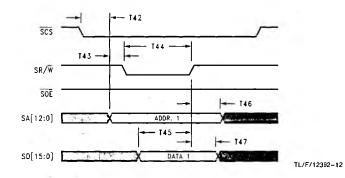

| SA[12:0]    | 0/Z, L     |        | SRAM ADDRESS [12:0]: The SRAM address bus should be directly connected to the fast<br>external SRAM's address inputs. |

| SD[15:0]    | 1/0/Z/P, L |        | SRAM DATA [15:0]: The SRAM data bus, should be directly connected to the fast external SRAM's data pins.              |

| SR/W        | 0/Z, L     |        | SRAM READ-WRITE: Should be directly connected to the fast external SRAM's write enable pin. Read = 1, Write = 0.      |

| SCS         | 0/Z, L     | Low    | SRAM CHIP SELECT: Should be directly connected to the fast external SRAM's active low<br>chip select pin.             |

| SOE         | 0/Z, L     | Low    | SRAM OUTPUT ENABLE: Should be directly connected to the fast external SRAM's (active low) output enable pin.          |

# 2.0 Pin Description (Continued)

## 2.3 TRANSMIT BUS AND MANAGEMENT BUS

| Signal Name | Туре | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

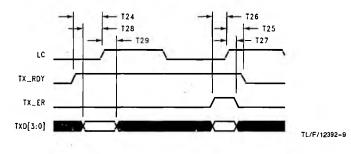

| TXD[3:0]    | I    |        | <b>TRANSMIT DATA [3:0]:</b> Transfers data from a local DP83850 to the DP83856. TXD[3:0] is synchronous to the local clock signal LC, and is framed by the transmit ready signal TX_RDY.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TX_RDY      | I    | High   | TRANSMIT DATA READY: Asserted by a local DP83850 when non-idle symbols are repeated<br>on any of the DP83850's output ports. The DP83856 uses this signal as a framing signal for<br>transmit data, transmit error, management data, management error, collision, data valid, and as<br>an enable for carrier and network utilization timing.                                                                                                                                                                                                                                                                  |

| TXER        | I    | High   | <b>TRANSMIT DATA ERROR:</b> Asserted by a local DP83850 when a transmit error occurs. The DP83856 monitors this signal to determine if the current reception was a Symbol Code violation error. TX_ER is synchronous to the local clock signal LC.                                                                                                                                                                                                                                                                                                                                                             |

| IR_COL      | I    | Low    | INTER REPEATER COLLISION: Asserted by any (all) DP83850s in the system which are<br>currently experiencing a collision. The DP83856 monitors this signal during TX_RDY valid, and<br>uses the information in statistics processing and collision counting.                                                                                                                                                                                                                                                                                                                                                     |

| IRD_V       | Ι    | Low    | INTER REPEATER DATA VALID: Asserted by any DP83850 in the system which has won the Inter Repeater Bus arbitration and is transmitting valid data symbols. The DP83856 monitors this line at the beginning of the frame to establish whether the frame is a false carrier event. If TX_RDY is valid and IR_DV is invalid when the DP83856 samples the IR_DV line, then a false carrier event is counted.                                                                                                                                                                                                        |

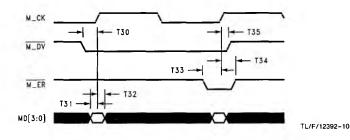

| MD[3:0]     |      |        | MANAGEMENT DATA [3:0]: Data which is sourced by any DP83850 in the system that has won the Inter Repeater Bus arbitration. This data is synchronous to the management clock M_CK, and is framed by the transmit ready signal TX_RDY. The DP83856 uses this data to determine the source of the current data stream (DP83850 RID number and Port number).                                                                                                                                                                                                                                                       |

| M_DV        | I    | Low    | <b>MANAGEMENT DATA VALID:</b> Asserted by any DP83850 in the system which has won the Inter Repeater Bus arbitration when it places valid data on MD[3:0]. The DP83856 monitors this line when TX_RDY is valid to determine when to latch the DP83850 RID number and port number for the current reception. $M_DV$ is synchronous to $M_CK$ .                                                                                                                                                                                                                                                                  |

| м_ск        | I    |        | MANAGEMENT CLOCK: All data transfers on the management bus are synchronized to the rising edge of this clock. M_CK is a reference 25 MHz clock used to latch the active DP83850, port, and elasticity buffer errors for the current packet reception. M_CK is sourced by any DP83850 in the system which has won the Inter Repeater Bus arbitration.                                                                                                                                                                                                                                                           |

| M_ER        | I    | Low    | MANAGEMENT ERROR: Asserted by any DP83850 in the system which has won the Inter<br>Repeater Bus arbitration when a data rate mismatch error occurs (elasticity buffer over/<br>underrun). The DP83856 monitors this line during TX_RDY valid to determine if the current<br>frame contains a data rate management error. M_ER is synchronous to M_CK. Note that on<br>data rate mismatch errors, M_ER will not be asserted until after the DP83850 number and port<br>number have been sent to the DP83856 from the DP83850, but will be sent prior to the end of<br>the frame (before TX_RDY is de-asserted). |

#### 2.4 MII INTERFACE

| Signal Name | Туре     | Active | Description                                                                                                                                                                                                                                                                                         |

|-------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

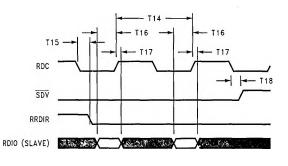

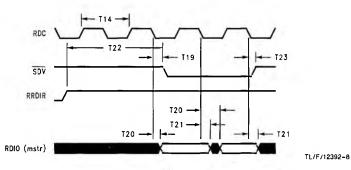

| RDC         | 0/Z, L   |        | <b>REGISTER DATA CLOCK:</b> A 2.5 MHz clock which is continuously output from the DP83856. Used to synchronize data transfers on the serial MII register bus.                                                                                                                                       |

| RDIO        | 1/0/Z, L |        | <b>REGISTER DATA I/O:</b> Serial MII register data signal. Used to transfer data to and from the DP83856 on MII register accesses. This signal should be buffered onto the backplane, using the RRDIR signal as a direction control for the buffer. The buffer does not require a tri-state enable. |

| RRDIR       | 0/Z, L   | High   | <b>RIB REGISTER DIRECTION:</b> Serial MII Register Direction pin to drive an external buffer. The buffer should default to READ, and toggle to WRITE only when the DP83856 is initiating an MII register access.         0 = MII Slave (DP83850 or PHY) drives RDIO         1 = DP83856 drives RDIO |

| SDV         | 0/Z, L   | Low    | SERIAL DATA VALID: Indicates that a valid MII access is in progress. It is asserted one half clock prior to the start of the cycle and remains valid for one half clock after the cycle is complete.                                                                                                |

# 2.0 Pin Description (Continued)

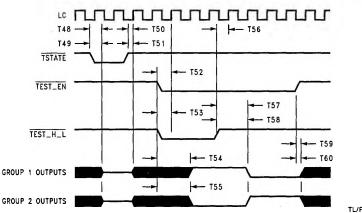

## 2.5 TEST INTERFACE

1/0/Z/P, L

|                                                                                                                                                     | _                                                |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                                                                                                                                         | Туре                                             | Active           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TSTATE                                                                                                                                              | I/P                                              | Low              | TRI-STATE®: Pulling this pin low puts the DP83856 into a test mode that tri-states all outputs<br>except NAND_E and NAND_O. This allows an external tester to drive all the outputs of the<br>DP83856.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TEST_EN                                                                                                                                             | I/P                                              | Low              | TEST MODE ENABLE HIGH/LOW OUTPUT TEST: Forces the DP83856's outputs to the High<br>or Low state as defined by the TEST_H_L pin. This allows automatic test machines to check<br>for outputs stuck at High or Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TEST_H_L                                                                                                                                            | 1/P                                              | Low              | TEST MODE OUTPUT HIGH/LOW: When TEST_EN is taken Low, the DP83856's output pins (in two groups) are forced into the High or Low state as defined below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                     |                                                  |                  | TEST_H_L Group 1 Outputs Group 2 Outputs<br>0 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                     |                                                  |                  | 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                     |                                                  |                  | <u>Group 1 output pin numbers are:</u> 21, 23, 27, 31, 35, 37, 39, 43, 61, 64, 68, 70, 72, 74, 78, 80, 82, 87, 89, 90, 92, 96, 98, 100, 104, 108, 113, 115.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                     | :                                                |                  | <u>Group 2 output pin numbers are:</u> 20, 22, 24, 30, 34, 36, 38, 42, 44, 65, 69, 71, 73, 75, 79, 81, 83, 88, 91, 93, 97, 99, 103, 105, 114, 116.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NAND_E                                                                                                                                              | 0, L                                             | Low              | NAND TREE EVEN INPUTS OUTPUT: The logical NAND of all of the even numbered inputs (except the test input TEST_EN) and RST. If all of the inputs are High, the output will go Low. If any of the inputs are Low, the output will remain High.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NAND_O                                                                                                                                              | 0, L                                             | Low              | NAND TREE ODD INPUTS OUTPUT: The logical NAND of all of the odd numbered inputs (except the test inputs TSTATE, TEST_H_L and LC). If all of the inputs are High, the output wil go Low. If any of the inputs are Low, the output will remain High.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                     |                                                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.6 MISCELL                                                                                                                                         | ANEOU                                            | SPINS            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.6 MISCELL<br>Signal Name                                                                                                                          | ANEOU<br>Type                                    | S PINS<br>Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                     |                                                  |                  | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off LC. This clock must be the same local clock used to drive the local DP83850 because the TX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>Signal Name</b><br>LC                                                                                                                            | Туре                                             |                  | <b>LOCAL CLOCK:</b> Primary clock for DP83856 device. All DP83856 internal state machines run off LC. This clock must be the same local clock used to drive the local DP83850 because the TX signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must be a 25.000 MHz, 40/60 duty cycle, 50 ppm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Signal Name<br>LC<br>RST                                                                                                                            | Гуре                                             | Active           | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br>RESET: The DP83856 is reset when this signal is asserted low. Asserting this signal will cause all<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not                                                                                                                                                                                                                                                                                                                                                       |

| Signal Name<br>LC<br>RST<br>RES1                                                                                                                    | Type<br>I                                        | Active           | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br>RESET: The DP83856 is reset when this signal is asserted low. Asserting this signal will cause all<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by RST, it must be cleared/preset by software.                                                                                                                                                                                                                                                                                             |

| Signal Name                                                                                                                                         | Туре<br> <br> <br> <br> <br> <br> <br> <br> <br> | Low              | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br><b>RESET:</b> The DP83856 is reset when this signal is asserted low. Asserting this signal will cause all<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by RST, it must be cleared/preset by software.<br><b>RESERVED OUTPUT 1:</b> No Connect.                                                                                                                                                                                                                                             |

| Signal Name<br>LC<br>RST<br>RES1<br>RES2                                                                                                            | Type<br>I<br>I<br>O<br>O<br>E DESIG              | Low              | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br><b>RESET:</b> The DP83856 is reset when this signal is asserted low. Asserting this signal will cause all<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by RST, it must be cleared/preset by software.<br><b>RESERVED OUTPUT 1:</b> No Connect.                                                                                                                                                                                                                                             |

| Signal Name<br>LC<br>RST<br>RES1<br>RES2<br>2.7 PIN TYPI                                                                                            | Type<br>I<br>I<br>O<br>O<br>E DESIG              | Low              | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br>RESET: The DP83856 is reset when this signal is asserted low. Asserting this signal will cause al<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by RST, it must be cleared/preset by software.<br>RESERVED OUTPUT 1: No Connect.<br>RESERVED OUTPUT 2: No Connect.                                                                                                                                                                                                                          |

| Signal Name<br>LC<br>RST<br>RES1<br>RES2<br>2.7 PIN TYPI<br>Typ                                                                                     | Type<br>I<br>I<br>O<br>O<br>E DESIG              | Low              | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br>RESET: The DP83856 is reset when this signal is asserted low. Asserting this signal will cause all<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by RST, it must be cleared/preset by software.<br>RESERVED OUTPUT 1: No Connect.<br>RESERVED OUTPUT 2: No Connect.<br>Description                                                                                                                                                                                                          |

| Signal Name<br>LC<br>RST<br>RES1<br>RES2<br>2.7 PIN TYPI<br>Typi<br>I                                                                               | Type<br>I<br>I<br>O<br>O<br>O<br>E DESIG         | Low              | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br>RESET: The DP83856 is reset when this signal is asserted low. Asserting this signal will cause al<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by RST, it must be cleared/preset by software.<br>RESERVED OUTPUT 1: No Connect.<br>RESERVED OUTPUT 2: No Connect.<br>Description<br>Input buffer.                                                                                                                                                                                          |

| Signal Name<br>LC<br>RST<br>RES1<br>RES2<br>2.7 PIN TYPI<br>Typi<br>I<br>I                                                                          | Type<br>I<br>I<br>O<br>O<br>E DESIG              | Low              | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br>RESET: The DP83856 is reset when this signal is asserted low. Asserting this signal will cause al<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by RST, it must be cleared/preset by software.<br>RESERVED OUTPUT 1: No Connect.<br>RESERVED OUTPUT 2: No Connect.<br>Description<br>Input buffer.<br>Input buffer with internal pull-up resistor.                                                                                                                                          |

| Signal Name<br>LC<br>RST<br>RES1<br>RES2<br>2.7 PIN TYPI<br>Typi<br>I<br>I/P<br>O, L                                                                | Type<br>I<br>I<br>O<br>E DESIG                   | Low              | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run off<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br><b>RESET:</b> The DP83856 is reset when this signal is asserted low. Asserting this signal will cause all<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by <b>RST</b> , it must be cleared/preset by software.<br><b>RESERVED OUTPUT 1:</b> No Connect.<br><b>RESERVED OUTPUT 2:</b> No Connect.<br><b>Description</b><br>Input buffer.<br>Input buffer with internal pull-up resistor.<br>Output buffer, low drive (4 mA).                                                                 |

| Signal Name           LC           RST           RES1           RES2           2.7 PIN TYPI           I           I/P           O, L           O/Z, | Type<br>I<br>I<br>O<br>E DESIG<br>B<br>L<br>L    | Low              | LOCAL CLOCK: Primary clock for DP83856 device. All DP83856 internal state machines run of<br>LC. This clock must be the same local clock used to drive the local DP83850 because the TX<br>signals (to which the DP83856 must be sychronized) are all synchronous to the local clock. Must<br>be a 25.000 MHz, 40/60 duty cycle, 50 ppm.<br><b>RESET:</b> The DP83856 is reset when this signal is asserted low. Asserting this signal will cause a<br>DP83856 state machines and registers to enter their reset state. The statistics SRAM is not<br>cleared by <b>RST</b> , it must be cleared/preset by software.<br><b>RESERVED OUTPUT 1:</b> No Connect.<br><b>RESERVED OUTPUT 2:</b> No Connect.<br><b>Description</b><br>Input buffer.<br>Input buffer with internal pull-up resistor.<br>Output buffer, low drive (4 mA).<br>Output buffer with high impedance capability, low drive (4 mA). |

Bi-directional buffer with high impedance capability and pull-up resistor, low drive (4 mA).

## **3.0 Functional Description**

The following sections describe the different functional blocks of the DP83856 100 Mb/s Repeater Information Base. Referring to the block diagram on page 2 of this data-sheet, the DP83856 is used in conjuction with a number of DP83850s, a management CPU and a fast (20 ns) 8k x 16 bit SRAM. The DP83856 collects and maintains network management statistics from the connected DP83850s and makes them available to the management CPU.

#### 3.1 STATISTICS GENERATION

Inputs to the DP83856 Statistic Generation block include the Inter Repeater Bus signals, Management Bus signals and TX bus signals. These signals provide the data streams necessary to create all the statistics collected by the DP83856. The DP83856 uses the fast external SRAM to hold statistics for the current packet reception. Statistics for the current receive packet are collected as follows:

#### 3.1.1 Octet Derived

The majority of the statistics are a function of the octet count. Statistics based on octet counts imply that a valid SFD has been detected and an accurate count of the number of data bytes in the packet are available.

The DP83856 Statistic Generation module has an SFD detect block, which indicates that a valid SFD has been detected so that the octet counter can be enabled. The Source Address latch is used to store the source address of the current packet, so that a comparison to the previous source address can be made at the end of the packet reception. Octet derived statistics include:

Frames Octets FCS Errors Alignment Errors Frames Too Long Source Address Source Address Changes

#### 3.1.2 Carrier Derived

Other statistics are a function of carrier. Carrier derived statistics have a high probability of occurring on activity bursts which do not include a valid SFD. To ensure accurate statistic gathering a carrier based detection scheme is implemented. A nibble counter is used to calculate the length of the carrier, which is used to create the carrier derived statistics.

The DP83856 employs 32-bit counters for network utilization, false carrier events, and collisions. All of these counters monitor events for all ports, i.e. they are an aggregate of the total repeater events.

Carrier derived statistics gathered by the DP83856 include:

Runts

Very Long Events (jabber)

Network Utilization

**Repeater False Carrier Events**

Repeater Collisions (per port collision map obtained from DP83850s)

#### 3.1.3 DP83850 Notified

For a few of the required statistics the DP83856 has no way of determining the occurrence of that event. These statistics are obtained by notification from the connected DP83850s. DP83850 notified statistics include:

Data Rate Mismatches Symbol Code Violations

#### 3.1.4 Collision Counter

The DP83856 has a 32-bit counter which is incremented any time the repeater experiences a collision. This counter is used to keep track of total number of collisions happening on the repeater.

#### 3.1.5 Network Utilization Counter

The Network Utilization counter is a 32-bit counter that counts nibbles when TX\_RDY is active. The network utilization counter will count all nibbles relative to any packet activity. This includes any short events, runts, and even noise on the segment. The network utilization counter is used to measure the packet activity relative to the overall network bandwidth. Since the nibbles occurs at a 25 MHz rate, during a one second update there could be up to a maximum of 25 million nibbles that could be recorded.

As an example, software can do a one second read update on the 32-bit network utilization counter, and read a 10 million value count. The network utilization can be calculated as 10 mil./25 mil. (max. total) = 0.4 or 40 per cent of the network bandwidth is utilized on that segment.

#### 3.1.6 False Carrier Counter

The DP83856 has a 32-bit counter which is incremented any time the repeater experiences a false carrier event. This counter is used to keep track of the total number of false carrier events occurring on the segment.

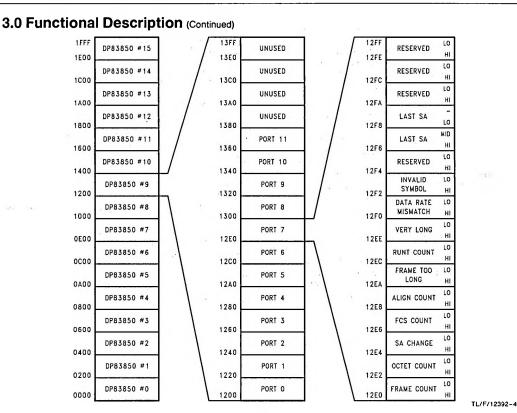

#### **3.2 SRAM INTERFACE**

The SRAM interface provides the logic required to communicate with the fast external SRAM.

The interface between the DP83856 and the fast external SRAM is very straightforward. The fast external SRAM is a dedicated block of memory directly accessed only by the DP83856. The DP83856 provides the address capability for 8k x 16 bits of SRAM. In this configuration the DP83856 can store up to sixteen 32-bit statistics per port.

Figure 1 shows a memory map for the 8k x 16 configuration. For each port there are 11 statistics defined which are stored in SRAM. Ten of these statistics are 32-bit values, and one is a 48-bit value (Last Source Address).

Last Source Address is stored as two 32-bit values for simplicity of hardware implementation. All statistics are stored in big endian mode.

The DP83856 can be directly connected to the SRAM; there is no need for buffering between the DP83856 and the SRAM. The DP83856 requires fast SRAM with a maximum access time of 20 ns.

The SRAM interface block contains the address and data multiplexers to select between CPU and Statistic Update accesses. Data is multiplexed under control of the SRAM arbiter.

#### 3.3 SRAM ARBITER

The SRAM arbiter controls the SRAM data multiplexers depending on what type of access is being performed and creates all of the control signals for the SRAM, ensuring the timing is correct. There are three events that result in SRAM arbitration:

- End of packet request\_Runt (Statistic Update State Machine)

- End of packet request\_Legal Length or greater (Statistic Update State Machine)

- CPU request (read or write)

The arbiter assigns highest priority to EOP-runts and lowest priority to CPU requests. For single statistic reads, the arbiter produces two 16-bit locked read cycles on the SRAM to form the 32-bit value. For block reads the SRAM arbiter rearbitrates after each 32-bit SRAM read (two 16-bit locked reads) to allow any higher priority event access to the SRAM. Writes to the SRAM must always be word (16-bit) accesses: byte writes are not supported.

#### 3.4 INTERRUPT GENERATION AND CONTROL

There are four events that can generate an interrupt:

- SRAM access complete

- MII register access complete

- Invalid MII register read

- DP83856 error

The DP83856 provides one interrupt line (CINT) that is shared for all interrupts. The interrupt is an active low, level sensitive signal. Interrupts are generated based on a valid event occuring with the appropriate mask bit set and global interrupt bit set. Interrupts are cleared by reading the interrupt register.

The "SRAM access complete" interrupt signifies that the current SRAM request has been serviced and the data is in the SRAM Read Data Register(s) (10h-40h).

The "MII register access complete" interrupt signifies that the current MII register request has been serviced and the data is in the MII Read Data Register(s) (A0h-ACh). The "Invalid MII register read" interrupt is generated based on the DP83856 detecting an error while performing an MII read access. Per the MII register protocol in IEEE 802.3u/ D5, Clause 22, the DP83856 looks for a leading 0 on reads; if it does not see a leading 0, it flags the read as invalid and generates the interrupt. DP83856

The "DP83856 error" interrupt signifies that the device has dropped management data due to invalid inter-frame gap (IFG) spacing between packets. The minimum IFG specified in the IEEE 802.3u/D5, Clause 21A.3 is 0.96  $\mu$ s. The DP83856 may drop management data if the IFG drops below 0.64  $\mu$ s. This event is not expected to happen on well formed 100 Mb/s networks.

#### **3.5 MII REGISTER INTERFACE**

The MII register interface block is a state machine that performs accesses to DP83850 and Physical Layer Device registers (read and write) based on requests from the CPU.

This interface uses the IEEE 802.3u clause 22 MII compliant serial interface protocol.

The MII Register Interface eliminates the need for the CPU to talk directly to the DP83850 and Physical Layer Device registers. The amount of spare management CPU processing bandwidth is therefore increased.

## 3.0 Functional Description (Continued)

The CPU provides the opcode, type of access (read or write), register address, and device ID to the MII Interface Register, and then asserts a start command by writing a 1 to bit 0 (MII\_ACC) of the Configuration Register.

MII protocol for performing reads and writes are as follows: READ

<01> <10> <AAAAA> <RRRRR> line turn-around> <0> <xxxx xxxx xxxx xxxx>

where <01> is a start bit sequence, <10> is a read opcode, <AAAAA> is the device address (up to 32 devices), <RRRR> is the register address (up to 32 registers), line turn-around> is a clock cycle allowed for turn-around of the data bus, <0> is a leading 0, and <xx ... xx> is 16 bits of data.

#### WRITE

<01><01><AAAAA><RRRRR> <10><xxxx xxxx xxxx xxxx>

where <01> is a start bit sequence, <01> is a write opcode, <AAAAA> is the device address (up to 32 devices), <RRRRP> is the register address (up to 32 registers), <10> is a leading 10, and <xx ... xx> is 16 bits of data. Refer to the IEEE 802.3u D5 draft document for more details on the MII interface, its function and timing.

#### 3.6 CPU REGISTER BLOCK

The CPU register block provides the system management CPU access to all of the data in the DP83856, SRAM, connected DP83850s and Physical Layer Devices.

#### **3.7 MANAGEMENT DATA INTERFACE**

For every network event, the DP83850 device with port N will send information required by the DP83856 to perform statistics gathering.

The information required by the DP83856 is transferred on the Management Data Interface, which consists of a nibble wide data bus with synchronous clock (MD[3:0] and  $M\_CK$ ), plus a framing signal ( $M\_DV$ ) and an error flag ( $M\_ER$ ).

Data is transferred in 3 nibbles (per network event). The first data nibble contains the lowest significant 4 bits of the DP83850 RID Number, the second contains the most significant bit of the DP83850 RID number and the third contains the number of the receiving port (port N). The  $M\_ER$  signal indicates elasticity buffer errors (due to under-run or over-run) in the DP83850.

## 4.0 Registers

All the DP83856 registers are directly addressable by the system management CPU. Although some bits in the Configuration Register have been allocated to a register paging scheme, these are not currently used (available for future expansion) and should always be set to zero.

All register accesses are word (16-bit) wide: byte access is not supported. The addresses given in the tables below assume that the user has connected the DP83856 to a man-

#### 4.1 REGISTER MEMORY MAP

agement CPU in the normal 16-bit manner with address bits A1-A7 from the CPU connected to bits CA1-CA7 on the DP83856. The addresses are thus the offset from the base address at which the DP83856 is located in the system.

To be consistent with normal address bus labeling practice, since the DP83956 only supports 16-bit accesses, no pin A0 is supplied.

| Address | Register                              | Access |

|---------|---------------------------------------|--------|

| 00h     | Configuration Register                | R/W    |

| 02h     | Interrupt                             | R/W    |

| 04h     | Reserved                              |        |

| 06h     | SRAM Interface                        | R/W    |

| 08h     | MII Management Interface              | R/W    |

| 0Ah     | SRAM Write Data                       | R/W    |

| 0Ch     | MII Write Data                        | R/W    |

| 0Eh     | Device ID                             | R only |

| 10h     | Frame Count High Read                 | R/W    |

| 12h     | Frame Count Low Read                  | R/W    |

| 14h     | Octet Count High Read                 | R/W    |

| 16h     | Octet Count Low Read                  | R/W    |

| 18h     | Source Address Change Count High Read | R/W    |

| 1Ah     | Source Address Change Count Low Read  | R/W    |

| 1Ch     | FCS Error Count High Read             | R/W    |

| 1Eh     | FCS Error Count Low Read              | R/W    |

| 20h     | Alignment Error Count High Read       | R/W    |

| 22h     | Alignment Error Count Low Read        | R/W    |

| 24h     | Frame Too Long Count High Read        | R/W    |

| 26h     | Frame Too Long Count Low Read         | R/W    |

| 28h     | Runt Count High Read                  | R/W    |

| 2Ah     | Runt Count Low Read                   | R/W    |

| 2Ch     | Very Long Event Count High Read       | R/W    |

| 2Eh     | Very Long Event Count Low Read        | R/W    |

| 30h     | Data Rate Mismatch Count High Read    | R/W    |

| 32h     | Data Rate Mismatch Count Low Read     | R/W    |

| 34h     | Invalid Symbol Count High Read        |        |

| 36h     | Invalid Symbol Count Low Read         | R/W    |

| 38h     | Reserved                              |        |

| 3Ah     | Reserved                              |        |

| 3Ch     | Source Address High Read              | * R/W  |

| 3Eh     | Source Address Mid Read               | R/W    |

| 40h     | Source Address Low Read               | R/W    |

| 42h     | Reserved                              |        |

| 44h-7Eh | Reserved                              |        |

## 4.1 REGISTER MEMORY MAP (Continued)

| Address  | Register                                                   | Access |

|----------|------------------------------------------------------------|--------|

| 80h      | Carrier Count Register                                     | R/W    |

| 82h      | Oct_Nib Count Register                                     | R/W    |

| 84h-8Eh  | Reserved                                                   |        |

| 90h      | Repeater Collisions High Read                              | R/W    |

| 92h      | Repeater Collisions Low Read                               | R/W    |

| 94h      | Network Utilization High Read                              | R/W    |

| 96h      | Network Utilization Low Read                               | R/W    |

| 98h      | False Carrier High Read                                    | R/W    |

| 9Ah      | False Carrier Low Read                                     | R/W    |

| 9Ch-9Eh  | Reserved                                                   |        |

| A0h      | Mil Read Data / Port 0-11 Short Event High Block Read Data | R only |

| A2h      | DP83850 Port 0-11 Short Event Low Block Read Data          | Ronly  |

| A4h      | DP83850 Port 0-11 Late Event High Block Read Data          | R only |

| A6h      | DP83850 Port 0-11 Late Event Low Block Read Data           | R only |

| A8h      | DP83850 Port 0-11 Collision High Block Read Data           | R only |

| AAh      | DP83850 Port 0-11 Collision Low Block Read Data            | R only |

| ACh      | DP83850 Port 0-11 Auto-Partitions Block Read Data          | R only |

| AEh      | Reserved                                                   |        |

| B0h-1FEh | Reserved                                                   |        |

## 4.2 CONFIGURATION REGISTER

### Address: 00h

Reset: All bits cleared to zero.

| Bit     | Bit Name    | Access | Description                                                                                                                                                            |

|---------|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0      | MII_ACC     | R/W    | 0: DP83856 writes 0 after register access completes<br>1: CPU initiates register access by writing 1                                                                   |

|         |             |        | This bit indicates when the current DP83850 or Physical Layer device register access is<br>complete.                                                                   |

| D1      | SR_ACC      | R/W    | 0: DP83856 writes 0 after SRAM access completes<br>1: CPU initiates SRAM access by writing 1                                                                           |

|         | 8           |        | This bit indicates when the current SRAM access is complete.                                                                                                           |

| D2      | SR_ACC_TYPE | R/W    | 0: Perform Single Access<br>1: Perform Block Access (Reads Only) All SRAM based statistics will be loaded into<br>SRAM (CPU Addr. 10h-40h)                             |

| D3      | MEN         | R/W    | 0: Statistics gathering disabled<br>1: Statistics gathering enabled                                                                                                    |

|         |             |        | This bit enables managment statistics gathering. Note that subsequent read accesses should use read-modify-write instructions so that the MEN bit is left undisturbed. |

| D(4:7)  | PAGE_SEL    | R/W    | These bits define which page of the register map the CPU is pointing to. Allows for 16 pages x 256 word registers.                                                     |

|         |             | -      | Always write 0 for compatibility with later versions of DP83856.                                                                                                       |

|         | 8           |        | Note: The Page bits are not implemented in current version.                                                                                                            |

| D(8:15) | Reserved    | R/W    | Write: 0<br>Read: Undefined                                                                                                                                            |

4.3 INTERRUPT REGISTER

Address: 02h

.

Reset: All bits cleared to zero.

Note: Mask bits must be set to enable valid status on corresponding status bits.

| Bit     | Bit Name       | Access | Description                                                                                                                                                                        |

|---------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0      | MII_INT_STS    | R      | 0: MII access complete Interrupt not asserted.<br>1: MII access complete Interrupt asserted.<br>Cleared by read of register. Writes ignored.                                       |

| D1      | SR_ACC_STS     | R      | 0: SRAM access complete Interrupt not asserted.<br>1: SRAM access complete Interrupt asserted.<br>Cleared by read of register. Writes ignored.                                     |

| D2      | RIBERR_STS     | R      | 0: DP83856 error Interrupt not asserted.<br>0: Mil access complete Interrupt not asserted.<br>1: DP83856 error Interrupt asserted.<br>Cleared by read of register. Writes ignored. |

| D3      | MII_RD_ERR_STS | R      | 0: MII register read error Interrupt not asserted.<br>1: MII register read error Interrupt asserted.<br>Cleared by read of register. Writes ignored.                               |

| D4      | MII_INT_MSK    | R/W    | 0: Mask MII access complete Interrupt.<br>1: Enable MII access complete Interrupt.                                                                                                 |

| D5      | SR_ACC_MSK     | R/W    | 0: Mask SRAM access complete Interrupt.<br>1: Enable SRAM access complete Interrupt.                                                                                               |

| D6      | RIBERRMSK      | R/W    | 0: Mask DP83856 error Interrupt.<br>1: Enable DP83856 error Interrupt.                                                                                                             |

| D7      | MII_RD_ERR_MSK | R/W    | 0: Mask MII Register Error Interrupt.<br>1: Enable MII Register Error Interrupt.                                                                                                   |

| D8      | INT_EN         | R/W    | 0: Disable CINT signal.<br>1: Enable CINT signal.<br>This bit is a global enable for the CINTsignal. It has NO effect on the status bits.                                          |

| D(9:15) | Reserved       | R/W    | Write: 0<br>Read: Undefined.                                                                                                                                                       |

4.4 SRAM INTERFACE REGISTER

Address: 06h

D(13:15)

Reset: All bits cleared to zero.

| Bit      | Bit Name     | Access  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D(0:4)   | STAT_ACC#    | R/W     | These bits set which STATISTIC the SRAM access is destined for. Values are:<br>00h: Frame Count<br>02h: Octet Count<br>04h: SA Change Count<br>06h: FCS Error Count<br>08h: Alignment Error Count<br>0Ah: Frame Too Long Count<br>0Ch: Runt Count<br>0Ch: Very Long Event Count<br>10h: Data Rate Mismatch Count<br>12h: Invalid Symbol Count<br>14h: Reserved<br>16h: Source Address High<br>18h: Source Address Low<br>1Ah-1Eh: Reserved |

| D(5:6)   | Reserved     | R/W     | Always Write 0                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D7       | R/W_SRAM     | R/W     | 0: SRAM Write<br>1: SRAM Read<br>This bit defines whether the current CPU SRAM access is a read or a write.                                                                                                                                                                                                                                                                                                                                |

| D(8:11)  | PORT_ACC#    | R/W     | These bits set which PORT number the access is destined for.<br>Valid values are 0h–Bh (12 ports)                                                                                                                                                                                                                                                                                                                                          |

| D(12:15) | RICACC#      | R/W     | These bits set which DP83850 the access Is destined for.<br>Valid values are 0h-Fh (16, DP83850s)                                                                                                                                                                                                                                                                                                                                          |

|          | ANAGEMENT IN | TERFACE | hile an SRAM access is in progress (If bit D1 of Configuration Register is 1, then do not access this register).                                                                                                                                                                                                                                                                                                                           |

| Bit      | Bit Name     | Access  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D(0:4)   | REG_ADDR     | R/W     | These bits set which register the access is destined for.                                                                                                                                                                                                                                                                                                                                                                                  |

| D(5:9)   | DEV_ID       | R/W     | These bits set which DEVICE_ID the access is destined for.                                                                                                                                                                                                                                                                                                                                                                                 |

| D(10:11) | OPCODE       | R/W     | OPCODE VALUE: Corresponds to the opcodes defined in the MII specification.<br>01: Extended Addressed Mode Write, 16-bit payload.<br>10: Extended Addressed Mode Read, 16-bit payload.                                                                                                                                                                                                                                                      |

| D12      | MII_ACC_TYP  | R/W     | MII ACCESS TYPE: Sets the access type to single or block read.<br>0: Perform Single Access (All Physical Layer device accesses and all DP83850 accesses<br>except DP83850 counters).                                                                                                                                                                                                                                                       |

1: Perform Block Read (DP83850 reads only). All DP83850 based counters will be loaded into registers (Address A0h-ACh). The OPCODE field is 10 for block reads. REG\_ADDR is set to register address corresponding to the Port\_ShortEvent Counter for the desired port.

Reserved

R/W

Read: Undefined.

## 4.6 SRAM WRITE DATA REGISTER

Address: 0Ah

Reset: All bits cleared to zero.

| Bit     | Bit Name                    | Access | Description                                                                                                                                   |  |  |

|---------|-----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D(0:15) | WR_DATA                     | R/W    | This register contains the data to be written on an SRAM write access. SRAM writes should<br>only be performed during DP83856 initialization. |  |  |

| 4.7 MII | 4.7 MII WRITE DATA REGISTER |        |                                                                                                                                               |  |  |

Address: 0Ch

Reset: All bits cleared to zero.

| Bit     | Bit Name | Access | Description                                                                    | 1 |  |

|---------|----------|--------|--------------------------------------------------------------------------------|---|--|

| D(0:15) | WR_DATA  | R/W    | This register contains the data to be written on an MII register write access. |   |  |

## 4.8 DEVICE ID REGISTER

Address: 0Eh

Reset: All bits cleared to zero.

| Bit     | Bit Name  | Access | Description                                                                                                               |

|---------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------|

| D(0:3)  | REV_LEVEL | R      | These bits are the Revision level of the device and are embedded into the DP83856 silicon. Reads 0h for initial revision. |

| D(4:7)  | DEVICE ID | R      | These bits are a vendor specific code embedded in the DP83856. Reads 0h for initial revision.                             |

| D(8:15) | Reserved  | R/W    | Write: 0<br>Read: Undefined.                                                                                              |

## 4.9 SRAM READ DATA REGISTERS

Addresses: 10h-40h

Reset: All bits cleared to zero.

| Bit     | Bit Name       | Access | Description                                                | <br> |

|---------|----------------|--------|------------------------------------------------------------|------|

| D(0:15) | SRAM Read Data | R      | Contains data corresponding to the SRAM location selected. | -8   |

## 4.10 CARRIER COUNT REGISTER

Address: 80h

Reset: All bits cleared to zero.

| Bit      | Bit Name      | Access           | Description                                                                                                                                                          |

|----------|---------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D(0:13)  | Carrier Count | <sup>-</sup> R/W | Contains data which is used to preset the carrier counter FOR TEST PURPOSES ONLY.<br>This register can only be written when the MEN bit in the CONFIG register is 0. |

| D(14:15) | Unused        | R/W              | Write: 0<br>Read: Undefined.                                                                                                                                         |

### 4.11 OCT\_NIB COUNT REGISTER

Address: 82h

Reset: All bits cleared to zero.

| Bit      | Bit Name      | Access | Description                                                                                                                                                            |

|----------|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D(0:11)  | Oct_Nib Count | R/W    | Contains data which is used to preset the Octet-Nibble counter FOR TEST PURPOSES ONLY. This register can only be written when the MEN bit in the CONFIG register is 0. |

| D(12:15) | Unused        | R/W    | Write: 0<br>Read: Undefined.                                                                                                                                           |

## 4.12 NETWORK COUNTERS

Addresses: 90h-9Ah

Reset: All bits cleared to zero.

| Bit Bit Name Access Description |  | Description                                                                                                                                                                     |

|---------------------------------|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|