# DP802514-1 TROPIC REEF + ™, DP802515-1 TROPIC PELÉ + ™, TROPIC™ Microcode ROM

### **General Description**

The DP802514-1 and DP802515-1 are the microcode ROMs for the TROPIC token ring network controllers. The DP802514-1 is a TROPIC REEF+ device and the DP802515-1 is a TROPIC PELE+ device. The devices feature an interface that is compatible to DP8025 interface controller to allow direct interfacing without the use of glue logic.

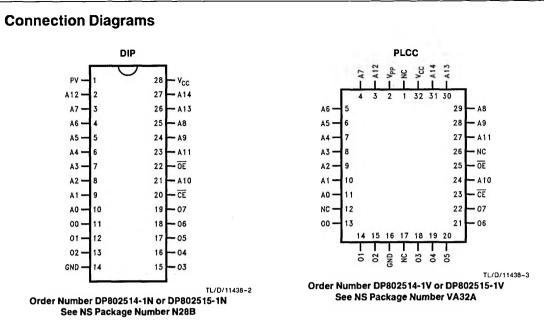

The DP802514-1 and DP802515-1 are implemented in National's double poly, single metal CMOS process. They operate from a single 5V  $\pm$  10% power supply. They are available in 28-pin, DIP or 32-pin PLCC.

#### Features

- TROPIC compatible

- Glueless interface

- High reliability CMOS processing

ESD protection exceeds 2000V

Latch up immunity to 200 mA

- Surface mount and DIP package

- Surface mount and Dir packa

28-pin molded plastic DIP

32-pin PLCC

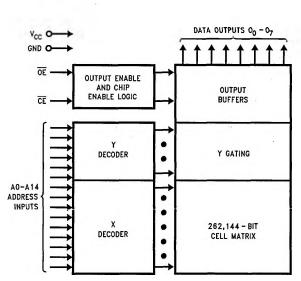

# **Block Diagram**

TL/D/11438-1

DP802514-1, DP802515-1

#### Commercial Temperature Range (0°C to +70°C) V<sub>CC</sub> = 5V $\pm$ 10%

| Order<br>Number | Microcode<br>Section | Check<br>Sum<br>7940 |  |

|-----------------|----------------------|----------------------|--|

| DP802514-1N, V  | Even/Lower           |                      |  |

| DP802515-1N, V  | Odd/Upper            | D739                 |  |

#### Pin Names

| Symbol                         | Description                |

|--------------------------------|----------------------------|

| A0-A14                         | Addresses                  |

| CE                             | Chip Enable                |

| ÕE                             | Output Enable              |

| O <sub>0</sub> -O <sub>7</sub> | Outputs                    |

| PV*                            | Connect to V <sub>CC</sub> |

\*This function is used during test/manufacture. Should be connected to V<sub>CC</sub> in application.

4-61

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Storage Temperature                                      | -65°C to +150°C |

|----------------------------------------------------------|-----------------|

| All Input Voltages<br>with Respect to Ground             | -0.6V to +7V    |

| V <sub>CC</sub> Supply Voltage<br>with Respect to Ground | -0.6V to $+7V$  |

ESD Protection

All Output Voltages with Respect to Ground

$V_{CC}$  + 1.0V to GND - 0.6V

>2000V

# **Operating Range**

| Range      | Temperature    | V <sub>CC</sub> |

|------------|----------------|-----------------|

| Commercial | 0°C to +60°C   | 5V ±10%         |

| Industrial | -40°C to +85°C | 5V ±10%         |

### **Read Operation**

#### DC Electrical Characteristics Over Operating Range

| Symbol             | Parameter                              | Test Condtions                                                     | Min                   | Max                 | Units |

|--------------------|----------------------------------------|--------------------------------------------------------------------|-----------------------|---------------------|-------|

| VIL                | Input Low Level                        |                                                                    | -0.5                  | 0.8                 | v     |

| VIH                | Input High Level                       |                                                                    | 2.0                   | V <sub>CC</sub> + 1 | V     |

| V <sub>OL</sub>    | Output Low Voltage                     | I <sub>OL</sub> = 2.1 mA                                           |                       | 0.4                 | V     |

| V <sub>OH</sub>    | Output High Voltage                    | $I_{OH} = -400 \ \mu A$                                            | 3.5                   |                     | V     |

| ICCSB1             | V <sub>CC</sub> Standby Current (CMOS) | $CE = V_{CC} \pm 0.3V$                                             | 1.030                 | 100                 | μΑ    |

| I <sub>CCSB2</sub> | V <sub>CC</sub> Standby Current        | CE = V <sub>IH</sub>                                               | - 640                 | 1                   | mA    |

| Icc                | V <sub>CC</sub> Standby Active Current | $\overline{CE} = \overline{OE} = V_{IL}$ , f = 5 MHz<br>I/O = 0 mA |                       | 35                  | mA    |

| Ірр                | VPP Supply Current                     | $V_{PP} = V_{CC}$                                                  |                       | 10                  | μA    |

| V <sub>PP</sub>    | VPP Read Voltage                       |                                                                    | V <sub>CC</sub> - 0.7 | V <sub>CC</sub>     | V     |

| l <sub>u</sub>     | Input Load Current                     | $V_{IN} = 5.5V \text{ or } GND$                                    | -1                    | 1                   | μΑ    |

| ILO -              | Output Leakage Current                 | V <sub>OUT</sub> = 5.5V or GND                                     | -10                   | 10                  | μΑ    |

# AC Electrical Characteristics Over Operating Range

| Symbol                      | Parameter                                                         | Min | Max |

|-----------------------------|-------------------------------------------------------------------|-----|-----|

| tACC                        | Address to Output Delay                                           |     | 95  |

| TOE                         | CE to Output Delay                                                |     | 95  |

| toe                         | OE to Output Delay                                                |     | 40  |

| t <sub>DF</sub><br>(Note 2) | Output Disable to Output Float                                    |     | 25  |

| <sup>t</sup> OH<br>(Note 2) | Output Hold from Addresses,<br>CE or OE, whichever occurred First |     |     |

#### Capacitance $T_A = +25^{\circ}C$ , 1 = 1 MHz (Note 2)

| Symbol          | Parameter          | Conditions            | Тур | Max | Units |

|-----------------|--------------------|-----------------------|-----|-----|-------|

| C <sub>IN</sub> | Input Capacitance  | $V_{IN} = 0V$         | 6   | 12  | pF    |

| COUT            | Output Capacitance | V <sub>OUT</sub> = 0V | 9   | 12  | pF    |

# **AC Test Conditions**

| Output Load        | 1 TTL Gate and $C_L = 100  pF$ | Input Pulse Level        | 0.45V to 2.4V |

|--------------------|--------------------------------|--------------------------|---------------|

|                    | (Note ≤ 5 ns)                  | Timing Measurement Level | (Note 8)      |

| Input Pulse Levels | 0.45V to 2.4V                  | Inputs                   | 0.8V to 2V    |

|                    |                                | Outputs                  | 0.8V to 2V    |

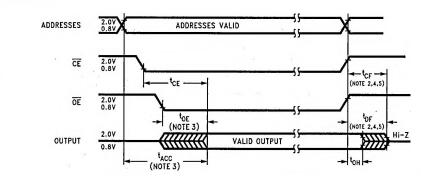

#### AC Waveforms (Notes 6, 7 and 9)

TL/D/11438-4

Note 1: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operations sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: This parameter is only sampled and is not 100% tested.

Note 3:  $\overline{OE}$  may be delayed up to  $t_{ACC} - t_{\overline{CE}}$  after the falling edge of  $\overline{CE}$  without impacting  $t_{ACC}$ .

Note 4: The top and top compare level is determined as follows:

High to TRI-STATE®, the measure VCH1 (DC) - 0.10V;

Low to TRI-STATE, the measured V<sub>OL1</sub> (DC) + 0.10V.

Note 5: TRI-STATE may be attained using OE or CE.

Note 6: The power switching characteristics require careful device decoupling. It is recommended that at least a 0.2 µF ceramic capacitor be used on every device between V<sub>CC</sub> and GND.

Note 7: The outputs must be restricted to  $V_{CC}$  + 1.0V to avoid latch-up and device damage.

Note 8: 1 TTL Gate:  $I_{OL}$  = 1.6 mA,  $I_{OH}$  = -400  $\mu$ A, CL: 100 pF includes fixture capacitance.

# **Functional Description**

#### DEVICE OPERATION

The three modes of operation of the DP802514-1 and DP802515-1 are listed in Table I. It should be noted that all inputs for the three modes are at TTL levels. The power supply required is  $V_{CC}$ .

#### READ MODE

THE DP802514-1 and DP802515-1 have two control functions, both of which must be logically active in order to obtain data at the outputs. Chip Enable ( $\overline{\text{CE}}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{\text{OE}}$ ) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time ( $t_{ACC}$ ) is equal to the delay from  $\overline{\text{CE}}$  to output ( $t_{\overline{\text{CE}}}$ ). Data is available at the outputs  $t_{\overline{\text{OE}}}$  after the falling edge of  $\overline{\text{OE}}$ , assuming that  $\overline{\text{CE}}$  has been low and addresses have been stable for at least  $t_{ACC} - t_{\overline{\text{OE}}}$ .

#### STANDBY MODE

The DP802514-1 and DP802515-1 have a standby mode which reduces the active power dissipation by over 99%, from 75 mW to 0.55 mW. They are placed in the standby mode by applying a CMOS high signal to the  $\overline{CE}$  input. When in standby mode, the outputs are in a high impedance state, independent of the  $\overline{OE}$  input.

#### OUTPUT DISABLE

The DP802514-1 and DP802515-1 are placed in output disable by applying a TTL high signal to the OE input. When in output disable all circuitry is enabled, except the outputs are in a high impedance state (TRI-STATE).

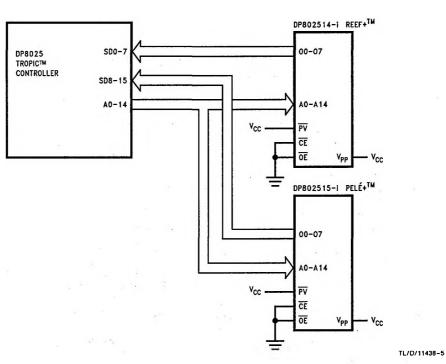

#### APPLICATION

In application, the DP802514-1 and DP802515-1 should be connected to the DP8025 TROPIC controller as shown in *Figure 1*. The DP802514-1 is the lower microcode ROM, and O<sub>0</sub> thru O<sub>7</sub> are to be connected to SD<sub>0</sub> thru SD<sub>7</sub>. The DP802515-1 is the upper microcode ROM and O<sub>0</sub> thru O<sub>7</sub> are to be connected to SD<sub>6</sub> thru SD<sub>15</sub> of the DP8025.

#### SYSTEM CONSIDERATION

The power switching characteristics of DP802514-1 and DP802515-1 require careful decoupling of the devices. The supply current, ICC, has three segments that are of interest to the system designer: the standby current level, the active current level, and the transient current peaks that are produced by voltage transitions on input pins. The magnitude of these transient current peaks is dependent of the output capacitance loading of the device. The associated V<sub>CC</sub> transient voltage peaks can be suppressed by properly selected decoupling capacitors. It is recommended that at least a 0.2 µF ceramic capacitor be used on every device between V<sub>CC</sub> and GND for each eight devices. The bulk capacitor should be located near where the power supply is connected to the subsystem. The purpose of the bulk capacitor is to overcome the voltage drop caused by the inductive effects of the PC board traces.

#### **Mode Selection**

The modes of operation of the DP802514-1 and DP802515-1 are listed in Table I. A single 5V power supply is required. All inputs are TTL levels except for  $PV = V_{CC}$ .

# DP802514-1, DP802515-1

# Mode Selection (Continued)

| TABLE I. Modes Selection |                 |     |                 |                 |                  |

|--------------------------|-----------------|-----|-----------------|-----------------|------------------|

| Pins<br>Mode             | CE/PGM          | ŌĒ  | PV              | V <sub>CC</sub> | Outputs          |

| Read                     | VIL             | VIL | V <sub>CC</sub> | 5.0V            | D <sub>OUT</sub> |

| Output Disable           | X (Note 1)      | VIH | V <sub>CC</sub> | 5.0V            | High Z           |

| Standby                  | V <sub>IH</sub> | x   | V <sub>CC</sub> | 5.0V            | High Z           |

Note 1: X can be  $V_{IL} \text{ or } V_{IH}.$

FIGURE 1. Typical TROPIC Connection