# INational Semiconductor

# DP802513 **TROPIC<sup>™</sup> MEMCS\_\_16 Signal Decoder**

### **General Description**

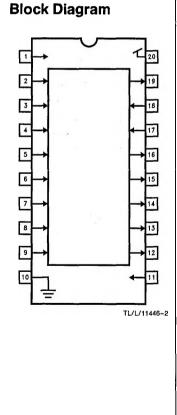

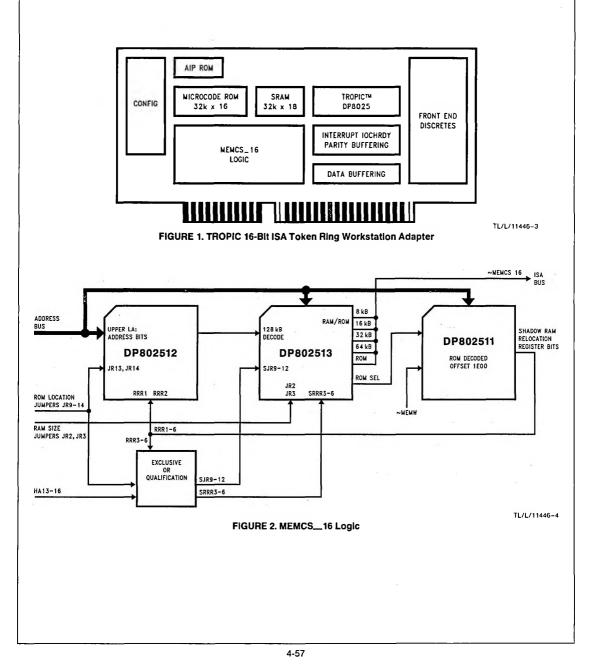

The DP802511, DP802512 and DP802513 form the majority of the MEMCS\_16 circuitry that is responsible for notifying the ISA bus (by way of MEMCS\_16) that it can execute 16-bit bus transfers with the DP8025 TROPIC.

The areas of the architecture that will benefit most from the increased performance of 16-bit transfers are the shared memory interface and the host boot ROM (if so designed). For the boot ROM it is a relatively simple matter of matching the jumpered configuration bits SD9-SD15 (BIOS/MMIO base address) with the system address (SA) lines. The MEMCS\_16 signal's maximum propagation delay from the SA lines is about 25 ns (assuming 8 MHz IBM® PC-AT®).

The shared memory interface RAM size is determined by jumper bits SD2 and SD3. These indicate the block size decoded to the shared memory MEMCS\_\_16 circuitry. The

address of this shared memory interface is software selectable. In order for the hardware to respond to the proper memory address it must shadow the RAM Relocation Register of the TROPIC's memory mapped I/O space. The data programmed into the RAM Relocation Register is latched into this shadowing register and used in conjuction with the system address lines to determine which address range contains the shared memory interface.

#### Features

- High speed: t<sub>PD</sub> = 7.0 ns (max)

- Single chip custom logic solution

- Replaces glue logic

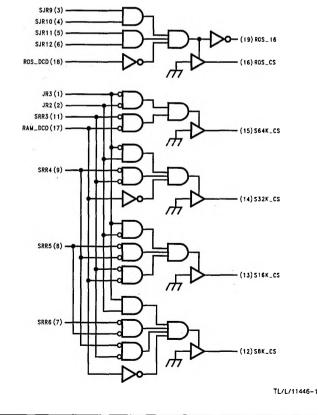

## Logic Diagram

### **Functional Description**

The DP802513 TROPIC MEMCS\_16 Signal Decoder is manufactured using National's high speed ASPECT II bipolar TTL process and provides further decode of a 128k block decode for generation of the MEMCS\_16 signal on the ISA bus. The ROS\_CS (Read Only Storage) signal is a decode of an 8k boundary that is wire-ORed externally with the four RAM decode outputs. The ROS\_16 signal is an identical decode as for ROS\_CS above, except that it is not wire-ORed to the MEMCS\_16 signal. Its purpose is to

notify the RAM relocation register strobe circuitry (DP802511) that the required address (1E00) is in the ROM address area.

Depending upon the position of the jumpers JR02 and JR03, for user selectable shared RAM size, the device provides a decode of either 8k, 16k, 32k or 64k for MEMCS\_\_\_\_\_\_ 16 generation. These signals are all output enabled and wire-ORed.

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> ) | -0.5V to +7.0V                   |

|-----------------------------------|----------------------------------|

| Input Voltage                     | - 1.5V to V <sub>CC</sub> + 7.0V |

| Off-State Output Voltage          |                                  |

| (V <sub>O</sub> ) (Note 2)        | -1.5V to V <sub>CC</sub> + 5.5V  |

- 10.0 mA to + 5.0 mA Input Current Output Current (IOL) -65°C to +150°C Storage Temperature Ambient Temperature with -65°C to +125°C Power Applied Junction Temperature -65°C to +150°C

100 mA

## **Recommended Operating Conditions**

#### SUPPLY VOLTAGE AND TEMPERATURE

| Symbol          | Parameter                      |      | Units |      |       |

|-----------------|--------------------------------|------|-------|------|-------|

| Symbol          |                                | Min  | Nom   | Max  | onits |

| V <sub>CC</sub> | Supply Voltage                 | 4.75 | 5     | 5.25 | v     |

| T <sub>A</sub>  | Operating Free-Air Temperature | 0    | 25    | 75   | °C    |

### Electrical Characteristics Over Recommended Operating Conditions

| Symbol          | Parameter                             | Conditions                                     | Min   | Тур | Max   | Units |

|-----------------|---------------------------------------|------------------------------------------------|-------|-----|-------|-------|

| V <sub>IL</sub> | Low Level Input Voltage (Note 3)      |                                                |       |     | 0.8   | v     |

| VIH             | High Level Input Voltage (Note 3)     |                                                | 2     |     |       | v     |

| VIC             | Input Clamp Voltage                   | $V_{CC} = Min, I = -18 mA$                     |       |     | -1.2  | v     |

| łL              | Low Level Input Current               | $V_{CC} = Max, V_I = 0.4V$                     |       |     | -250  | μA    |

| ĮН              | High Level Input Current              | $V_{CC} = Max, V_I = 2.4V$                     |       |     | 25    | μA    |

| t <sub>l</sub>  | Maximum Input Current                 | $V_{CC} = Max, V_I = 5.5V$                     |       |     | 100   | μA    |

| VOL             | Low Level Output Voltage              | $V_{CC} = Min, I_{OL} = 24 \text{ mA}$         |       |     | 0.5   | v     |

| V <sub>OH</sub> | High Level Output Voltage             | $V_{CC} = Min, I_{OL} = -3.2 \text{ mA}$       | 2.7   |     |       | ٠v    |

| lozL            | Low Level Off State Output Current    | $V_{CC} = Max, V_O = 0.4V$                     | 1     |     | -50   | μA    |

| IOZH            | High Level Off State Output Current   | $V_{CC} = Max, V_O = 2.4V$                     | - 0.0 |     | 50    | μА    |

| los             | Output Short Circuit Current (Note 4) | $V_{\rm CC} = 5V, V_{\rm O} = 0V$              | -50   |     | - 130 | mA    |

| Icc             | Supply Current                        | V <sub>CC</sub> = Max, Output Open             |       | 125 | 180   | mA    |

| CI              | Input Capacitance                     | $V_{\rm CC} = 5.0 V_{\rm I} V_{\rm I} = 2.0 V$ |       | 8   |       | pF    |

| Co              | Output Capacitance                    | $V_{\rm CC} = 5.0V, V_{\rm O} = 2.0V$          |       | 8   |       | pF    |

Note 1: Absolute maximum ratings are those values beyond which the device may be permanently damaged. Proper operation is not guaranteed outside the specified recommended operating conditions.

Note 2: V<sub>O</sub> must not exceed V<sub>CC</sub> + 1V.

Note 3: These are absolute voltages with respect to the ground pin on the device and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

Note 4: To avoid invalid readings in other parameter tests it is preferable to conduct the IOS test last. To minimize internal heating, only one output should be shorted at a time with a maximum duration of 1.0 second each. Prolonged shorting of a High output may raise the chip temperature above normal and permanent damage may result.

| Switching Characteristics Over Recommended Operating Conditions |                                               |                                                                              |            |     |     |       |  |

|-----------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------|------------|-----|-----|-------|--|

| 0                                                               |                                               | Conditions                                                                   | Commercial |     |     | Units |  |

| Symbol                                                          | Parameter                                     |                                                                              | Min        | Тур | Max | Onits |  |

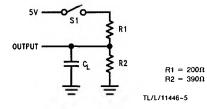

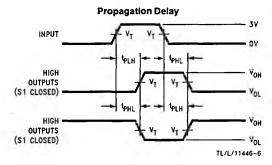

| t <sub>PD</sub>                                                 | Input to Output                               | C <sub>L</sub> = 50 pF, S1 Closed                                            |            |     | 7.0 | ns    |  |

| <sup>t</sup> PZXI                                               | Input to Output Enabled via<br>Control Logic  | C <sub>L</sub> = 50 pF, Active High: S1 Open<br>Active Low: S1 Closed        | 3.0        |     | 7.0 | ns    |  |

| t <sub>PXZI</sub>                                               | Input to Output Disabled via<br>Control Logic | $C_L = 5 \text{ pF}$ , From $V_{OH}$ : S1 Open,<br>From $V_{OL}$ : S1 Closed | 3.0        |     | 7.0 | ns    |  |

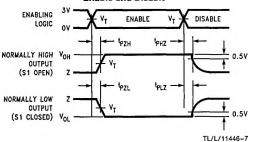

## Test Load

## **Test Waveforms**

DP802513