| Subject:                | Additional Information                             |

|-------------------------|----------------------------------------------------|

| Data Sheet Concerned:   | DMA 2271, DMA 2280, DMA 2281<br>6251-331-1E, 08/91 |

| Supplement / Order No.: | No. 2 / 6251-384-2DSS                              |

| Edition:                | Nov. 9, 1995                                       |

#### The DMA 2381 can replace the DMA 2281.

Software changes are only needed to achieve improved functionality.

Hardware changes are only needed to optimize improved functionality.

#### Changes between the DMA 2281 and the DMA 2381:

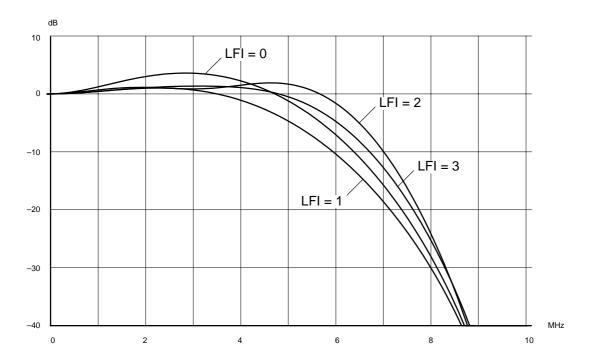

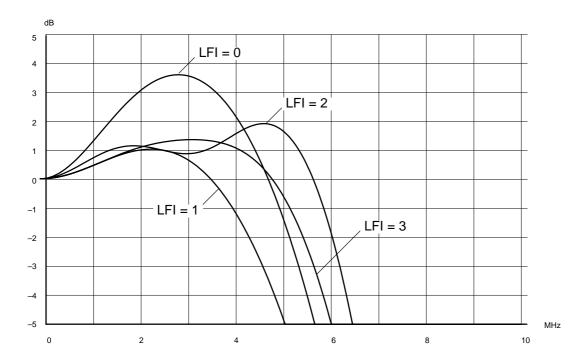

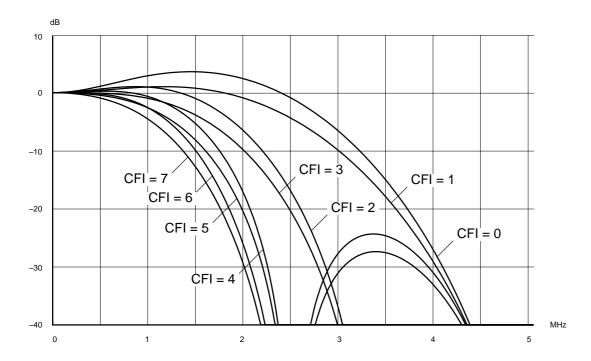

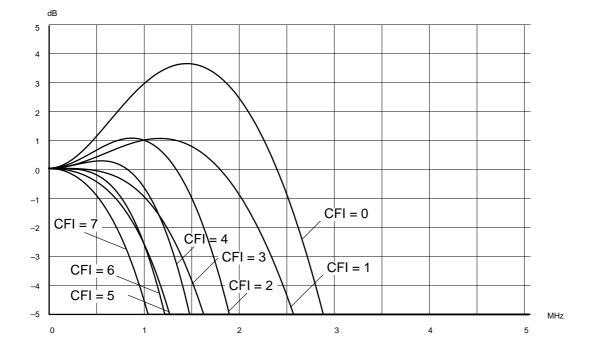

- 1. Luma and chroma interpolation filters (see attachment)

- Luma interpolation filters have been improved in bandwidth and noise performance.

- Chroma interpolation filters have been improved in noise performance.

#### 2. Vertical blank circuit

- Luma and chroma have been set to black from lines 1 to 23, lines 311 to 335, and lines 623 to 625.

- If 'VPSD' is set to zero, the luma signal of line 16 is not blanked. This is required for VPS acquisition.

- 3. AGC circuit with PWM output, polarity, and tristate

- The number of samples used to measure the amplitude of the digitized baseband signal has been increased from 8 to 128.

- If 'IAGC' is set to 1, the AGC output (pin 49) supplies a 16 level PWM signal instead of a 3 level signal.

- If 'AGCP' is set to 1, the polarity of the AGC output is inverted.

- If 'AGCT' is set to 1, the AGC output signal (PWM) supplies three levels: high, low, and tristate.

- 4. Clamping circuit with PWM output, polarity, and tristate

- The number of samples used to measure the DC level of the digitized baseband signal has been increased from 8 to 14.

- If 'DCLE' is set to 1, all 'zero cross points' detected in the databurst are used to measure the DC level of the digitized baseband signal in addition to the 14 samples during the clamping period.

- If 'TZE' is set to 1, only triple 'zero cross points' in the databurst are used to measure the DC level of the digitized baseband signal.

- If 'ICLE' is set to 1, the integral clamp loop is activated.

- If 'CLMP' ist set to 1, the polarity of the clamping output is inverted.

- If 'CLMT" is set to 1, the clamp output signal (PWM) supplies three levels: high, low, and tristate.

## 5. Slave mode for S\_BUS interface

- If 'SBS' is set to 1, the S\_BUS interface is set to slave mode for applications with MSP 3410/MSP 3400.

In this mode

- S\_IDENT signal becomes an input signal

- Audio clock output signal (pin 65) supplies an 18 kHz reference signal for MSP 3410/MSP 3400

- pin XTAL2 (pin 17) is used as an 18.432 MHz input signal supplied from MSP 3410/MSP 3400 (internal load capacitor = 0 pF)

- In S\_BUS slave mode operation, "DCOF" should be set to 1 to achieve minimum input capacitance at clock input XTAL2 (pin 17).

### 6. Soft reset for sound processing part

- If 'SR' is set to 1, the sound processing part of the DMA 2381 is reset.

### The following IM Bus bits have been added in Table 4–1 and Table 4–3.

| VPSD | VPS Disable              | 0 = line 16 is not blanked<br>1 = line 16 is blanked                                                        |

|------|--------------------------|-------------------------------------------------------------------------------------------------------------|

| SR   | Sound Reset              | 0 = normal operation<br>1 = sound part of DMA 2381 is reset                                                 |

| IAGC | Improved AGC             | 0 = AGC compatible to DMA 2281<br>1 = improved AGC enabled                                                  |

| DCLE | Digital Clamp Enable     | 0 = clamping compatible to DMA 2281<br>1 = digital clamp enabled                                            |

| TZE  | Triple Zero Enable       | 0 = all 'zero crossing points' are used<br>1 = triple 'zero crossing points' are used only                  |

| ICLE | Integral Clamp Enable    | 0 = clamping compatible to DMA 2281<br>1 = integral clamp enabled                                           |

| TPE  | Tristate Polarity Enable | 0 = CLMP, CLMT, AGCP and AGCT don't care<br>compatible to DMA 2281<br>1 = CLMP, CLMT, AGCP and AGCT enabled |

| CLMP | Clamping Polarity        | 0 = compatible to DMA 2281<br>1 = polarity of clamping output is inverted                                   |

| CLMT | Clamping Tristate        | 0 = compatible to DMA 2281<br>1 = tristate of clamping output is enabled                                    |

| AGCP | AGC Polarity             | 0 = compatible to DMA 2281<br>1 = polarity of clamping output is inverted                                   |

| AGCT | AGC Tristate             | 0 = compatible to DMA 2281<br>1 = tristate of AGC output is enabled                                         |

| SBS  | S_BUS Slave              | 0 = compatible to DMA 2281<br>1 = S_BUS slave mode enabled                                                  |

| DCOF | DCO_Forced               | 0 = audio clock DCO normal operation<br>1 = audio clock DCO forced to minimum input capacitance (XTAL2)     |

#### Attachments:

- IM\_Bus register list of the DMA 2381

- Frequency response of the DMA 2381 luma and chroma filters

page 2 of 12 MICRONAS INTERMETALL

DATA SHEET SUPPLEMENT DMA 2381

## 4.3.1. Control and Status Registers

Note: unused bits must be set to zero for control (receive) registers and are don't care for status (transmit) registers.

Table 4–1: 16-bit DMA control registers, instructions from CCU to DMA

| Address | Label             | Bit No.        | Default<br>Setting | Typical<br>Value | Function                                                                                            |  |  |  |  |

|---------|-------------------|----------------|--------------------|------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| 14      | VCOA              | 0–7            | 0                  | 0                | VCO adjustment (range –128+127)<br>alignment of the 20.25 MHz VCO                                   |  |  |  |  |

| 14      | vcos              | 8–10           | 4                  | 4                | VCO select<br>1 = VCO3 selected<br>2 = VCO2 selected<br>4 = VCO1 selected                           |  |  |  |  |

| 14      | DI1<br>DI2<br>DI3 | 11<br>14<br>15 | 0                  | 0                | disable PLL output (pin 25, 26)<br>if (DI1 . or . DI2 . or DI3) then<br>PLL output = high impedance |  |  |  |  |

| 23      | SAV               | 2–7            | 32                 | 25               | saturation V adjust<br>0: gain = 0<br>63: gain = 2                                                  |  |  |  |  |

| 23      | SAU               | 10–15          | 32                 | 18               | saturation U adjust 0: gain = 0 63: gain = 2                                                        |  |  |  |  |

| 200     | LD                | 3–7            | 4                  | 6                | luma delay adjust (range 030)<br>resolution: 20.25 MHz clock                                        |  |  |  |  |

| 200     | CTS               | 8              | 0                  | 1                | luma contrast switch                                                                                |  |  |  |  |

| 200     | СТ                | 10–15          | 32                 | 16               | luma contrast adjust 0: gain = 0 63: gain = 1 if CTS = 1 63: gain = 2 if CTS = 0                    |  |  |  |  |

| 201     | DSY               | 0              | 1                  | 0                | disable sync outputs (pins 50–53, 58–60)<br>0 = enabled<br>1 = high impedance                       |  |  |  |  |

| 201     | DCL               | 1              | 0                  | 0                | disable clamping output (pin 48)<br>0 = enabled<br>1 = high impedance                               |  |  |  |  |

| 201     | DLC               | 2              | 0                  | 0                | disable luma/chroma output (pin 21–24, 27–38)<br>0 = enabled<br>1 = high impedance                  |  |  |  |  |

| 201     | NIN               | 3              | 0                  | 0                | non interlace 0 = interlace on 1 = interlace off                                                    |  |  |  |  |

| 201     | PLLO              | 4              | 0                  | 0                | PLL open 0 = PLL closed 1 = PLL opened                                                              |  |  |  |  |

| 201     | STA               | 5              | 0                  | 0                | stand alone operation 0 = digital insertion 1 = stand alone                                         |  |  |  |  |

| 201     | СМР               | 6              | 0                  | 0                | chroma output multiplex 0 = 4 x 4 multiplex 1 = 2 x 8 multiplex                                     |  |  |  |  |

Table 4-1, continued

| Address | Label | Bit No.  | Default<br>Setting | Typical<br>Value | Function                                                                                                                                                                            |  |  |  |  |  |

|---------|-------|----------|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 201     | DGC   | 7        | 0                  | 0                | disable gray code converter input signal (pin 39–45) 0 = gray coded 1 = binary coded                                                                                                |  |  |  |  |  |

| 201     | L525  | 8        | 0                  | 0                | 525 lines standard select 0 = 625 lines standard selected 1 = 252 lines standard selected                                                                                           |  |  |  |  |  |

| 201     | LF    | 10–11    | 0                  | 0                | luma filter selection                                                                                                                                                               |  |  |  |  |  |

| 201     | CF    | 13–15    | 0                  | 0                | chroma filter selection                                                                                                                                                             |  |  |  |  |  |

| 202     | BD    | 1–7      | 64                 | 64               | horizontal blank delay adjust (pin 50–52) resolution: 10.125 MHz clock                                                                                                              |  |  |  |  |  |

| 202     | VPSD  | 8        | 0                  | 0                | VPS disable 0 = line 16 is not blanked 1 = line 16 is blanked                                                                                                                       |  |  |  |  |  |

| 202     | SD    | 9–15     | 64                 | 64               | comp. sync delay adjust (pin 53)<br>resolution: 10.125 MHz clock                                                                                                                    |  |  |  |  |  |

| 203     | C1A   | 0–9      | 0                  | 128              | channel 1 packet address                                                                                                                                                            |  |  |  |  |  |

| 203     | C1E   | 10       | 0                  | 1                | channel 1 enable                                                                                                                                                                    |  |  |  |  |  |

| 203     | C1U   | 11       | 0                  | 0                | channel 1 mode update                                                                                                                                                               |  |  |  |  |  |

| 203     | C1M   | 12–15    | 0                  | 12               | channel 1 mode  ×××× linear/nicam hamming/parity protection high/medium quality                                                                                                     |  |  |  |  |  |

|         |       |          |                    |                  | stereo/mono                                                                                                                                                                         |  |  |  |  |  |

| 194     |       | see regi | ster 203           |                  | channel 2                                                                                                                                                                           |  |  |  |  |  |

| 195     |       | see regi | ster 203           |                  | channel 3                                                                                                                                                                           |  |  |  |  |  |

| 196     |       | see regi | ster 203           |                  | channel 4                                                                                                                                                                           |  |  |  |  |  |

| 197     | SFS   | 0–10     | 7                  | 7                | subframe select SFS = sample number of the first bit in the selected subframe examples: DRS = 1, first subframe DRS = 1, second subframe SFS = 106 DRS = 0, first subframe SFS = 14 |  |  |  |  |  |

| 197     | SR    | 12       | 0                  | 0                | sound reset 0 = normal operation 1 = sound part of DMA 2381 is reset                                                                                                                |  |  |  |  |  |

| 197     | CD    | 13       | 0                  | 0                | chip definition 0 = DMA 2280 1 = DMA 2285                                                                                                                                           |  |  |  |  |  |

| 197     | AUM   | 14       | 0                  | 0                | auto mode 0 = auto mode off 1 = sound coding in packet header                                                                                                                       |  |  |  |  |  |

| 197     | DRS   | 15       | 0                  | 1                | data rate select       0 = 10.125 Mbits/s       D2-MAC         1 = 20.25 Mbits/s       C/D-MAC                                                                                      |  |  |  |  |  |

page 4 of 12 MICRONAS INTERMETALL

DATA SHEET SUPPLEMENT DMA 2381

Table 4–1, continued

| Address | Label | Bit No. | Default<br>Setting | Typical<br>Value | Function                                                                                                                       |

|---------|-------|---------|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 198     | AGCT  | 0       | 0                  | 0                | AGC tristate 0 = compatible to DMA 2281 1 = tristate of AGC output is enabled                                                  |

| 198     | AGCP  | 1       | 0                  | 0                | AGC polarity 0 = compatible to DMA 2281 1 = polarity of clamping output is inverted                                            |

| 198     | CLMT  | 2       | 0                  | 0                | clamping tristate 0 = compatible to DMA 2281 1 = tristate of clamping output is enabled                                        |

| 198     | CLMP  | 3       | 0                  | 0                | clamping polarity 0 = compatible to DMA 2281 1 = polarity of clamping output is inverted                                       |

| 198     | CLG   | 4–5     | 0                  | 2                | clamping loop gain                                                                                                             |

| 198     | TPE   | 9       | 0                  | 0                | tristate polarity enable 0 = CLMP, CLMT, AGCP and AGCT don't care compatible to DMA 2281 1 = CLMP, CLMT, AGCP and AGCT enabled |

| 198     | ICLE  | 10      | 0                  | 0                | integral clamp enable 0 = clamping compatible to DMA 2281 1 = integral clamp enabled                                           |

| 198     | TZE   | 11      | 0                  | 0                | triple zero enable 0 = all 'zero crossing points' are used 1 = triple 'zero crossing points' are used only                     |

| 198     | DCLE  | 12      | 0                  | 0                | digital clamp enable 0 = clamping compatible to DMA 2281 1 = digital clamp enabled                                             |

| 198     | IAGC  | 13      | 0                  | 0                | integral clamp enable<br>0 = AGC compatible to DMA 2281<br>1 = improved AGC enabled                                            |

| 198     | CS    | 14–15   | 0                  | 0                | chip select<br>0 = IM bus of DMA 2280 active<br>1 = IM bus of DMA 2285 active                                                  |

Table 4-1, continued

| Address | Label | Bit No. | Default<br>Setting | Typical<br>Value | Function                                                                                                               |  |  |  |  |

|---------|-------|---------|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 199     | PLLS  | 0       | 0                  | 0                | PLL select<br>0 = D/D2 MAC PLL<br>1 = CMAC PLL                                                                         |  |  |  |  |

| 199     | ENF2  | 1       | 0                  | 0                | enable filter 2<br>0 for C/D MAC<br>1 for D2 MAC                                                                       |  |  |  |  |

| 199     | SLS   | 2–3     | 0                  | 1                | slicer select<br>0 for D2-MAC<br>1 for D-MAC<br>2 for C-MAC                                                            |  |  |  |  |

| 199     | PLLG  | 4–5     | 0                  | 2                | PLL gain 0 = maximal gain 3 = minimal gain                                                                             |  |  |  |  |

| 199     | FCD   | 6       | 0                  | 0                | full channel data 0: DBW is gated (pin 52) 1: DBW is active all the time                                               |  |  |  |  |

| 199     | BPH   | 7       | 0                  | 0                | burst phase<br>0 = with DMA 2285<br>1 = only DMA 2280                                                                  |  |  |  |  |

| 199     | SLL   | 8–15    | 0                  | 40<br>0          | slice level (range –128+127)<br>for D/D2-MAC<br>for C-MAC                                                              |  |  |  |  |

| 204     | SBE   | 0–3     | 0                  | 15               | S bus enable  x x x x channel 1 enable  channel 2 enable  channel 3 enable  channel 4 enable                           |  |  |  |  |

| 204     | DGT   | 4–7     | 0                  | 0                | data group type selection                                                                                              |  |  |  |  |

| 204     | POR   | 8       | 0                  | 0                | packet 0 reset  1: select first byte in packet 0 buffer (first byte = data group type DGT)                             |  |  |  |  |

| 204     | POC   | 9       | 0                  | 0                | packet 0 clear 1: enable packet 0 buffer to store next packet 0                                                        |  |  |  |  |

| 204     | DSB   | 10      | 1                  | 0                | disable S bus outputs (pins 64, 66, 67)  0 = enabled  1 = high impedance                                               |  |  |  |  |

| 204     | ACS   | 11      | 1                  | 1                | audio clock switch (pin 65) 0: audio clock = main clock 1: audio clock = 18.432 MHz                                    |  |  |  |  |

| 204     | ACF   | 12      | 1                  | 0                | audio clock = 16.432 MHz  audio clock free running  0 = audio clock locked to main clock  1 = audio clock free running |  |  |  |  |

| 204     | SBS   | 13      | 0                  | 0                | S bus slave 0 = compatible with DMA 2281 1 = S bus slave mode enabled                                                  |  |  |  |  |

| 204     | DCOF  | 14      | 0                  | 0                | 0 = audio clock DCO normal operation<br>1 = audio clock DCO forced to minimum input capacitance (XTAL2)                |  |  |  |  |

page 6 of 12 MICRONAS INTERMETALL

Table 4–1, continued

| Address | Label | Bit No. | Default<br>Setting | Typical<br>Value | Function                                  |  |  |  |  |  |

|---------|-------|---------|--------------------|------------------|-------------------------------------------|--|--|--|--|--|

| 205     | T0    | 0       | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T1    | 1       | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T2    | 2       | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T3    | 3       | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T4    | 4       | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T5    | 5       | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T6    | 6       | 0                  | 0                | enable PDAT input                         |  |  |  |  |  |

| 205     | T7    | 7       | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T8    | 8       | 0                  | 0                | disable error concealment                 |  |  |  |  |  |

| 205     | Т9    | 9       | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T10   | 10      | 0                  | 0                | enable BDAT input                         |  |  |  |  |  |

| 205     | T11   | 11      | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T12   | 12      | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T13   | 13      | 0                  | 0                | disable luma/chroma interpolation filters |  |  |  |  |  |

| 205     | T14   | 14      | 0                  | 0                | for test only                             |  |  |  |  |  |

| 205     | T15   | 15      | 0                  | 0                | for test only                             |  |  |  |  |  |

Table 4–2: 16-bit DMA status registers, information from DMA to CCU

| Address | Label | Bit No. | Function                                                                                                              |

|---------|-------|---------|-----------------------------------------------------------------------------------------------------------------------|

| 206     | BER   | 0–7     | bit error rate number of erroneous bits detected by the golay decoder within the 82 packet headers of one frame       |

| 206     | VER   | 8–9     | version 0: C/D/D2-MAC Decoder 1: D2-MAC Decoder 2: D-MAC Decoder 3: C/D2-MAC Decoder                                  |

| 206     | C1S   | 10      | status of sound signal selected by C1A 0: sound signal is inactive or interrupted 1: sound signal is present          |

| 206     | C2S   | 11      | status of sound signal selected by C2A 0: sound signal is inactive or interrupted 1: sound signal is present          |

| 206     | C3S   | 12      | status of sound signal selected by C3A  0: sound signal is inactive or interrupted  1: sound signal is present        |

| 206     | C4S   | 13      | status of sound signal selected by C4A 0: sound signal is inactive or interrupted 1: sound signal is present          |

| 206     | P0S   | 14      | status of packet 0 buffer 0: packet 0 selected by DGT not received 1: packet 0 received                               |

| 206     | SYNC  | 15      | status of frame sync word detector 0: frame sync word not detected within 8 frames 1: frame sync word detected        |

| 207     | WL    | 0–7     | white level measured in line 624 (typical value = 240)                                                                |

| 207     | BL    | 8–15    | black level measured in line 624 (typical value = 16)                                                                 |

| 208     | C1L   | 0–3     | coding law of sound signal selected by C1A                                                                            |

| 208     | C2L   | 4–7     | coding law of sound signal selected by C2A                                                                            |

| 208     | C3L   | 8–11    | coding law of sound signal selected by C3A                                                                            |

| 208     | C4L   | 12–15   | coding law of sound signal selected by C4A  L = 0: companded law                                                      |

|         |       |         | 1: linear law                                                                                                         |

|         |       |         | H = 0: first level protection 1: second level protection                                                              |

|         |       |         | HQ = 0: medium quality sound                                                                                          |

|         |       |         | 1: high quality sound S = 0: monophonic sound                                                                         |

|         |       |         | 1: stereophonic sound                                                                                                 |

| 209     | PSL   | 0–7     | packet 0 syndrom low byte                                                                                             |

| 209     | PSH   | 8–15    | packet 0 syndrom high byte PSL + PSH = 0: packet 0 received without error PSL + PSH > 0: packet 0 received with error |

| 210     | PDL   | 0–7     | packet 0 data low byte                                                                                                |

| 210     | PDH   | 8–15    | packet 0 data high byte                                                                                               |

page 8 of 12 MICRONAS INTERMETALL

Table 4-3: DMA control and status registers, graphical overview

| IC 4-      | <b>-3.</b> DIVI                                      | A COIII               | ioi and                   | Status                                  | regist                               | ers, gra                            | apnicai                               | overvi                      | ew                                                                                                                                                                    |                        |                            |                     |                              |                              |                           |                         |  |  |

|------------|------------------------------------------------------|-----------------------|---------------------------|-----------------------------------------|--------------------------------------|-------------------------------------|---------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|---------------------|------------------------------|------------------------------|---------------------------|-------------------------|--|--|

| Bit<br>No. | MSB<br>15                                            | 14                    | 13                        | 12                                      | 11                                   | 10                                  | 9                                     | 8                           | 7                                                                                                                                                                     | 6                      | 5                          | 4                   | 3                            | 2                            | 1                         | LSB<br>0                |  |  |

| W          | DI3                                                  | DI2                   |                           |                                         | DI1                                  |                                     | VCOS                                  | ı                           | VCOA<br>VCO Adjustment                                                                                                                                                |                        |                            |                     |                              |                              |                           |                         |  |  |

| W          | 0                                                    | 0                     |                           |                                         | 0                                    | 1                                   | 0                                     | 0                           |                                                                                                                                                                       |                        | _                          | AV                  | 0                            |                              |                           |                         |  |  |

| W          |                                                      |                       | C                         | т                                       |                                      |                                     | 0<br>CSE                              | O<br>CTS                    |                                                                                                                                                                       |                        | LD                         |                     |                              |                              | 0                         | 0                       |  |  |

| W          | CI                                                   | CFI<br>nroma Filte    |                           | CSP                                     |                                      |                                     | CSP                                   | 0<br>L525<br>525<br>lines   | DGC<br>Disable<br>Gray                                                                                                                                                | CMP<br>Chroma<br>Mult. | 6<br>STA<br>Stand<br>alone | PLLO<br>PLL<br>open | NIN<br>Non<br>Interl.        | 0 DLC Disable L/C            | 0<br>DCL<br>Clamp.<br>off | DSY Disable Sync.       |  |  |

| w          |                                                      | 0                     | Comp                      | SD osite Sync.                          |                                      | )                                   | 0                                     | 0<br>VPSD<br>VPS<br>Disable | 0                                                                                                                                                                     | 0                      | 0                          | BD<br>Blank Dela    | 0<br>ay                      | 0                            | 0                         | 0                       |  |  |

| W          |                                                      | Chan                  | nel Mode                  | 64                                      | C1U<br>Mode<br>Update                | C1E<br>Channel<br>Enable            |                                       | 0                           |                                                                                                                                                                       |                        | (                          |                     |                              | ss                           |                           | 0                       |  |  |

| w          |                                                      | Chan                  | C2M<br>nel Mode           | L                                       | C2U<br>Mode<br>Update                | C2E<br>Channel<br>Enable            |                                       |                             |                                                                                                                                                                       |                        | (                          | C<br>Channel Pa     | 2A<br>cket Addres            | ss                           |                           |                         |  |  |

| w          | S                                                    |                       | C3M                       | L                                       | 0<br>C3U<br>Mode<br>Update           | C3E<br>Channel<br>Enable            |                                       |                             |                                                                                                                                                                       |                        | (                          | С                   | 100<br>C3A<br>Packet Address |                              |                           |                         |  |  |

| w          | S                                                    |                       |                           | L                                       | 0<br>C4U<br>Mode<br>Update           | 0<br>C4E<br>Channel<br>Enable       |                                       |                             | 100 C4A Channel Packet Address                                                                                                                                        |                        |                            |                     |                              |                              |                           |                         |  |  |

| W          | DRS<br>Data<br>Rate<br>Select                        | AUM<br>Auto<br>Mode   | H<br>CD<br>Chip<br>Defin. | SR<br>Sound<br>Reset                    | 0                                    | 0                                   |                                       |                             | SFS<br>Subframe Select                                                                                                                                                |                        |                            |                     |                              |                              |                           |                         |  |  |

| w          |                                                      |                       | IAGC<br>Improved<br>AGC   | 0<br>DCLE<br>Digital<br>Clamp<br>Enable | 0<br>TZE<br>Triple<br>Zero<br>Enable | ICLE<br>Integral<br>Clamp<br>Enable | TPE<br>Tristate<br>Polarity<br>Enable |                             |                                                                                                                                                                       |                        | L                          | LG<br>mping<br>oop  | CLMP                         | CLMT<br>Clamping<br>Tristate | AGCP<br>AGC<br>Polarity   | AGCT<br>AGC<br>Tristate |  |  |

| W          | (                                                    | )                     | 0                         | Slice Le                                |                                      | 0                                   | 0                                     | 0                           | 0         0         2         2         2         2           BPH         FCD Full Burst Chanel Phase Data         PLL Slicer Enable Filter 2         Enable Filter 2 |                        |                            |                     |                              | PLLT<br>PLL<br>Test          |                           |                         |  |  |

| W          |                                                      | DCOF<br>DCO<br>Forced | SBS<br>S Bus<br>Slave     | ACF<br>Audio<br>Free                    | Switch                               | DSB<br>Disable<br>S Bus             | P0C<br>P0<br>Clear                    | P0R<br>P0<br>Reset          | 0                                                                                                                                                                     | Do<br>Data Gr          | GT<br>oup Type             | 2                   |                              | SI<br>S Bus                  | BE<br>Enable              | 0                       |  |  |

| w          | T15                                                  | T14                   | T13                       | T12                                     | T11                                  | T10                                 | Т9                                    | Т8                          | T7                                                                                                                                                                    | Т6                     | T5                         | T4                  | Т3                           | T2                           | T1                        | ТО                      |  |  |

| R          |                                                      |                       | C4S                       | C3S                                     | C2S                                  | 0<br>C1S                            | V                                     | ER                          | 0                                                                                                                                                                     | 0                      | 0                          | В                   | ER                           | 0                            | 0                         | 0                       |  |  |

| R          | BL                                                   |                       |                           |                                         |                                      |                                     |                                       |                             | WL<br>White Level                                                                                                                                                     |                        |                            |                     |                              |                              |                           |                         |  |  |

| R          |                                                      |                       |                           |                                         |                                      |                                     |                                       | I .                         | C2L C1L Coding Law CH2 Coding Law CH1                                                                                                                                 |                        |                            |                     |                              |                              |                           |                         |  |  |

| R          | S                                                    | l HQ                  |                           |                                         | SH                                   |                                     | <u>  H</u>                            | <u>  L</u>                  | S         HQ         H         L         S         HQ         H         L           PSL           Packet 0 Syndrom Low Byte                                           |                        |                            |                     |                              |                              | <u>  L</u>                |                         |  |  |

| R          |                                                      |                       | F                         |                                         |                                      | te                                  |                                       |                             |                                                                                                                                                                       |                        | F                          |                     |                              | e                            |                           |                         |  |  |

|            | Bit No. Direct W W W W W W W W W W W W W W W W W W W | Bit No.               | Bit No.   MSB   14     W  | Bit No.   15                            | No.   MSB                            | No.   NSB   14                      | No.                                   | Street                      | No.                                                                                                                                                                   | No.   NSB   14         | No.                        | No.                 | No                           | No.                          | No.                       | No.                     |  |  |

Bits must be set to zero for write registers (W) and are don't care for read registers (R)

Bits not used in DMA 2280 registers, but in other devices

DMA 2381 DATA SHEET SUPPLEMENT

Table 4-4: VCU control and status registers, graphical overview

| Addr.<br>No. | Bit<br>No.<br>Direct. | MSB<br>15                                                                                           | 14 | 13 | 12        | 11                     | 10 | 9 | 8 | 7                       | 6                         | 5                    | 4  | 3 | 2                                | 1                     | LSB<br>0                |  |  |

|--------------|-----------------------|-----------------------------------------------------------------------------------------------------|----|----|-----------|------------------------|----|---|---|-------------------------|---------------------------|----------------------|----|---|----------------------------------|-----------------------|-------------------------|--|--|

| 16           | W                     | SCS NIE Noise VI2 COB BCR Chroma Invert. Video Sync Enable Input 2 Code Bits Beam Current Reduction |    |    |           |                        |    |   |   |                         | BR<br>Brightness          |                      |    |   |                                  |                       |                         |  |  |

| 17           | W                     | 1                                                                                                   | 0  | 0  | Cutoff Vo | 7<br>CR<br>oltage Red  |    |   | 0 |                         |                           | YDA<br>Luma<br>Adder |    |   |                                  |                       |                         |  |  |

| 18           | W                     |                                                                                                     |    |    | С         | 27<br>G<br>tage Green  |    |   |   | DG<br>White Drive Green |                           |                      |    |   |                                  |                       | BLD<br>Blank<br>Disable |  |  |

| 19           | W                     |                                                                                                     |    |    | C         | 27<br>CB<br>Itage Blue |    |   |   |                         | 127  DB  White Drive Blue |                      |    |   |                                  |                       |                         |  |  |

|              |                       |                                                                                                     |    |    | 1         | 27                     |    |   |   | 127                     |                           |                      |    |   |                                  |                       | Adder<br>Shift<br>0     |  |  |

| 27           | W                     |                                                                                                     |    |    |           |                        |    |   |   |                         |                           | GBC<br>GB Contras    | ŧt |   | DGD<br>Double<br>Gain<br>Disable | BEN<br>Bit<br>Enlarg. |                         |  |  |

|              |                       |                                                                                                     |    |    |           | 0                      |    |   |   |                         |                           |                      | 32 |   |                                  | 1                     | 1                       |  |  |

Bits must be set to zero for write registers (W) and are don't care for read registers (R)

page 10 of 12 MICRONAS INTERMETALL

# Frequency Responses of the DMA 2381

# a) Luminance frequency response

## b) Chrominance frequency response

page 12 of 12 MICRONAS INTERMETALL