## Contents

| Page                                                                                                                                                                                                       | Section                                                                                                                                                                                                                                                    | Title                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                                                                                                                                                                                                          | 1.                                                                                                                                                                                                                                                         | Introduction                                                                                                                                                                                                                                                                |

| 4                                                                                                                                                                                                          | 1.1.                                                                                                                                                                                                                                                       | General Information                                                                                                                                                                                                                                                         |

| 4                                                                                                                                                                                                          | 1.2.                                                                                                                                                                                                                                                       | Environment                                                                                                                                                                                                                                                                 |

| 5                                                                                                                                                                                                          | 2.                                                                                                                                                                                                                                                         | Chip Architecture                                                                                                                                                                                                                                                           |

| 6                                                                                                                                                                                                          | 3.                                                                                                                                                                                                                                                         | Video Processor                                                                                                                                                                                                                                                             |

| 6                                                                                                                                                                                                          | 3.1.                                                                                                                                                                                                                                                       | Code Converter                                                                                                                                                                                                                                                              |

| 6                                                                                                                                                                                                          | 3.2.                                                                                                                                                                                                                                                       | Video Descrambler                                                                                                                                                                                                                                                           |

| 6                                                                                                                                                                                                          | 3.3.                                                                                                                                                                                                                                                       | Interpolation Filter                                                                                                                                                                                                                                                        |

| 6                                                                                                                                                                                                          | 3.4.                                                                                                                                                                                                                                                       | Clamping and Video Gate                                                                                                                                                                                                                                                     |

| 7                                                                                                                                                                                                          | 4.                                                                                                                                                                                                                                                         | PRBS Generator                                                                                                                                                                                                                                                              |

| 7                                                                                                                                                                                                          | 4.1.                                                                                                                                                                                                                                                       | Video PRBS Generator                                                                                                                                                                                                                                                        |

| 7                                                                                                                                                                                                          | 4.2.                                                                                                                                                                                                                                                       | Packet PRBS Generator                                                                                                                                                                                                                                                       |

| 7                                                                                                                                                                                                          | 4.3.                                                                                                                                                                                                                                                       | VBI Descrambler                                                                                                                                                                                                                                                             |

| 8                                                                                                                                                                                                          | 5.                                                                                                                                                                                                                                                         | Line 625 Processor                                                                                                                                                                                                                                                          |

| 8                                                                                                                                                                                                          | 5.1.                                                                                                                                                                                                                                                       | Majority Decision                                                                                                                                                                                                                                                           |

| 8                                                                                                                                                                                                          | 5.2.                                                                                                                                                                                                                                                       | BCH Check                                                                                                                                                                                                                                                                   |

| 8                                                                                                                                                                                                          | 5.3.                                                                                                                                                                                                                                                       | Frame Counter Flywheel                                                                                                                                                                                                                                                      |

| 8                                                                                                                                                                                                          | 5.4.                                                                                                                                                                                                                                                       | RTCI Detector                                                                                                                                                                                                                                                               |

| 9                                                                                                                                                                                                          | 6.                                                                                                                                                                                                                                                         | Sound Processor                                                                                                                                                                                                                                                             |

| 9                                                                                                                                                                                                          | 6.1.                                                                                                                                                                                                                                                       | The S Bus Interface and the S Bus                                                                                                                                                                                                                                           |

| 9                                                                                                                                                                                                          | 0.1.                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                             |

| 9<br>10                                                                                                                                                                                                    | <b>7.</b>                                                                                                                                                                                                                                                  | Packet Processor                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                             |

| 10                                                                                                                                                                                                         | 7.                                                                                                                                                                                                                                                         | Packet Processor                                                                                                                                                                                                                                                            |

| <b>10</b><br>10<br>11<br><b>12</b>                                                                                                                                                                         | <b>7.</b><br>7.1.<br>7.2.<br><b>8.</b>                                                                                                                                                                                                                     | Packet Processor<br>Packet Acquisition<br>Packet Descrambler<br>Interface Processor                                                                                                                                                                                         |

| <b>10</b><br>10<br>11<br><b>12</b><br>12                                                                                                                                                                   | <b>7.</b><br>7.1.<br>7.2.<br><b>8.</b><br>8.1.                                                                                                                                                                                                             | Packet Processor<br>Packet Acquisition<br>Packet Descrambler<br>Interface Processor<br>Fast Processor                                                                                                                                                                       |

| <b>10</b><br>10<br>11<br><b>12</b><br>13                                                                                                                                                                   | <b>7.</b><br>7.1.<br>7.2.<br><b>8.</b><br>8.1.<br>8.2.                                                                                                                                                                                                     | Packet Processor<br>Packet Acquisition<br>Packet Descrambler<br>Interface Processor<br>Fast Processor<br>IM Bus Interface                                                                                                                                                   |

| <b>10</b><br>10<br>11<br><b>12</b><br>13<br>13                                                                                                                                                             | <b>7.</b><br>7.1.<br>7.2.<br><b>8.</b><br>8.1.                                                                                                                                                                                                             | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and Instructions                                                                                                                                      |

| <b>10</b><br>10<br>11<br><b>12</b><br>13<br>13<br>13                                                                                                                                                       | <ol> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> </ol>                                                                                                                                   | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM Interface                                                                                                                        |

| <b>10</b><br>10<br>11<br><b>12</b><br>13<br>13<br>13<br>18<br>19                                                                                                                                           | <ol> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> </ol>                                                                                                                     | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory Map                                                                                                         |

| <ul> <li>10</li> <li>10</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>18</li> <li>19</li> <li>19</li> </ul>                                                                         | <ol> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> </ol>                                                                                                                 | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode Register                                                                                            |

| <ul> <li>10</li> <li>10</li> <li>11</li> <li>12</li> <li>13</li> <li>13</li> <li>18</li> <li>19</li> <li>19</li> <li>20</li> </ul>                                                                         | <ol> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> <li>8.4.2.</li> </ol>                                                                                     | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode RegisterPac1 Register                                                                               |

| <ul> <li>10</li> <li>10</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>18</li> <li>19</li> <li>19</li> <li>20</li> <li>21</li> </ul>                                                 | <ol> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> <li>8.4.2.</li> <li>8.4.3.</li> </ol>                                                                     | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode RegisterPac1 RegisterPac2 Register                                                                  |

| <ol> <li>10</li> <li>10</li> <li>11</li> <li>12</li> <li>13</li> <li>13</li> <li>18</li> <li>19</li> <li>19</li> <li>20</li> <li>21</li> <li>23</li> </ol>                                                 | <ol> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> <li>8.4.2.</li> <li>8.4.3.</li> <li>8.4.4.</li> </ol>                                                     | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode RegisterPac1 RegisterPac2 RegisterCoeff Register                                                    |

| <ol> <li>10</li> <li>10</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>13</li> <li>13</li> <li>19</li> <li>19</li> <li>20</li> <li>21</li> <li>23</li> <li>24</li> </ol>             | <ol> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> <li>8.4.2.</li> <li>8.4.3.</li> <li>8.4.4.</li> <li>8.4.5.</li> </ol>                                     | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode RegisterPac1 RegisterPac2 RegisterCoeff RegisterCW Register                                         |

| <ol> <li>10</li> <li>10</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>18</li> <li>19</li> <li>19</li> <li>20</li> <li>21</li> <li>23</li> <li>24</li> <li>25</li> </ol>             | <ol> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> <li>8.4.2.</li> <li>8.4.3.</li> <li>8.4.4.</li> <li>8.4.5.</li> <li>8.4.6.</li> </ol>                                 | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode RegisterPac1 RegisterPac2 RegisterCoeff RegisterCW RegisterError Buffer                             |

| <ol> <li>10</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>13</li> <li>19</li> <li>19</li> <li>20</li> <li>21</li> <li>23</li> <li>24</li> <li>25</li> <li>26</li> </ol>             | <ol> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> <li>8.4.2.</li> <li>8.4.3.</li> <li>8.4.4.</li> <li>8.4.5.</li> <li>8.4.6.</li> <li>8.4.7.</li> </ol>     | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode RegisterPac1 RegisterPac2 RegisterCoeff RegisterCW RegisterError BufferPacket Buffer  |

| <ol> <li>10</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>13</li> <li>19</li> <li>19</li> <li>20</li> <li>21</li> <li>23</li> <li>24</li> <li>25</li> <li>26</li> <li>28</li> </ol> | <ol> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> <li>8.4.2.</li> <li>8.4.3.</li> <li>8.4.4.</li> <li>8.4.5.</li> <li>8.4.6.</li> <li>8.4.7.</li> <li>8.4.8.</li> </ol> | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode RegisterPac1 RegisterPac2 RegisterCoeff RegisterCW RegisterError BufferPacket BufferLine 625 Buffer |

| <ol> <li>10</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>13</li> <li>19</li> <li>19</li> <li>20</li> <li>21</li> <li>23</li> <li>24</li> <li>25</li> <li>26</li> </ol>             | <ol> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.2.1.</li> <li>8.3.</li> <li>8.4.</li> <li>8.4.1.</li> <li>8.4.2.</li> <li>8.4.3.</li> <li>8.4.4.</li> <li>8.4.5.</li> <li>8.4.6.</li> <li>8.4.7.</li> </ol>     | Packet ProcessorPacket AcquisitionPacket DescramblerInterface ProcessorFast ProcessorFast ProcessorIM Bus InterfaceIM Bus Addresses and InstructionsDRAM InterfaceDRAM Memory MapMode RegisterPac1 RegisterPac2 RegisterCoeff RegisterCW RegisterError BufferPacket Buffer  |

# Contents, continued

| Page | Section | Title                                      |

|------|---------|--------------------------------------------|

| 31   | 9.      | Specifications                             |

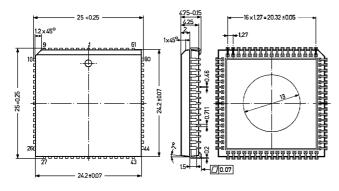

| 31   | 9.1.    | Outline Dimensions                         |

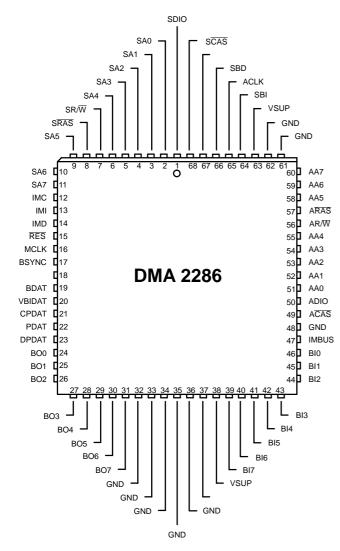

| 31   | 9.2.    | Pin Connections                            |

| 34   | 9.3.    | Pin Configuration                          |

| 34   | 9.4.    | Pin Descriptions                           |

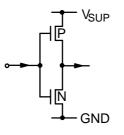

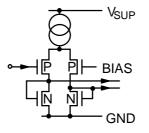

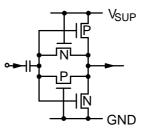

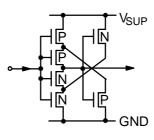

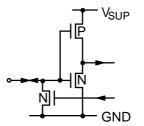

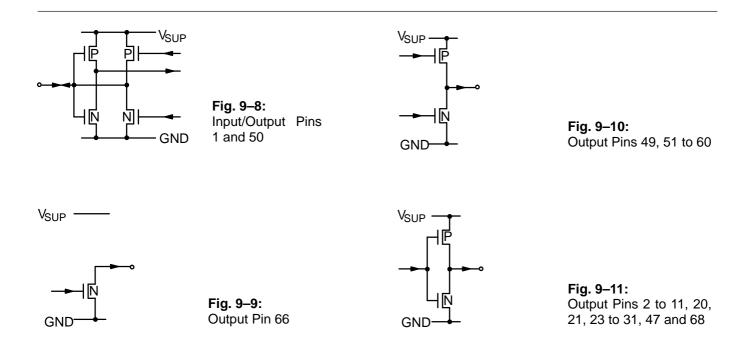

| 35   | 9.5.    | Pin Circuits                               |

| 36   | 9.6.    | Electrical Characteristics                 |

| 36   | 9.6.1.  | Absolute Maximum Ratings                   |

| 37   | 9.6.2.  | Recommended Operating Conditions           |

| 39   | 9.6.3.  | Characteristics                            |

| 40   | 9.6.4.  | Sound DRAM Interface Characteristics       |

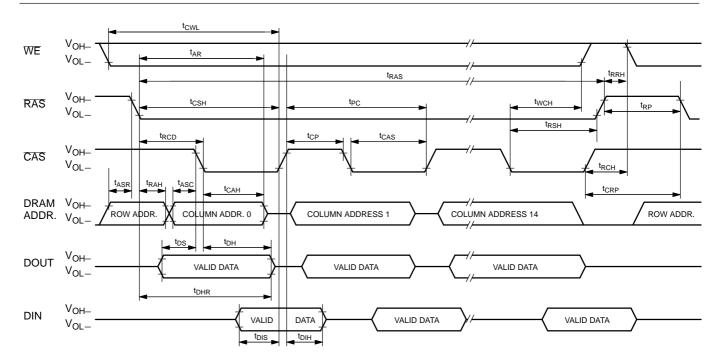

| 42   | 9.6.5.  | Acquisition DRAM Interface Characteristics |

| 44   | 9.6.6.  | Waveforms                                  |

| 40   | 40      | Deferences                                 |

| 46 10. References |

|-------------------|

|-------------------|

The DMA 2275 and DMA 2286 C/D/D2-MAC Descrambler

#### 1. Introduction

#### 1.1. General Information

The DMA 2275 is a digital real-time descrambling processor for the D2–MAC/Packet system. Together with the D2–MAC/Packet decoder chip DMA 2271, it can be used to build up a D2–MAC/Packet conditional access receiver.

The DMA 2286 is a digital real-time descrambling processor for the C/D/D2–MAC/Packet system. Together with the C/D/D2–MAC/Packet decoder chip DMA 2281, it can be used to build up a C/D/D2–MAC/Packet conditional access receiver.

The programmable VLSI circuits in CMOS technology are housed in 68–pin packages and contain on a single silicon chip the following functions:

#### DMA 2275 and DMA 2286

- descrambling of MAC video signal

- interpolation of MAC video signal (aspect ratio 16:9)

- descrambling of MAC data packets

- descrambling of VBI-teletext

- entitlement packet acquisition

- supplementary general purpose packet acquisition

- line 625 acquisition

- communication with external microprocessor via the IM bus

#### DMA 2286 only

- one subframe sound processing C/D/D2-MAC

### 1.2. Environment

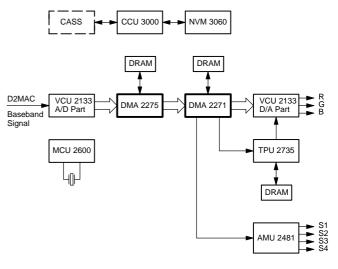

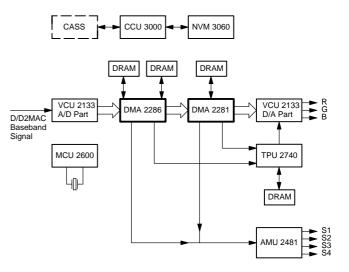

Figures 1–1 and 1–2 show how the descrambler chips DMA 2275 and DMA 2286 can be implemented into a MAC conditional access receiver together with other circuits of ITT's DIGIT 2000 digital TV system. These re-

ceivers provide descrambling facility for one video service and up to four audio or data services including VBI-teletext. It is important to notice that the DMA 2275 or DMA 2286 do not include any decryption or security functions. These functions will be carried out by one or more conditional access subsystems (CASS) which communicate with the descrambler chip via the central control unit (CCU) and the IM bus.

Fig. 1–1: Block diagram for a stand–alone D2–MAC decoder

Fig. 1-2: Block diagram for a stand-alone D/D2-MAC decoder

## 2. Chip Architecture

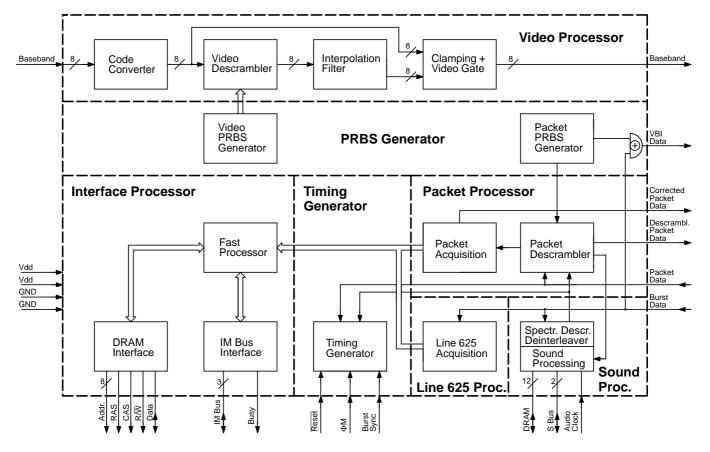

Figure 2–1 shows the architecture of the descrambling chip DMA 2286. The DMA 2275 architecture is identical to the that of the DMA 2286, except that the sound processor is missing. The chips can be subdivided into several functional blocks.

### DMA 2275 and DMA 2286:

#### Video Processor

descrambling, panning and interpolation of the video signal

#### **PRBS** Generator

- delivers cut points and cipher streams

#### Line 625 Processor

acquisition of service identification data and real time control information

#### **Packet Processor**

acquisition of entitlement packets, acquisition of general purpose packets, selection of cipher stream, descrambling of data packets

#### **Interface Processor**

- management of internal and external data transfer

### **Timing Generator**

- delivers internal chip timing

#### DMA 2286 only:

#### Sound Processor

spectrum descrambling of data burst, packet deinterleaving (one subframe only), sound packet processing (one subframe only)

Fig. 2-1: Block diagram of the DMA 2286

## 3. Video Processor

The video processor consists of:

- Code Converter

- Video Descrambler

- Interpolation Filter

- Clamping and Video Gate

## 3.1. Code Converter

Input for the video processor is the digitized baseband signal which may be delivered by the VCU 2133 in parallel Gray code or by the UVC 3130 in simple binary code. Therefore, a code converter from Gray to binary code is intended. This converter can be disabled under software control (bit 6 of video mode register) and can be switched from 7 to 8 bit input (test bit TT6).

## 3.2. Video Descrambler

To make the transmitted video signal unintelligible, the luma and/or chroma component are cut into two segments in the MAC encoder. These two segments are then transposed. Task of the video descrambler is to retranspose the segments into their original waveform.

Three different video waveforms are possible:

- clear

- double-cut component rotation

- single-cut line rotation

The video descrambler has to cope with all these video waveforms. In any case the output signal has a constant delay of 1296 + 4 clock periods in order to avoid synchronization problems during change of the video scrambling mode. For any video configurations not corresponding to Fig. 3, part 2, p. 75 of ref. 1, the video descrambler should be disabled by the software. The signal is then passed through the descrambler unaffected except for the delay of one line.

The baseband data burst signal passes the video descrambler through a special shift register, luma and chroma rotation is done in within two video RAMs. The video RAMs are subdivided into chroma and luma segments which are organized as ringbuffer. The concerning address counter is loaded every line with a start value depending on the cut point (CPL or CPC) in case of scrambling, on the pan vector (PANV) in case of 16:9 aspect ratio and in any case on an offset value which is programmable (FP register 33 and 34). The calculation of the start address is done by the Fast Processor in real time. The expansion of the compatible 4:3 part in case of 16:9 aspect ratio is done by reading every third sample twice.

## 3.3. Interpolation Filter

If the compatible 4:3 part of a 16:9 picture is to be processed (see Fig. 7, part 2, p. 79 of ref. 1), only this part of the luma and chroma component is read out of the video memory (262 chroma samples, 523 luma samples). An interpolation filter is then used to regain the number of samples expected by the DMA 2271 or DMA 2281 (349 chroma samples, 697 luma samples). The sampling rate ratio is 4:3. The filter function is defined by a set of 16 coefficients, which are programmable. Download of these coefficients into the interpolation filter is a one shot function triggered by software (bit 4 of video\_mode register).

The interpolation is not influenced by the video scrambling method, because the output signal of the video memory appears unscrambled. The position of the compatible 4:3 part is programmable so that user panning is possible. The panning can also be controlled by the broadcaster when sending real time pan vectors in line 625. The selection of these two panning modes is done by bit 7 of the scram\_mode registers.

The high frequency losses in the interpolation filter can be partly compensated with a peaking filter. Low peaking increases the signal level about 6 dB at 5 MHz, high peaking increases the signal level about 10 dB at 5 MHz. Peaking is controlled with bit 0 and 1 in the video\_mode register.

Alternatively the interpolation and peaking filter can be used for baseband filtering. It is then enabled not only during active video, but also during the data burst and VBI transmission. The filter coefficients have to be changed for this application.

## 3.4. Clamping and Video Gate

The DC level of the analog baseband signal is controlled by the clamping circuit of the DMA 2271 or DMA 2281 decoder chip which measures the clamping period of each line. The line store in the video descrambler of the DMA 2275 or DMA 2286 would cause a line delay within the clamping control loop with all corresponding problems.

Therefore, the line store of the descrambler chip is bypassed during the clamping period to avoid the line delay. The position of the clamping bypass within the line can be programmed in steps of 99 clock cycles (bit 3–0 in mac\_mode register). Clamp position '0' would be located after the first subframe of a D–MAC signal. Clamp position '1' is the default specified in ref 1. The clamp bypass is automatically disabled in line 625 and line 1.

Finally, a video gate is provided to switch the luminance component to black and the chrominance component to zero in case of denied access to the video service. This gate can be used in country by country control (CbCC) applications to black out special programs under software control (bit 5 of video\_mode register).

## 4. PRBS Generator

The PRBS generator delivers pseudo random binary sequences to descramble the video signal, packet data, and VBI data. It consists of:

- Video PRBS Generator

- Packet PRBS Generator

## 4.1. Video PRBS Generator

The Video PRBS generator delivers the cut points for the luma and chroma component as two bytes per line (CPL and CPC). These two bytes are calculated in the PRBS 2 generator described in detail in Fig. 4, part 6, p. 205 and Fig. 3, appendix to part 6, p. 309 of ref. 1.

The PRBS 2 generator is clocked 16 times at the beginning of each line in a way that the cut points are available before start of the vision signal. The PRBS 2 generator is loaded with a 60 bit video initialization word (VIW) at the beginning of each frame. The video initialization word is a combination of the 8 bit frame counter (FCNT) and a 60 bit video control word (VCW) which is either one of the local control words (LCW\_even and LCW\_odd) or one of the video control words received from the CASS (VCW\_even and VCW\_odd).

The selection of even or odd control words is done with the LSB of the conditional access frame counter (CAFCNT). CAFCNT and FCNT are delivered by the line 625 processor. All control words (including the local control words) are read out of the control word registers of the external acquisition DRAM. These registers must be defined by CCU software, which gets control words from the CASS and initializes the local control words with all bits set to '1'.

## 4.2. Packet PRBS Generator

The packet PRBS generator delivers the descrambling sequence for four different data channels which may carry sound or teletext or any other data service. The sequence is used to descramble the 720 useful data bits (after packet header and PT–byte) of packets carrying a scrambled service component.

The packet PRBS generator consists of four PRBS 1 generators and four PRBS 3 generators described in detail in Fig. 3, part 6, p. 203, Fig. 5, part 6, p. 207, Fig. 2, appendix to part 6, p. 308 and Fig. 4, appendix to part 6, p. 310 of ref. 1.

The four data initialization words (DIW) for the PRBS 1 generators are derived in the same way as in the video PRBS generator and are loaded at the beginning of each frame. Each PRBS 1 generator is then clocked 61 times before receiving the next data packet and the serial output, called packet initialization word (PIW), is loaded into the PRBS 3 generator.

The actual descrambling sequence is generated in one of the PRBS 3 generators which is selected by the packet recognition each time a scrambled packet arrives. Channel 1 of the packet recognition selects the PRBS 3 generator which is loaded from the PRBS 1 generator initialized with DCW1 and so on.

## 4.3. VBI Descrambler

Although there is no specification of VBI descrambling in ref. 1, the DMA 2275 or DMA 2286 provide means of descrambling VBI data in a simple manner.

The PRBS 1 generator for channel 4 can be used to descramble 2–4 PSK demodulated or duobinary decoded data in the VBI (e.g. VBI–teletext). In this case the PRBS 1 generator will be clocked with 10.125 MHz (D2–MAC) or 20.25 MHz (C/D–MAC) and its serial output is directly used to descramble the VBI data burst. The VBI\_PRBS starts with bit 117 and stops after bit 648 (D2–MAC) or bit 1296 (D–MAC) of each data burst of the VBI. The VBI is defined from line 1 to 22 and line 311 to 334 inclusive. Due to the fast processor software (see Fig. 8–1), the PRBS 1 generator can only be loaded in line 7. This means that the VBI descrambler operates from line 1 to line 6 with the data initialization word (DIW) of the previous frame. During line 7 the VBI data output (pin 20) is unpredictable.

The delay between data burst input (pin 19) and descrambled VBI data output (pin 20) is 4 clock periods.

## 5. Line 625 Processor

The line 625 processor is loaded via the data burst input. Line 625 is identified by checking the sync pulse of the data burst input. The normal sync pulse covers only 6 bits of the line synchronization word (LSW), the sync pulse of line 625 covers 102 bits of the frame synchronization data (FSD) and is directly followed by:

| <ul> <li>5 bit</li> <li>71 bit</li> <li>470 bit</li> </ul> | UDT<br>SDF<br>RDF | unified data time<br>static data frame<br>repeated data frame |

|------------------------------------------------------------|-------------------|---------------------------------------------------------------|

| 546 bit                                                    |                   | line 625 data                                                 |

In case of C–MAC or D–MAC the 546 bits of UDT, SDF and RDF are interleaved with PRBS data. The PRBS data are discarded by using a clock divider so that the clock frequency for the line 625 processor is unique for C–, D– and D2–MAC (10.125 MHz). UDT, SDF and the error corrected TDMCTL data are stored into the external acquisition DRAM (see figure "Line 625 Buffer") and are updated every frame.

The line 625 processor consists of:

- Majority Decision

- BCH Check

- Frame Counter Flywheel

- RTCI Detector

# 5.1. Majority Decision

The RDF consists of five successive identical 94 bit data blocks transmitting time division multiplex control (TDMCTL) information. The fivefold repetition is used by a 3 of 5 majority decision including the BCH suffix.

# 5.2. BCH Check

SDF and TDMCTL are each protected by a 14 bit BCH suffix. The BCH check is only used for error detection. BCH check for the TDMCTL is done after majority decision. The complete SDF (71 bit) or TDMCTL (94 bit) information is stored into DRAM together with two error flags SDF\_Error and TDM\_Error indicating the result of the BCH check.

# 5.3. Frame Counter Flywheel

The 8 bit frame counter (FCNT) is used in conjunction with the PRBS generators of the descrambling system. The correct acquisition of FCNT is essential to maintain a scrambled service. Therefore, a flywheel technique is used in a way that a free running frame counter is synchronized from time to time with the received FCNT in line 625. In this case even the loss of several line 625 data will not disturb the service acquisition.

The CAFCNT LSB is used to select even and odd control words and allows frame accurate switching from one phase to the other. Therefore, a similar flywheel technique is used to protect this LSB. In fact, the internal CAFCNT LSB is the 9th bit of the free running frame counter and is synchronized by the actually transmitted CAFCNT LSB after a majority decision over several frames.

# 5.4. RTCI Detector

A special TDMCID code in the TDMCTL indicates the presence of real time control information (RTCI) transmitted instead of TDMS and LINKS. TDMCID = '81' (hex) is defined to signal the transmission of real time panning information.

The pan vector PANV is needed for panning the 4:3 portion of a 16:9 picture. In this case the 63 bits of TDMS and LINKS are substituted with 56 bits of PANV. PANV is organized in seven bytes giving the pan vector for seven consecutive frames starting from the second frame after transmission. Each byte of PANV defines in 2's complement format the offset of the 4:3 portion from the center position (see Fig. 7, part 2, p. 79 of ref. 1).

After detection of TDMCID = '81' (hex) the following seven bytes are stored in a FIFO which is read out once a frame with one frame delay. If the FIFO is empty the last byte will be repeated until a new pan vector is received. The TDMCTL transmitting the pan vector will be stored into the line 625 buffer like any other TDMCTL information.

If user panning is selected by software, the pan vector inside TDMCID will be ignored and a user defined pan vector will be used instead, allowing the user to pan the picture himself. In any case the recently transmitted pan vector in line 625 is stored in the pan output register to allow the software to make a smooth return between different pan positions.

## 6. Sound Processor

The DMA 2286 contains an additional sound processor, which is loaded via the data burst input. The sound processor consists of:

- spectrum descrambler

- deinterleaver

- sound processing

- S Bus interface

These blocks are identical to the sound processing blocks of the DMA 2281 (see ref. 2). Both sound processors are able to decode 4 sound channels out of one single subframe. The subframe position is programmable to allow full channel data reception.

On the DMA 2286 the output of the deinterleaver is internally fed to the packet descrambler and the descrambled packets are going back to the sound processor.

The sound processor needs a separate external  $64 \text{ k} \times 1$  bit DRAM, which is independent from the acquisition DRAM and is not accessible by software.

## 6.1. The S Bus Interface and the S Bus

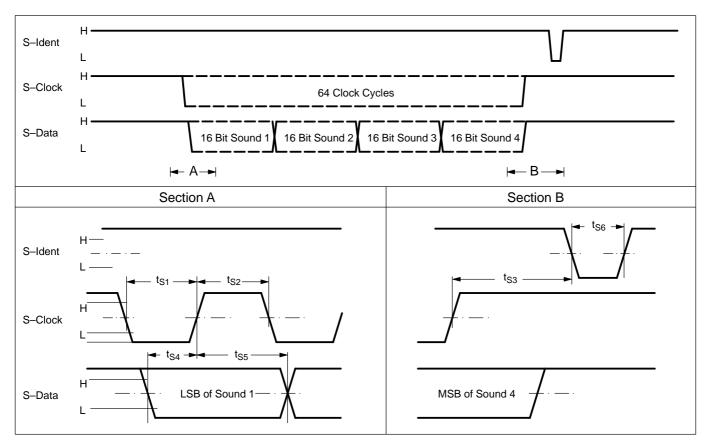

The S bus has been designed to connect the digital sound output of the DMA 2271 or DMA 2281 MAC Decoder or the MSP 2400 NICAM Demodulator/Decoder to audio–processing ICs such as the AMU 2481 Audio Mixer or the ACP 2371 Audio Processor etc., and to connect these ICs one to the other. The S bus is a unidirectional, digital bus which transmits the sound information in one direction only, so that it is not necessary to solve priority problems on the bus.

The S bus consists of the three lines: S–Clock, S–Ident, and S–Data. The DMA 2271, DMA 2281 or the MSP 2400 generates the signals S–Clock and S–Ident, which control the data transfer to and between the various processors which follow the DMA 2271, DMA 2281 or the MSP 2400. For this, the S–Clock and S–Ident inputs of all processors in the system are connected to the S– Clock and S–Ident outputs of the DMA 2271, DMA 2281 or the MSP 2400. S–Data output of the DMA 2271, DMA 2281 or MSP 2400 is connected to the S–Data input of the next following AMU, the AMU's S–Data output is connected to the ACP's S–Data input and so on.

The sound information is transmitted in frames of 64 bits, divided into four successive 16—bit samples. Each sample represents one sound channel. The timing of a complete transmission of four samples is shown in Fig. 9–13, the times are specified under "Recommended Operating Conditions". The transmission starts with the LSB of the first sample. The S–Clock signal is used to write the data into the receiver's input register. the S–Ident signal marks the end of one frame of 64 bits and is used as latch pulse for the input register. The repetition rate of S–Ident pulses is identical to the sampling rate of the D/D2–MAC or NICAM sound signal; thus it is possible to transfer four sound channels simultaneously.

The S bus interface of the DMA 2286 mainly consists of an output register, 64–bit wide. The timing to write bit by bit is supplied by the Audio–Clock signal. In the case of an S–Ident pulse, the contents of the output register are written to the S–Data output.

The S\_Bus\_Data line of the DMA 2286 can be connected to that of the DMA 2281 if only one audio processor AMU 2481 is available. In this case each S\_Bus channel of both DMA chips can be enabled or disabled under software control.

## 7. Packet Processor

The packet processor is loaded via the scrambled packet data input with packets of one subframe delivered by the DMA 2271 or DMA 2281 and additionally has an internal connection to the deinterleaver of the DMA 2286 for packets of the other subframe. Packet data on these lines are already spectrum descrambled and deinterleaved. The packet header and the PT byte have already been corrected. The transmission of each packet starts with a '0' bit followed by 751 bit packet data with a unique bit rate of 10.125 MHz (for C–, D– and D2–MAC).

To avoid simultaneous reception of two packets from different subframes, the packet output of the DMA 2286 has to be delayed in reference to the packet output of the DMA 2281. This can be done with the CD bit in IM\_Bus register 197.

The packet processor consists of:

- Packet Acquisition

- Packet Descrambler

## 7.1. Packet Acquisition

Task of the packet acquisition is to select specific packets out of the packet multiplex. In case of C- or D-MAC packets can be located in one or two subframes, therefore, the packet selection will be repeated in the second subframe if necessary. The selected packets can be error corrected if needed and are stored into packet buffers which are located in the acquisition DRAM.

Due to timing conflicts with the line 625 acquisition, it is not possible to acquire packets in the last (82nd) packet slot of each subframe.

Additionally, all packets of both subframes are available on a separate output pin (corrected packet data output), only that the selected packets are replaced by their error corrected equivalents.

The most common application of the packet acquisition will be the selection of the following packets:

- '0' packets

- EMM packets

- ECM packets

- BI packets

- 2nd level teletext packets

- general purpose data packets

The '0' packets are forming the service identification (SI) channel. The first thing the receiver software has to do is to monitor the SI channel and to configure the receiver according to the SI information. '0' packets are either hamming protected (H[8,4]) or golay protected (Golay

[24,12]). The SI channel is subdivided into 16 data groups which can be identified by the data group (TG) byte immediately following the PT byte of the packet header.

The EMM and ECM packets are essentially carrying encryption keys and control words. Their packet addresses are indicated by the LISTX, ACMM and ACCM parameters of the service identification channel. EMM packets can be addressed to a single customer or a group of customers by means of an address extension field of up to 36 bit, immediately following the PT byte. EMM and ECM packets are highly error protected (Golay [24,12] or Hamming [8,4]).

BI packets are carrying additional interpretation data related to sound packets with the same packet address. They are selected by their PT byte ('00' or '3F'). BI packets are not error corrected.

Second level teletext packets can be selected to do Golay [24,12] correction. They are available then on the corrected packet data output which can be connected to the teletext processor TPU 2740.

Every selected packet is CRC checked regardless of packet type and error protection. The CRC check is done over the full range of 720 bit and does not change any packet data. CRC check, Golay [24,12] and Hamming [8,4] error correction is done in real time, i.e. with 10.125 MHz. In case of packets with Golay [24,12] error protection, the protection bits will be removed before storing these packets into the packet buffer. the packet length is therefore reduced from 96 bytes (full length packet) to 48 bytes (half length packets), doubling the possible number of packets in the related packet buffer. The result of CRC check and the number of uncorrectable Golay or Hamming codes per packet is indicated in a special packet error buffer which holds up to 16 error bytes for every packet buffer. In case of full length packets, only every second entry of the error buffer is used.

Every selected packet is stored into the external acquisition DRAM of the descrambler chip. The DRAM includes 8 independent packet buffers, each offering the data capacity to store 8 full length packets or 16 half length packets. The packet buffers can be read out by software at any time and in any sequence. There are two ways to use these packet buffers. One is the "standard" buffer application where the buffer is automatically closed when it is filled up with packets. The buffer must then be reopened by software to start packet acquisition again. The second way is the "ring" buffer application where the packet buffer is always open and the oldest packets in the buffer are overwritten by the next incoming packets.

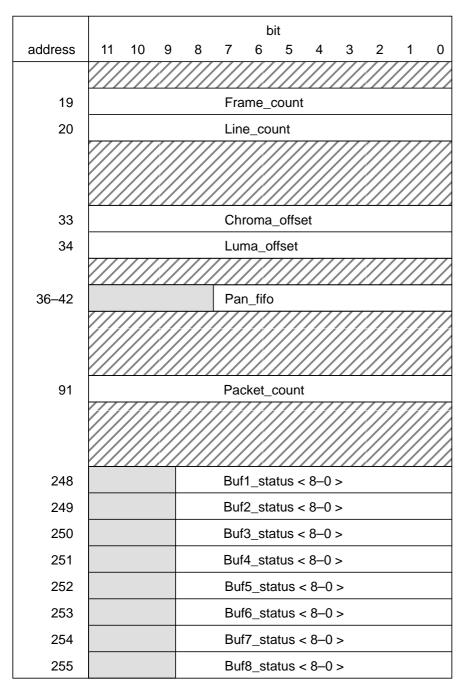

Each packet buffer can be monitored by reading its buffer status. The buffer status is located in the FP memory and includes a buffer pointer (bit 4–0) which indicates the position where the next packet will be stored in numbers of half length packets. In ring buffer application this pointer runs modulo 16 and in standard buffer application the pointer stops at 16. The buffer application (standard/ring) can be defined with bit 5 in the buffer status register. Bit 7 allows to close or reopen the buffer under software control. Bit 6 defines the buffer increment. that means whether the buffer will store full length (96 byte) packets or half length (48 byte) packets.

Each of the 8 packet buffer is attached to a programmable packet filter which selects specific packets out of the packet multiplex depending on packet address (PA), continuity index (CI), packet type (PT) and packet address extension (PAE). The packet address extension can be used to select EMM packets by their specific customer address (UCA, SCA, CCA) or to select ECM packets by command identification (CI or to select the data group type (TG) of '0' packets. This selection is done after error correction.

Each of the 8 packet filter is controlled by a set of registers located in the acquisition DRAM and programmable by software. The 'packet address base' (PAB) registers define the 10 bit packet address and the continuity index. The 'packet address extension' (PAE) registers define up to 36 bit of the address extension field. The 'packet selection control' (PSC) registers define how packets will be selected, error corrected and linked together.

The software should take care of conflicts like programming different packet filters with the same conditions. There must be at least one difference in the combination of packet address, continuity index, packet type, and packet location. Otherwise the result of the packet selection will be undefined.

If packet link is activated, the first packet meeting all programmed conditions is defined as sync packet. Selection of continuation packets is done according to the packet link status. In case of CI link, the continuity index of following packets will be ignored. In case of PT link, the packet type selection is changed to PT2. a special bit in the buffer status indicates if this procedure has been activated by the first sync packet. The packets are then stored into the packet buffer in the same order as they are transmitted. The choice of packet link is independent from the choice of buffer application.

Depending on the page select bit in the PSC register the packet address extension is checked in every packet or only in the sync packet. To select linked EMM packets by customer address this bit should be '0', to select linked '0' packets by data group type this bit should be '1'.

## 7.2. Packet Descrambler

Main task of the packet descrambler is to detect those sound or data packets that have to be descrambled. Four different packet addresses can be recognized. After detection of such a packet the concerning PRBS 3 generator is selected and produces an output sequence of 720 bit to descramble the packet data. The PT–Byte of each selected packet is decoded to disable the PRBS 3 generator output in case of BI packets ('00' or '3F'). The packet descrambler can be switched to "automatic" operation. In this mode the 4 center bits of the packet address are ignored by the packet address comparator.

In case of C– or D–MAC, packets carrying one digital component can be inserted in one or both subframes, therefore the packet recognition will be repeated in the second subframe if necessary.

Because the packet header is not scrambled, the packet recognition has about 20 clock cycles to compare the packet address before start of the descrambling sequence. Therefore there is only a 4 clock cycle delay between packet input and output.

Additionally, a packet gate is provided to remove packets form the packet output in case of denied access to that particular service. These packets are not physically removed – only the 720 bits after the packet header are set to '1'.

Any other packet not selected by the packet recognition passes through the packet descrambler unaffected but with a delay of 4 clock periods.

The packet recognition is controlled by a set of registers located in the acquisition DRAM and programmable by software. The 'scrambled packet address' (SPA) registers define the 10 bit packet address and the 'scrambled packet status' (SPS) registers define packet location and status.

The software should take care of conflicts like programming different SPA and SPS registers in the combination of packet address and packet location. Otherwise, the result of the packet recognition will be undefined.

#### 8. Interface Processor

The interface processor consists of:

- Fast Processor

- IM Bus Interface

- DRAM Interface

## 8.1. Fast Processor

The fast processor (FP) is a RISC–type 12 bit microcontroller built in CMOS technology. The maximum clock frequency of 40 MHz and the internal architecture that allows parallel ALU operation and data transfer to or from internal RAM, make it applicable for very high speed tasks, such as control and parameter calculation in digital signal processors.

The FP is embedded in the DMA 2275 or DMA 2286 with 256 x 12 bit RAM and 2K x 20 bit ROM and runs with 20.25 MHz. The FP performs the following tasks:

- data transfer to and from DRAM interface

- data transfer to and from IM Bus interfaces

- support of packet acquisition

- support of line 625 acquisition

- initialization of PRBS generators

- control of video descrambler

- control of interpolation filter

Fig. 8–1 shows roughly when the different FP tasks are executed within a frame period.

In normal operation the FP will not be directly accessed from outside, that means that the CCU software will not see another processor on the descrambling chip but only a set of registers and buffers which are located either in the acquisition DRAM or in the FP internal memory. The CCU can access both memories via IM Bus.

Changing any register in the DRAM memory by CCU software will not effect the descrambler hardware immediately. The FP will read or update the DRAM memory only on frame boundaries, i.e. from line 622 to line 7 inclusive. Changing registers in the FP memory by CCU software will effect the descrambler hardware immediately.

| Line |                                             |                                    |         |                    |               |                                                                                                               |                    |

|------|---------------------------------------------|------------------------------------|---------|--------------------|---------------|---------------------------------------------------------------------------------------------------------------|--------------------|

| 1    | line_sync                                   | prbs2                              | manager | line_625_store     |               |                                                                                                               |                    |

| 2    | line_sync                                   | prbs2                              | manager | vcw_update         | pab_update    |                                                                                                               |                    |

| 3    | line_sync                                   | prbs2                              | manager | dcw1_update        | dcw2_update   |                                                                                                               |                    |

| 4    | line_sync                                   | prbs2                              | manager | dcw3_update        | dcw4_update   |                                                                                                               |                    |

| 5    | line_sync                                   | prbs2                              | manager | cw_conversion      |               |                                                                                                               |                    |

| 6    | line_sync                                   | prbs2                              | manager | psc_update         |               |                                                                                                               |                    |

| 7    | line_sync                                   | prbs2                              | manager | prbs_init          | prbs2_init    | enable_imbus                                                                                                  | enable_packet_sync |

| 8    | line_sync<br> <br> <br> <br> <br> <br> <br> | prbs2<br> <br> <br> <br> <br> <br> |         | packet acquisition |               | packet_sync<br>packet_read<br>pae_comparator<br>buffer_manager<br>packet_link<br>packet_store<br>packet_error |                    |

| 622  | line_sync                                   | prbs2                              | manager | pae_low_update     | disable_imbus | disable_packet_sync                                                                                           |                    |

| 623  | line_sync                                   | prbs2                              | manager | pae_high_update    |               |                                                                                                               |                    |

| 624  | line_sync                                   | prbs2                              | manager | mode_update        | coeff_update  |                                                                                                               |                    |

| 625  | line_<br>sync                               |                                    |         | line_625_sync      |               |                                                                                                               |                    |

#### Fig. 8–1: Task manager

#### 8.2. IM Bus Interface

The INTERMETALL Bus (IM Bus for short) was designed to control the DIGIT 2000 ICs by the CCU Central Control Unit. Via this bus the CCU can write data to the ICs or read data from them. This means the CCU acts as a master, whereas all controlled ICs have purely slave status.

The IM bus consists of three lines for the signals Ident (ID), Clock (CL) and Data (D). The clock frequency range is 50 Hz to 1 MHz. Ident and clock are unidirectional from the CCU to the slave ICs, Data is bidirectional. Bidirectionality is achieved by using open–drain outputs. The 2.5 ... 1 kOhm pull–up resistor common to all outputs must be connected externally.

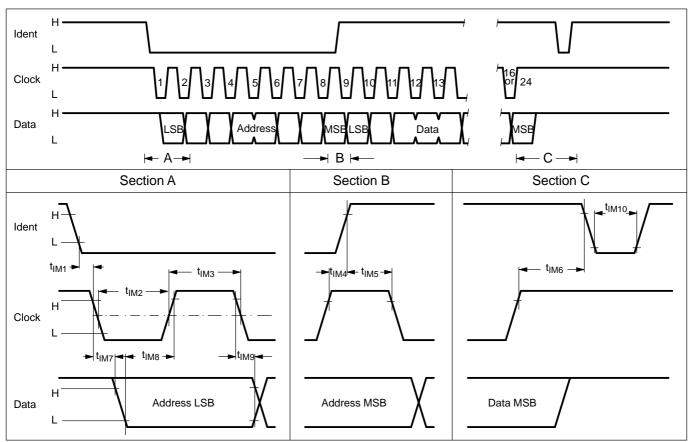

The timing of a complete IM Bus transaction is shown in Fig. 9–12. In the non-operative state the signals of all three bus lines are High. To start a transaction the CCU sets the ID signal to Low level, indicating an address transmission, and sets the CL signal to Low level, as well as to switch the first bit on the Data line. Then eight address bits are transmitted, beginning with the LSB. Data takeover in the slave ICs occurs at the positive edge of the clock signal. At the end of the address byte the ID signal switches to High, initiating the address comparison in the slave circuits. In the addressed slave, the IM bus interface switches over to Data read or write, because these functions are correlated to the address. Also controlled by the address the CCU now transmits eight or sixteen clock pulses, and accordingly one or two bytes of data are written into the addressed IC or read out from it, beginning with the LSB.

The completion of the bus transaction is signalled by a short Low state pulse of the ID signal. This initiates the storing of the transferred data.

For future software compatibility, the CCU must write a zero into all bits not used at present. Reading undefined or unused bits, the CCU must adopt "don't" care behavior.

#### 8.2.1. IM Bus Addresses and Instructions

On the DMA 2275 or DMA 2286 the IM bus registers 5-10 are used to transfer data to and from the acquisition DRAM. This is done by subaddressing. Each data transfer is preceded by the transfer of the extension address highbyte and the read or write address lowbyte. The subsequent data is written to or read from the DRAM according to the preceding address command. The DRAM address is then incremented internally to prepare for the next data transfer (auto address increment). The status register is used to synchronize the data transfer between CCU and the descrambler in terms of handshaking. For this purpose the CCU has to read the busy bit and has to wait until this bit is cleared. Reading the busy bit can be done with a normal IM bus read access which takes 16 IM Bus clock cycles or by checking the IM Bus busy signal at pin 47 which delivers the busy bit as a physical signal.

The same IM Bus registers can be used to transfer data to and from the FP internal memory. Loading the write address register (6) with an 8 bit FP address and setting bit 10 at the same time writes the 12 bit content of the extension address register (5) into the FP RAM. Loading the read address register (7) with an 8 bit FP address and setting bit 10 at the same time starts transfer of 12 bit FP data into the data (8) and status (9) register. The 8 LSBs are copied into the data register in normal order and the 4 MSBs are copied into the extension data of the status register but in reversed order.

The DMA 2286 carries a second set of IM Bus registers, which are used to control the sound processing. These IM Bus registers are a copy of the registers of the DMA 2281 with identical functions and addresses (194–198, 203–206 and 208–210). The CCU selects the IM Bus registers of the descrambler chip by writing '1' into the chip select register 198. This disables all parallel IM Bus registers of the decoder chip except the chip select register. Writing '0' into the chip select register disables all IM Bus registers of the descrambler chip select register disables all IM Bus registers of the descrambler chip select register disables all IM Bus registers of the descrambler chip select register disables all IM Bus registers of the descrambler chip, except the subaddressing registers 5–10 and the chip select register 198.

## Table 8-1: Data transfer between CCU and DMA 2275/2286

| Addr. | Bit<br>No. | MSB                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |                    |                                 |                               |                         |                         |                                          |          |                    |                |                      |                        |                        | LSB                     |

|-------|------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|---------------------------------|-------------------------------|-------------------------|-------------------------|------------------------------------------|----------|--------------------|----------------|----------------------|------------------------|------------------------|-------------------------|

| No.   | Direct.    | 15                            | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13                      | 12                 | 11                              | 10                            | 9                       | 8                       | 7                                        | 6        | 5                  | 4              | 3                    | 2                      | 1                      | 0                       |

| 5     | W          |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |                    |                                 |                               |                         | ļ                       | EXA<br>Extension Address                 |          |                    |                |                      |                        |                        |                         |

| 6     | W          |                               | $\sim$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\searrow$              | $\sim$             |                                 |                               |                         |                         |                                          |          |                    | Write A        | RA<br>Address<br>0   |                        |                        |                         |

| 7     | w          |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |                    |                                 |                               |                         |                         |                                          |          |                    | Read A         | DA<br>Address<br>0   |                        |                        |                         |