# **Tri-State Logic**

## DM7551/DM8551 tri-state quad-D flip flop

#### general description

The DM7551/DM8551 is a tri-state logic devicewhich provides four D-type flip flops in one package which operate synchronously from a common clock. Features of the device are:

- Series 54/74 compatible

- 23 ns typical propagation delay

- 250 mW typical power dissipation

- Outputs directly connectable for bus-line operation

- A "do-nothing" state accomplished without gating the clock

- Simple disable encoding

A unique three-state output allows the device to be used in bus-organized systems. The outputs can be directly wired to outputs of other DM7551/ DM8551's without encountering the problems normally met with "collector-ORing" TTL circuits. This is accomplished by gating the normally low impedance logical "1" or logical "0" output into a high impedance state.

(Continued on page 26)

### absolute maximum ratings (Note 1)

| Supply Voltage                        | 7V              |

|---------------------------------------|-----------------|

| Input Voltage                         | 5.5V            |

| Output Voltage                        | 5.5V            |

| Storage Temperature Range             | -65°C to +150°C |

| Operating Temperature Range DM7551    | -55°C to +125°C |

| DM8551                                | 0°C to +70°C    |

| Lead Temperature (Soldering, 10 sec)  | 300°C           |

| Time that 2 bus-connected devices may |                 |

| be in opposite low impedance states.  |                 |

simultaneously

Indefinitely

#### electrical characteristics (Note 2)

| PARAMETERS                                                                                             |                  | CONDITIONS                                        |                                                          | MIN | ТҮР  | MAX     | UNITS    |  |  |

|--------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|----------------------------------------------------------|-----|------|---------|----------|--|--|

| Logical "1" Input Voltage                                                                              | DM7551<br>DM8551 | V <sub>CC</sub> = 4.5V<br>V <sub>CC</sub> = 4.75V |                                                          | 2.0 |      |         | v        |  |  |

| Logical "0" Input Voltage                                                                              | DM7551<br>DM8551 | V <sub>CC</sub> = 4.5V<br>V <sub>CC</sub> = 4.75V |                                                          |     |      | 0.80    | v        |  |  |

| Logical "1" Output Voltage                                                                             | DM7551<br>DM8551 | V <sub>CC</sub> = 4.5V<br>V <sub>CC</sub> = 4.75V | I <sub>OUT</sub> = -2.0 mA<br>I <sub>OUT</sub> = -5.2 mA | 2.4 | 3.3  |         | v        |  |  |

| Logical "0" Output Voltage                                                                             | DM7551<br>DM8551 | $V_{CC} = 4.5V$<br>$V_{CC} = 4.75V$               | I <sub>OUT</sub> = 16 mA                                 |     | 0.2  | 0.40    | v        |  |  |

| Logical "0" Input Current                                                                              | DM7551<br>DM8551 | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5.25V | V <sub>IN</sub> = 0.40V                                  |     | -1.0 | -1.6    | mA       |  |  |

| Logical "1" Input Current                                                                              | DM7551<br>DM8551 | $V_{CC} = 5.25V$<br>$V_{CC} = 5.25V$              | V <sub>IN</sub> = 2.4V<br>V <sub>IN</sub> = 5.5V         |     |      | 40<br>1 | μA<br>mA |  |  |

| Output Current                                                                                         | DM7551           | V <sub>CC</sub> = 5.5V                            | V <sub>0</sub> = 2.4V                                    |     |      | 40      | μA       |  |  |

| In High Impedance State                                                                                | DM8551           | V <sub>CC</sub> = 5.25V                           | $V_0 = 0.4V$                                             |     |      | -40     | μA       |  |  |

| Supply Current                                                                                         | DM7551<br>DM8551 | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5,25V |                                                          |     | 50   | 72      | mA       |  |  |

| Output Short Current<br>(Note 3)                                                                       | DM7551<br>DM8551 | $V_{CC} = 5.5V$<br>$V_{CC} = 5.25V$               | V <sub>OUT</sub> = 0.0V                                  | -30 |      | -70     | mA       |  |  |

| Maximum Clock Frequency                                                                                | 4                | V <sub>CC</sub> = 5.0V<br>C <sub>L</sub> = 50 pF  | T <sub>A</sub> = 25°C                                    |     | 25   |         | MHz      |  |  |

| Propagation Delay from Clock<br>to Logical ''0'', t <sub>pd0</sub>                                     |                  | V <sub>CC</sub> = 5.0V<br>C <sub>L</sub> = 50 pF  | T <sub>A</sub> = 25°C                                    | 11  | 20   | 31      | ns       |  |  |

| Propagation Delay from Clock<br>to Logical "1", t <sub>pd1</sub>                                       |                  | V <sub>CC</sub> = 5.0V<br>C <sub>L</sub> = 50 pF  | T <sub>A</sub> = 25°C                                    | 11  | 27   | 43      | ns       |  |  |

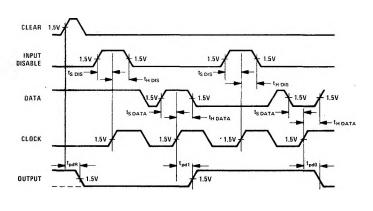

| Input Data Setup Time, t <sub>S DAT</sub>                                                              | A                | V <sub>CC</sub> = 5.0V                            | T <sub>A</sub> = 25°C                                    |     | 3    | 10      | ns       |  |  |

| Input Data Hold Time, t <sub>H DAT</sub> ,                                                             | A                | V <sub>CC</sub> = 5.0V                            | $T_A = 25^{\circ}C$                                      |     | 4    | 10      | ns       |  |  |

| Input Disable Setup Time, t <sub>S D</sub>                                                             | IS               | V <sub>CC</sub> = 5.0V                            | T <sub>A</sub> = 25°C                                    |     | 10   | 17      | ns       |  |  |

| Input Disable Hold Time, t <sub>H Di</sub>                                                             | s                | V <sub>cc</sub> = 5.0V                            | $T_A = 25^{\circ}C$                                      |     | -4   | 2       | ns       |  |  |

| Delay from "Output Disable" t<br>Impedance State (from Logical<br>Level), t <sub>1 H</sub>             |                  | V <sub>CC</sub> = 5.0V                            | $T_A = 25^{\circ}C$                                      | 3   | 5    | 30      | ns       |  |  |

| Delay from ''Output Disable'' t<br>Impedance State (from Logical<br>Level), t <sub>OH</sub>            | U U              | V <sub>CC</sub> = 5.0V                            | T <sub>A</sub> = 25°C                                    | 3   | 11   | 30      | ns       |  |  |

| Delay from "Output Disable" t<br>Logical "1" Level (from High<br>Impedance State), t <sub>H 1</sub>    | 0                | V <sub>CC</sub> = 5.0V                            | T <sub>A</sub> = 25°C                                    | 7   | 16   | 30      | ns       |  |  |

| Delay from ''Output Disable'' t<br>Logical ''0'' Level (from High<br>Impedance State), t <sub>HO</sub> | 0                | V <sub>CC</sub> = 5.0V                            | T <sub>A</sub> = 25°C                                    | 7   | 21   | 30      | ns       |  |  |

| Propagation Delay from Clear<br>to Output, t <sub>pd R</sub>                                           |                  | V <sub>CC</sub> = 5.0V                            | T <sub>A</sub> = 25°C                                    |     | 18   | 27      | ns       |  |  |

Note 1: Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range", they are not meant to imply operating conditions.

Note 2: Unless otherwise specified the min-max limits across the -55°C to +125°C temperature range for the DM7551 and across the 0°C to 70°C temperature range for the DM8551. All typicals are given for  $V_{CC} = 5.0V$  and  $T_A = 25°C$ .

Note 3: Only 1 output at a time should be shorted.

DM7551/DM8551

### general description (con't)

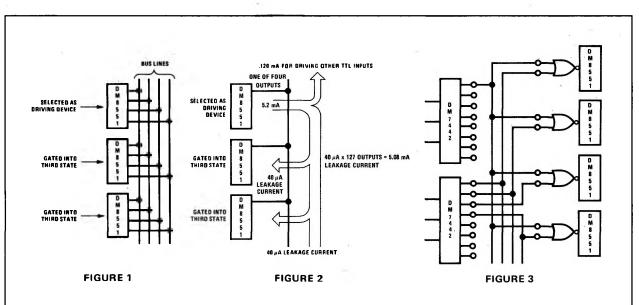

The high impedance state occurs on all outputs of all devices except the four outputs of the one device selected (Figure 1). The result is that the selected device has a normal TTL low impedance output providing good capacitive drive capability and waveform integrity especially during the transition from a logical "0" to a logical "1". The other outputs are all in the "third-state" and take only a small amount of leakage current from the driving outputs. Since the logical "1" output current of the selected device is 13 times that of a normal Series 54/74 output (5.2 mA vs 400  $\mu$ A), the output is easily able to supply that leakage current to as many as 127 connected devices and still retain enough drive for a full Series 54/74 fan-out of 3 at the end of the bus line (Figure 2).

A two-input NOR gate facilitates selection of the driving device through the use of only two octal decoders for as many as 64 DM7551/DM8551's (Figure 3).

A problem inherent in conventional D-type flip flops is that it is impossible to code the data input in such a way as to cause the flip flop to remain in its present state when clocked. Because flexibility is not as great as with a J-K flip flop (and its J=0, K=0 state), to keep a D-type flip flop in i\*s present state it is usually necessary to gate the clock, which increases the danger of false-clocking. The DM7551/DM8551 contains a gated input disable which does not disrupt clocking, but rather recirculates information from the Q output to the D input. In this manner the flip flop does not change state and the possibility of false-clocking is eliminated.

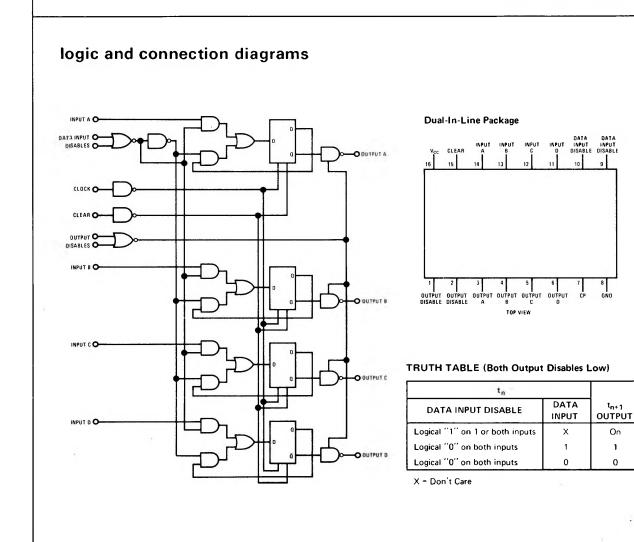

The following logic levels control the device:

- Clocking occurs on the positive-going transition.

- Clearing is enabled by taking the input to a Logical "1" level.

- Outputs are placed in the "third-state" if either of the two Output Disable inputs is taken to a Logical "1" level.

- The flip flops will remain in their previous state when clocked so long as either of the two Data Input Disable inputs is taken to a Logical "1" level.

The DM7551/DM8551 is completely compatible with other Series 54/74 devices.