# TTL MSI

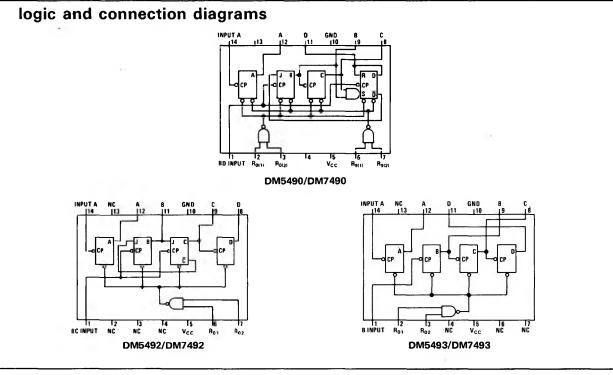

# DM5490/DM7490 (SN5490/SN7490)decade counter DM5492/DM7492 (SN5492/SN7492) divide-by-twelve counter DM5493/DM7493 (SN5493/SN7493) four-bit binary counter

## general description

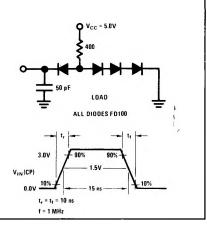

These TTL (Transistor-Transistor-Logic) monolithic counters are capable of counting pulses at a guaranteed frequency of 20 MHz. Gating is provided to reset the counters to the more popular states. Characteristics include high speed at moderate power dissipation, high noise immunity, and minimal variation in performance over temperature. These circuits are completely compatible with other series 54/74 devices.

To provide greater flexibility, the counters may be used in any of the modes as follows:

## DM5490/DM7490

- 1. BCD decade counter-connect the A output to the BD input. This is the normal mode of operation.

- 2. Symmetrical divide-by-ten operation-connect the D output to the A input. When pulses are then applied to the BD input, a symmetrical waveform one tenth of the applied frequency will appear at the A output.

- 3. Divide-by-five operation—if no external connections are made a frequency division of five will result between the BD input and the D output. This allows the flip flop A to be used to divide-by-two if desired.

## DM5492/DM7492

- 1. When used as a divide-by-twelve counter output A is connected to the BC input. In this mode outputs A, C, and D provide divisions by 2, 6, and 12 respectively.

- 2. When the connection is not made between A and BC, and when an input frequency is applied to the BC input, a frequency division of 3 and 6 results on the C and D outputs respectively. In this mode the A flip flop may be used independently except for the common reset input.

## DM5493/DM7493

- When used as a four-bit binary counter, output A is connected to the B input. In this mode outputs A, B, C, and D provide divisions by 2, 4, 8, and 16 respectively.

- 2. When the connection is not made between A and B and when an input frequency is applied to the B input, a frequency division of 2, 4 and 8 results on the B, C, and D outputs respectively. In this mode the A flip flop may be used independently except for the common reset input.

# absolute maximum ratings

| Supply Voltage                       | 7V                             |

|--------------------------------------|--------------------------------|

| Input Voltage                        | 5.5V                           |

| Operating Temperature Range          |                                |

| DM5490, DM5492, DM5493               | –55°C to +125°C                |

| DM7490, DM7492, DM7493               | $0^{\circ}C$ to $+70^{\circ}C$ |

| Storage Temperature Range            | -65°C to +150°C                |

| Lead Temperature (soldering, 10 sec) | 300°C                          |

# electrical characteristics (Note 1)

.

| PARAMETER                                                                          |                                  | CONE                                              | MIN                                             | ΤΥΡ      | MAX            | UNITS          |                |

|------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------|-------------------------------------------------|----------|----------------|----------------|----------------|

| Input Diode Clamp Voltage                                                          |                                  | V <sub>CC</sub> = 5.0V,<br>T <sub>A</sub> = 25°C  | I <sub>OUT</sub> = -12 mA                       |          | -1.0           | -1.5           | mA             |

| Logical "1" Input Voltage                                                          | DM5490, 92, 93<br>DM7490, 92, 93 | V <sub>CC</sub> = 4.5V<br>V <sub>CC</sub> = 4.75V |                                                 | 2.0      |                |                | V aya          |

| Logical "0" Input Voltage                                                          | DM5490, 92 ,93<br>DM7490, 92, 93 | V <sub>CC</sub> = 4.5V<br>V <sub>CC</sub> = 4.75V |                                                 |          |                | .8             | v ·            |

| Logical ''1'' Output Voltage                                                       | DM5490, 92, 93<br>DM7490, 92, 93 | V <sub>CC</sub> = 4.5V<br>V <sub>CC</sub> = 4.75V | ί <sub>ουτ</sub> = -400 μΑ                      | 2.4      |                |                | v              |

| Logical ''0'' Output Voltage                                                       | DM5490, 92, 93<br>DM7490, 92, 93 | V <sub>CC</sub> = 4.5V<br>V <sub>CC</sub> = 4.75V | I <sub>OUT</sub> = 16 mA                        |          | .2             | .4             | v              |

| Logical "1" Input Current                                                          | DM5490, 92, 93<br>DM7490, 92, 93 | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5.25V | V <sub>IN</sub> = 5.5V                          |          |                | 1              | mA             |

| Output Short Circuit Current                                                       | DM5490, 92, 93<br>DM7490, 92, 93 | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5.25V | (Note 2)                                        | 20<br>18 |                | 55<br>55       | mA             |

| DM5490/DM7490                                                                      |                                  |                                                   |                                                 |          |                |                | 19             |

| Logical "1" Input Current                                                          | DM5490<br>DM7490                 | V <sub>cc</sub> = 5.5V<br>V <sub>cc</sub> = 5.25V | V <sub>IN</sub> = 2.4V                          |          |                |                |                |

| R <sub>0(1)</sub> , R <sub>0(2)</sub> , R <sub>9(1)</sub> , R <sub>9(2)</sub><br>A |                                  |                                                   |                                                 |          |                | 40<br>80       | μΑ<br>μΑ       |

| BD                                                                                 |                                  |                                                   |                                                 |          |                | 160            | μΑ             |

| Logical ''0'' Input Current                                                        | DM5490<br>DM7490                 | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> 5.25V   | $V_{IN} = .4V$                                  |          |                |                |                |

| R <sub>0(1)</sub> , R <sub>0(2)</sub> , R <sub>9(1)</sub> , R <sub>9(2)</sub><br>A |                                  |                                                   |                                                 |          |                | 1.6<br>3.2     | mA<br>mA       |

| BD                                                                                 |                                  |                                                   |                                                 |          |                | 6.4            | mA             |

| Supply Current                                                                     | DM5490<br>DM7490                 | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5.25V |                                                 |          | 32             | 45             | mA             |

| Maximum Input Frequency                                                            |                                  | V <sub>CC</sub> = 5.0V,<br>F.O. = 10,             | T <sub>A</sub> = 25°C<br>C <sub>O</sub> = 50 pF | 20       | 32             |                | MHz            |

| Propagation Delay Time to a<br>Logical "1" Level From                              | A<br>B<br>C<br>D                 | F.O. = 10,<br>C <sub>OUT</sub> = 50 pF,           | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C |          | 16<br>35<br>50 | 35<br>60<br>80 | ns<br>ns<br>ns |

| Input to Output                                                                    | D                                | All Outputs                                       |                                                 |          | 35             | 60             | ns             |

| Propagation Delay Time to a                                                        | AB                               | F.O. = 10,<br>C <sub>OUT</sub> = 50 pF,           | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C |          | 19<br>35       | 35<br>60       | ns<br>ns       |

| Input to Output                                                                    | BCD                              | All Outputs                                       |                                                 |          | 50<br>35       | 80<br>60       | ns<br>ns       |

| Minimum Allowable Clock<br>Pulse Width (Note 3)                                    | n it.                            | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C   |                                                 |          | 8              | 15             | ns             |

| DM5492/DM7492                                                                      |                                  |                                                   |                                                 |          | -              |                |                |

| Logical "1" Input Current                                                          | DM5492<br>DM7492                 | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5.25V | V <sub>IN</sub> = 2.4V                          |          |                |                |                |

| R <sub>0(1)</sub> , R <sub>0(2)</sub><br>A                                         |                                  | -                                                 |                                                 |          |                | 40<br>80       | μΑ<br>μΑ       |

| BC                                                                                 |                                  |                                                   |                                                 |          |                | 160            | μA             |

DM5490/DM7490,DM5492/DM7492,DM5493/DM7493

| PARAMETER CONDITION DM5492/DM7492 (Continued)   |                  | RAMETER CONDITIONS                                |                                                 |    | ТҮР      | MAX          | UNITS    |

|-------------------------------------------------|------------------|---------------------------------------------------|-------------------------------------------------|----|----------|--------------|----------|

|                                                 |                  |                                                   |                                                 |    |          |              |          |

| Logical "0" Input Current                       | DM5492<br>DM7492 | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5.25V | V <sub>IN</sub> = .4V                           |    |          |              |          |

| R <sub>0(1)</sub> , R <sub>0(2)</sub>           |                  |                                                   |                                                 |    |          | 1.6          | mA       |

| Α                                               |                  |                                                   |                                                 |    |          | 3.2          | mA       |

| BC                                              |                  |                                                   |                                                 |    |          | 6.4          | mA       |

| Supply Current                                  | DM5492<br>DM7492 | V <sub>cc</sub> = 5.5V<br>V <sub>cc</sub> = 5.25V | V <sub>IN</sub> (R <sub>0</sub> ) = 4.5V        |    | 30       | 43           | mA       |

| Maximum Input Frequency                         |                  | V <sub>CC</sub> = 5.0V,<br>F.O. = 10,             | T <sub>A</sub> = 25°C<br>C <sub>O</sub> = 50 pF | 20 | 32       |              | MHz      |

|                                                 | Α                |                                                   |                                                 |    | 16       | 35           | ns       |

| Propagation Delay Time to a                     | B                | F.O. = 10,                                        | $V_{cc} = 5.0V$                                 |    | 35       | 60           | ns       |

| Logical "1" Level From                          | ī                | С <sub>ОUT</sub> = 50 pF,                         | T <sub>A</sub> = 25°C                           |    | 35       | 60           | ns       |

| Input A to Output                               |                  | All Outputs                                       |                                                 |    | 50       | 80           | ns       |

| 1                                               |                  |                                                   |                                                 |    | 19       | 35           | -        |

| Propagation Delay Time to a                     |                  | F.O. = 10,                                        |                                                 |    | 35       | - 35<br>- 60 | ns       |

| Logical "0" Level From                          | č                | C <sub>OUT</sub> = 50 pF,                         | T <sub>A</sub> = 25°C                           |    | 35       | 60           | ns       |

| Input A to Output                               | D D              | All Outputs                                       |                                                 |    | 35<br>50 | 80           | ns<br>ns |

| Minimum Allowable Clash                         | 0                |                                                   |                                                 |    | 30       | 00           | 113      |

| Minimum Allowable Clock<br>Pulse Width (Note 3) |                  | V <sub>CC</sub> = 5.0V<br>T <sub>A</sub> = 25°C   |                                                 |    | 8        | 15           | ns       |

| DM5493/DM7493                                   |                  |                                                   |                                                 |    |          |              |          |

| Logical "1" Input Current                       | DM5493           | V <sub>CC</sub> = 5.5V                            | V <sub>IN</sub> = 2.4V                          |    |          |              | -        |

| Logical i input coment                          | DM7493           | V <sub>CC</sub> = 5.25V                           | V IN - 2.4 V                                    |    |          |              |          |

| R <sub>0(1)</sub> , R <sub>0(2)</sub>           |                  |                                                   |                                                 |    |          | 40           | μΑ       |

| А, В                                            |                  |                                                   |                                                 |    |          | 80           | μA       |

| Logical "0" Input Current                       | DM5493           | V <sub>cc</sub> = 5.5V<br>V <sub>cc</sub> = 5.25V | V <sub>IN</sub> = .4V                           |    |          |              |          |

| Logical o input current                         | DM7493           | V <sub>CC</sub> = 5.25V                           | V <sub>IN</sub> 4V                              |    |          |              |          |

| R <sub>0(1)</sub> , R <sub>0(2)</sub>           |                  |                                                   |                                                 |    |          | 1.6          | mA       |

| А, В                                            |                  |                                                   |                                                 |    |          | 3.2          | mA       |

| Supply Current                                  | DM5493           | V <sub>CC</sub> = 5.5V                            |                                                 |    | 20       | 42           |          |

| Supply Current                                  | DM7493           | V <sub>CC</sub> = 5.25V                           |                                                 |    | 30       | 43           | mA       |

| Maximum Input Frequency                         |                  | V <sub>CC</sub> = 5.0V,<br>F.O. = 10,             | T <sub>A</sub> = 25°C<br>C <sub>O</sub> = 50 pF | 20 | 32       |              | MHz      |

| Propagation Datas Time                          | A                |                                                   |                                                 |    | 16       | 35           | ns       |

| Propagation Delay Time to a                     | в                | F.O. = 10,                                        | $v_{cc} = 5.0V$                                 |    | 35       | 60           | ns       |

| Logical "1" Level From                          | CID              | $C_{OUT} = 50  pF,$                               | $I_{A} = 25^{-}C$                               |    | 50       | 80           | ns       |

| Input to Output                                 | D                | All Outputs                                       |                                                 |    | 65       | 100          | ns       |

|                                                 | A                |                                                   |                                                 |    | 19       | 35           | ns       |

| Propagation Delay Time to a                     | B                | F.O. = 10,                                        | $V_{cc} = 5.0V$                                 |    | 35       | 60           | ns       |

| Logical "O" Level From                          | c                | С <sub>ОUT</sub> = 50 pF,                         | T <sub>A</sub> = 25°C                           |    | 50       | 80           | ns       |

| Input to Output                                 | D                | All Outputs                                       |                                                 |    | 64       | 100          | ns       |

| Minimum Allowable Clock                         |                  | V <sub>cc</sub> = 5.0V                            |                                                 |    |          |              |          |

| Pulse Width (Note 3)                            |                  | $T_A = 25^{\circ}C$                               |                                                 |    | 8        | 15           | ns       |

Note 1: Min/max limits apply across the guaranteed operating temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C for the DM5490, DM5492 and DM5493 and 0°C to 70°C for the DM7490, DM7492 and DM7493 unless otherwise specified. All typicals are given for V<sub>CC</sub> = 5.0V and T<sub>A</sub> = 25 C.

Note 2: Only one output may be shorted at a time.

Note 3: The flip flop will always recognize a 15 ns pulse

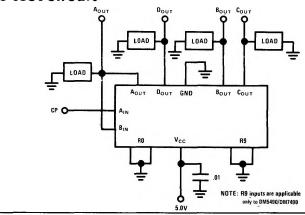

# ac test circuit

DM5490/DM7490,DM5492/DM7492,DM5493/DM7493

83

## **BCD** count sequence

#### DM5490/DM7490

| COUNT | С., | OUT | PUT |   |

|-------|-----|-----|-----|---|

|       | D   | С   | В   | Α |

| 0     | 0   | 0   | 0   | 0 |

| 1     | 0   | 0   | 0   | 1 |

| 2     | 0   | 0   | 1   | 0 |

| 3     | 0   | 0   | 1   | 1 |

| 4     | 0   | - 1 | 0   | 0 |

| 5     | .0  | 1   | 0   | 1 |

| 6     | 0   | 1   | 1   | 0 |

| 7     | 0   | 1   | 1   | 1 |

| 8     | 1   | 0   | 0   | Q |

| 9     | 1   | 0   | 0   | 1 |

#### count sequence

#### DM5492/DM7492

| COUNT | OUTPUT |     |   |     |  |

|-------|--------|-----|---|-----|--|

| 100   | D .    | С   | В | А   |  |

| 0     | 0      | 0   | 0 | 0   |  |

|       | 0      | 0   | 0 | 1   |  |

| 2     | 0      | 0   | 1 | 0   |  |

| 3     | 0      | 0   | 1 | 1   |  |

| 4     | 0      | 1   | 0 | 0   |  |

| 5     | 0      | 1   | 0 | 1   |  |

| 6     | 1      | 0   | 0 | 0   |  |

| 7     | 1      | 0   | 0 | 1 * |  |

| 8     | 1      | 0   | 1 | 0   |  |

| 9     | 1      | 0   | 1 | 1   |  |

| 10    | 1.+    | 1   | 0 | 0   |  |

| 11    | 1      | ្វ1 | 0 | 1   |  |

#### DM5493/DM7493

| COUNT                 |      | OU | TPUT    |     |

|-----------------------|------|----|---------|-----|

| + 1                   | D    | С  | В       | A   |

| 0                     | 0    | 0  | 0       | 0   |

| 1                     | 0    | 0  | 0       | 1   |

|                       | 0    | 0  | 1       | 0   |

| 3                     | 0    | 0  | 1       | 1   |

| 2<br>3<br>4<br>5<br>6 | 0    | 1  | 0       | 0   |

| 5                     | .0   | 1  | 0       | 1   |

|                       | 0    | 1  | 1       | 0   |

| 7                     | 0    | 1  | 1       | 1   |

| 8                     | 1    | 0  | 0       | 0   |

| 9                     | a. 1 | 0  | · · · 0 | 1   |

| 10                    | 1    | 0  | 1       | 0   |

| 11                    | 1,   | 0  | 1       | × 1 |

| 12                    | 1.   | 1  | 0       | 0   |

| 13                    | 1 0  | 1  | 0       | 1   |

| 14                    | -1   | 1  | 1       | 0   |

| 15                    | 1    | 1  | 1       | 1 * |

#### **RESET OPERATION**

To reset the counter to the BCD count of zero, both Reset 0 inputs must be at logical "1" levels while at least one Reset 9 input is at a logical "0" level.

To reset the counter to the BCD count of nine, both Reset 9 inputs must be at logical "1" levels; while at least one Reset 0 input is at a logical "0".

#### Notes:

- 1. Counting occurs on the negative-going edge of the input pulse.

- 2. At least one of the Reset 0 inputs and at least one of the Reset 9 inputs must be at a logical "0" for proper counting.

- 3. For  $\div$  10 counting, connect the A output to the BD input.

#### **RESET OPERATION**

To reset the counter to the count of zero, both Reset 0 inputs must be at logical "1" levels.

Notes:

- 1. Counting occurs on the negative-going edge of the input pulse.

- 2. At least one of the Reset 0 inputs must be at a logical "0" for proper counting.

- 3. For ÷12 counting, connect the A output to the BC input.

#### **RESET OPERATION**

To reset the counter to the count of zero, both Reset 0 inputs must be at logical "1" levels.

#### Notes:

- 1. Counting occurs on the negative-going edge of the input pulse.

- 2. At least one of the Reset 0 inputs must be at a logical "0" for proper counting.

- 3. For ÷16 counting, connect the A output to the B input.