# Gates, Series 54/74

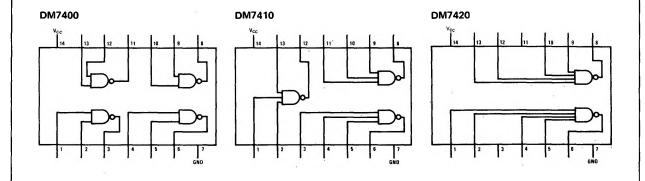

DM7400 (SN7400) quadruple two-input NAND gate DM7410 (SN7410) triple three-input NAND gate DM7420 (SN7420) dual four-input NAND gate

### general description

Employing TTL (Transistor-Transistor-Logic) to achieve high speed at moderate power dissipation, these gates provide the basic functions used in the implementation of digital integrated circuit systems. Characteristics of the circuits include high noise immunity, low output impedance, good capacitive drive capability, and minimal variation in switching times with temperature. The gates are compatible with and interchangeable with Series 74 equivalent.

#### Key features include:

| Typical Noi | se Imm | iunity   |     | 1V |

|-------------|--------|----------|-----|----|

| Guaranteed  | Noise  | Immunity | 400 | mV |

| Fan Out     |        |          |     | 10 |

Allowable Power Supply Variation

4.75V to 5.25V

Average Propagation DelayAverage Power Dissipation10 mW per gate

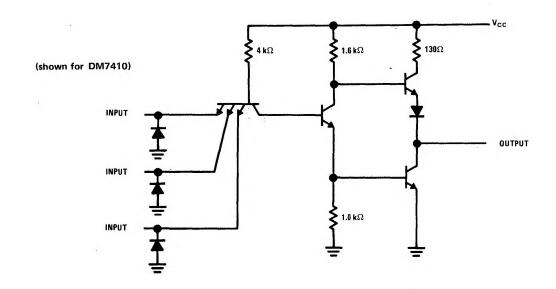

## schematic and connection diagrams

# absolute maximum ratings

Vcc 7.0V Input Voltage 5.5V Operating Temperature Range 0°C to +70°C Storage Temperature Range -65°C to +150°C Fan-Out 10 Lead Temperature (Soldering, 10 sec) 300°C

# electrical characteristics (Note 1)

| PARAMETER                                               | PARAMETER CONDITIONS                                      |          | TYP | MAX  | UNITS |

|---------------------------------------------------------|-----------------------------------------------------------|----------|-----|------|-------|

| Input Diode Clamp Voltage                               | $V_{CC} = 5.0V$ , $T_A = 25^{\circ}C$ , $I_{1N} = -12$ mA |          |     | -1.5 | V     |

| Logical "1"<br>Input Voltage                            | V <sub>CC</sub> = 4.75V                                   | 2.0      | = 0 |      | v     |

| Logical ''0''<br>Input Voltage                          | V <sub>CC</sub> = 4.75V                                   |          |     | 0.8  | v     |

| Logical "1"<br>Output Voltage                           | $V_{cc} = 4.75V$ $V_{IN} = 0.8V$ , $I_{OUT} = -40$        | 00μΑ 2.4 |     |      | V     |

| Logical ''0''<br>Output Voltage                         | $V_{cc} = 4.75 $ V $_{IN} = 2.0 $ V $_{IOUT} = 16 $ I     | mA       |     | 0.4  | v     |

| Logical "1"<br>Input Current                            | V <sub>CC</sub> = 5.25V V <sub>IN</sub> = 2.4V            |          |     | 40   | μΑ    |

| Logical "1"<br>Input Current                            | V <sub>CC</sub> = 5.25V V <sub>IN</sub> = 5.5V            |          |     | 1    | mA    |

| Logical ''0''<br>Input Current                          | V <sub>CC</sub> = 5.25V V <sub>IN</sub> = 0.4V            |          |     | -1.6 | mA    |

| Output Short<br>Circuit Current<br>(Note 2)             | V <sub>cc</sub> = 5.25V V <sub>IN</sub> = 0V              | -18      |     | -55  | mA    |

| Supply Current—<br>Logical "0"<br>(Note 3)              | V <sub>CC</sub> = 5.25V V <sub>IN</sub> = 5.0V            |          | 3   | 5.1  | mA    |

| Supply Current—<br>Logical "1"<br>(Note 3)              | V <sub>cc</sub> = 5.25V V <sub>IN</sub> = 0V              | ÷        | 1   | 1.8  | . mA  |

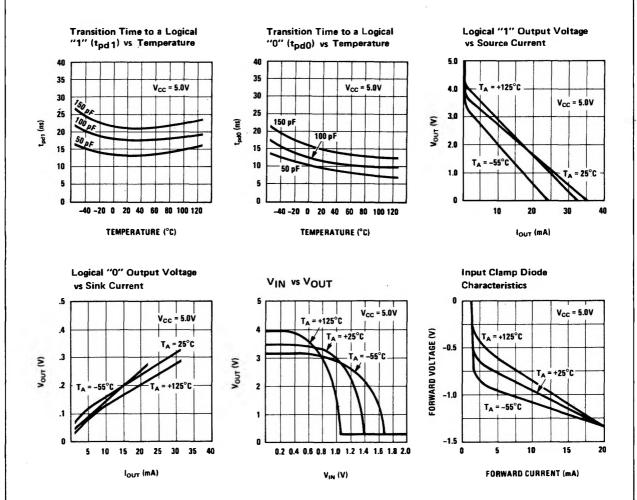

| Propagation Delay Time to Logical "0", t <sub>pd0</sub> | $V_{CC} = 5.0V$ , $T_A = 25^{\circ}C$ , $C = 50 pF$       |          | 8   | 15   | ns    |

| Propagation Delay Time to Logical "1", t <sub>pd1</sub> | $V_{CC} = 5.0V$ , $T_A = 25^{\circ}C$ , $C = 50 pF$       |          | 13  | 25   | ns    |

Note 1: Min/max limits apply across the guaranteed temperature range  $0^{\circ}C$  to  $70^{\circ}C$  unless otherwise specified. All typicals are given for  $V_{CC}$  = 5.0V and  $T_{A}$  = 25°C.

Note 2: Not more than 1 output should be shorted at a time.

Note 3: Each gate.

# typical performance characteristics

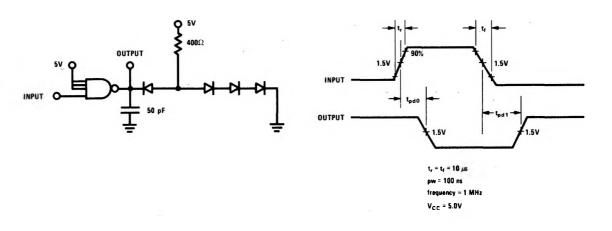

#### ac test circuit

# switching time waveform