# **Tri-State Logic**

# DM7230/DM8230 tri-state demultiplexer general description

The DM7230/DM8230 demultiplexer is another device in National's tri-state logic family.

Digital signals applied to two input lines can be routed to two-of-four output lines depending upon the logic on the Address inputs. Outputs can be directly connected to other similar outputs for use in bus-organized systems.

## features

- Series 54/74 compatible

- 20 ns propagation delay

- Data complement capability

- Very low output impedance-high drive capability

- Separate input disable controls

- High-impedance output state which allows many outputs to be connected to a common bus-line.

## mode of operation

#### COMPLEMENT AND DATA INPUTS

When Complement A is a logical "1", Data A will appear inverted at the output. When Complement A is a logical "0", Data A will appear non-inverted at the output.

This function is accomplished on the chip through the use of a two-input exclusive-OR gate with Complement A and Data A as the two inputs. Therefore, the A information that is routed to the

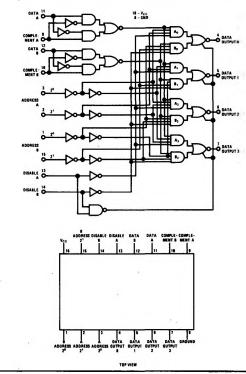

## logic and connection diagrams

outputs is actually (Complement A  $\oplus$  Data A). That this is the case may be verified by examining the logic diagram.

The two inputs of this exclusive-OR gate have identical characteristics, allowing the functions of these two inputs to be reversed. Also the propagation delay from either input to the output will be the same. This is also true for the Complement B and Data B inputs.

#### **ADDRESS INPUTS**

The Address A inputs select to which of the four outputs A information will be routed, The same is true for the Address B inputs and B information. If A and B information are both routed to the same output simultaneously, that output will be a logical "0" if either the A or B information is a logical "0". All outputs which are not selected for either A or B information will be in the logical "1" state.

#### DISABLE INPUTS

The Disable inputs are similar to higher order Address inputs in that when Disable A is a logical "1", A information is not routed to any output. All four outputs are nonselected for A information. The same is true for Disable B and B information. The Disable inputs have the additional feature that when both Disable A and Disable B are a logical "1" all outputs go to the High Impedance state. When multiple outputs are connected to a bus line, only one device at a time can be in the (Continued on Page 22)

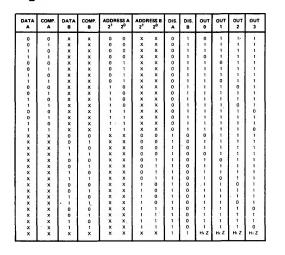

## logic table

### absolute maximum ratings

| Supply Voltage                       | 7V              |

|--------------------------------------|-----------------|

| Input Voltage                        | 5.5V            |

| Output Voltage                       | 5.5V            |

| Time that two bus connected          |                 |

| devices may be in opposite           |                 |

| low impedance states simultaneously. |                 |

| (5% duty cycle)                      | 10 msec         |

| Storage Temperature Range            | -65°C to +150°C |

| Operating Temperature Range          |                 |

| DM7230                               | -55°C to +125°C |

| DM8230                               | 0°C to +70°C    |

| Lead Temperature (Soldering, 10 sec) | 300°C           |

## electrical characteristics (Note 1)

| PARAMETER                                              |                    | CONDITIONS                                                                                              | MIN | TYP          | MAX                  | UNITS    |

|--------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------|-----|--------------|----------------------|----------|

| Logical "1" Input Voltage                              | DM7230             | V <sub>CC</sub> = 4.5V                                                                                  | 2.0 |              |                      | v        |

| Logical I Input voltage                                | DM8230             | V <sub>cc</sub> = 4.75V                                                                                 | 1.0 |              |                      |          |

|                                                        | DM7230             | V <sub>cc</sub> = 4.5V                                                                                  |     |              | 0.8                  | v        |

| Logical "0" Input Voltage                              | DM8230             | V <sub>cc</sub> = 4.75V                                                                                 |     |              | 0.8                  | v        |

|                                                        | DM7230             | Vec = 4.5V Jour = ~2 mA                                                                                 |     |              |                      | v        |

| Logical "1" Output Voltage                             | DM8230             | V <sub>CC</sub> = 4.5V, I <sub>OUT</sub> = -2 mA<br>V <sub>CC</sub> = 4.75V, I <sub>OUT</sub> = -5.2 mA | 2.4 | 3.5          |                      | v        |

|                                                        | DM7230             |                                                                                                         |     |              |                      |          |

| Logical "0" Output Voltage                             | DM8230             | $V_{CC} = 4.5V$<br>$V_{CC} = 4.75V$ I <sub>OUT</sub> = 16 mA                                            |     | 0.2          | 0.4                  | v        |

|                                                        |                    |                                                                                                         |     |              | 1                    |          |

| Logical "0" Input Current                              | DM7230             | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5.25V V <sub>IN</sub> = 0.4V                                |     |              |                      |          |

|                                                        | DM8230             |                                                                                                         |     |              |                      | mA       |

|                                                        |                    | Disable inputs                                                                                          |     | -2.0<br>-1.0 | -3.2<br>-1.6         | mA<br>mA |

|                                                        |                    | All other inputs                                                                                        |     | -1.0         | -1.0                 | ma       |

| Logical "1" Input Current                              | DM7230             | $V_{CC} = 5.5V$<br>$V_{CC} = 5.25V$ $V_{Hy} = 2.4V$                                                     |     |              | - 7 -                |          |

| Logica i input content                                 | DM8230             |                                                                                                         |     |              |                      |          |

|                                                        |                    | Disable inputs                                                                                          |     |              | 80                   | μΑ       |

|                                                        |                    | All other inputs                                                                                        |     |              | 40                   | μΑ       |

| Logical "1" Input Current                              | DM7230             | V <sub>CC</sub> = 5.5V<br>V <sub>CC</sub> = 5.25V                                                       |     |              | 1.0                  | mA       |

| Logical i input current                                | DM8230             | V <sub>cc</sub> = 5.25V                                                                                 |     |              | 1.0                  |          |

|                                                        | DM7230             | V <sub>cc</sub> = 5.5V V <sub>o</sub> = 2.4V                                                            |     |              | 40                   | μA       |

| Output Disable Current                                 | DM8230             | V <sub>CC</sub> = 5.25V V <sub>O</sub> = 0.4V                                                           |     |              | -40                  | μA       |

| Output Short Current                                   | DM7230             | V = 5.5V                                                                                                | -30 |              |                      |          |

| (Note 2)                                               | DM8230             | $V_{CC} = 5.5V$<br>$V_{CC} = 5.25V$ $V_{O} = 0.0V$                                                      | -28 |              | -70                  | mA       |

| (1010 2)                                               |                    |                                                                                                         |     |              |                      |          |

| Supply Current                                         | DM 7230<br>DM 8230 | $V_{CC} = 5.5V$<br>$V_{CC} = 5.25V$ $V_{IN} = 5.0V$                                                     |     | 48           | 75                   | mA       |

|                                                        | DM0230             |                                                                                                         |     |              |                      |          |

| Input Diode Clamp Voltage                              |                    | V <sub>CC</sub> = 5.0V, T <sub>A</sub> = 25°C                                                           |     |              | -1.5                 | v        |

|                                                        |                    | l <sub>iN</sub> = -12 mA                                                                                |     |              |                      |          |

|                                                        |                    | V <sub>CC</sub> = 5.0V, T <sub>A</sub> = 25°C                                                           |     |              |                      |          |

| Output Diode Clamp Voltag                              | e                  | I <sub>OUT</sub> = -12 mA                                                                               |     |              | -1.5                 | v        |

|                                                        |                    | i <sub>ουτ</sub> = +12 mA                                                                               |     |              | V <sub>cc</sub> +1.5 | v        |

|                                                        |                    | V <sub>CC</sub> = 5.0V, T <sub>A</sub> = 25°C                                                           |     |              |                      |          |

| Propagation Delay to Logica                            | n '' 1''           | C <sub>L</sub> = 50 pF                                                                                  |     |              |                      |          |

| from Data or Complement Input, tpd1                    |                    | Noninverting                                                                                            |     | 13           | 24                   | ns       |

|                                                        |                    | Inverting                                                                                               |     | 20           | 36                   | ns       |

|                                                        |                    | V <sub>CC</sub> = 5.0V, T <sub>A</sub> = 25°C                                                           |     |              |                      |          |

| Propagation Delay to Logica<br>from Data or Complement |                    | C <sub>L</sub> = 50 pF                                                                                  |     |              |                      |          |

| from Data or Complement                                | Cinput, Cpd0       | Noninverting or Inverting                                                                               |     | 18           | 26                   | ns       |

| Propagation Delay to Logica                            | it "1" from        | V <sub>CC</sub> = 5.0V, T <sub>A</sub> = 25°C                                                           |     |              |                      |          |

| Address Input, tod1 (Note                              |                    | $C_{L} = 50 \text{ pF}$                                                                                 |     | 20           | 36                   | ns       |

| Propagation Delay to Logica                            |                    | $V_{CC} = 5.0V, T_A = 25^{\circ}C$                                                                      |     | 10           |                      |          |

| Address Input, tpd0 (Note                              |                    | $V_{CC} = 5.0V, T_A = 25 C$<br>$C_1 = 50 \text{ pF}$                                                    |     | 20           | 30                   | ns       |

|                                                        |                    | -                                                                                                       |     |              |                      |          |

| Propagation Delay to Logica                            |                    | $V_{CC} = 5.0V, T_A = 25^{\circ}C$                                                                      |     | 13           | 25                   | ns       |

| Disable Input, t <sub>pd1</sub> (Note                  |                    | C <sub>L</sub> = 50 pF                                                                                  |     |              |                      |          |

| Propagation Delay to Logica                            |                    | $V_{CC} = 5.0V, T_{A} = 25^{\circ}C$                                                                    |     | 16           | 25                   | ns       |

| Disable Input, t <sub>pd0</sub> (Note                  | 4)                 | C <sub>L</sub> = 50 pF                                                                                  |     | "            |                      |          |

| Delay from Disable Input to                            | High               |                                                                                                         |     |              |                      |          |

| Impedance State (Note 5),                              |                    | V <sub>CC</sub> = 5.0V, T <sub>A</sub> = 25°C                                                           |     | 7            | 14                   | ns       |

|                                                        | ton                |                                                                                                         |     | 15           | 27                   | ns       |

| Delay from Disable Input to                            | Low                |                                                                                                         |     |              | -                    |          |

| Impedance State (Note 5),                              |                    | V <sub>CC</sub> = 5.0V, T <sub>A</sub> = 25°C<br>C <sub>L</sub> = 50 pF                                 |     | 15           | 23                   | ns       |

|                                                        | t <sub>HO</sub>    | i Ci=50 ph                                                                                              | 1   | 18           | 27                   | ns       |

**Note 1:** Min/max values apply across the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range for the DM7230 and across the 0°C to 70°C range for the DM8230 unless otherwise specified. Typicals are given for T<sub>A</sub> = 25°C and V<sub>CC</sub> = 5.0V.

Note 2: Only one output at a time should be short circuited.

**Note 3:** The only conditions under which a  $t_{od0}$  from the Address inputs can be observed is when an output goes from being nonselected to being selected and the information being routed to that output is a logical "0". If the information had been a logical "1", no change would have occurred and no measurement could have been made. Similarly, the only time a  $t_{od1}$  from the Address inputs can be observed, is when an output goes from being selected to being nonselected and the information that had been routed to that output was a logical "0". If the information had been a logical "1", no change would have occurred and no measurement could have been made.

Note 4: Information in Note 3 concerning tpd0 and tpd1 from the address inputs are applicable here also.

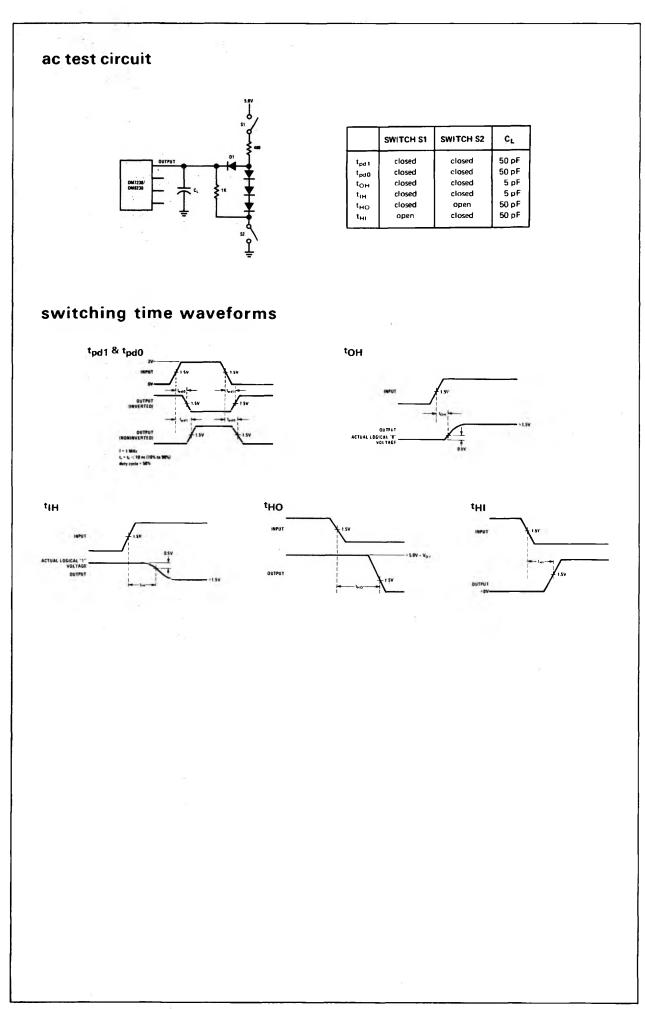

**Note 5:** All delays involving transitions to or from the High Impedance state are measured with respect to the Disable inputs. For example, with A information at a logical "0" and Disable B at a logical "1" the selected output will go from a logical "0" to the High Impedance state some time,  $t_{OH}$ , after Disable A has gone from a logical "0" to a logical "1"

DM7230/DM8230

5 X

GATED IN

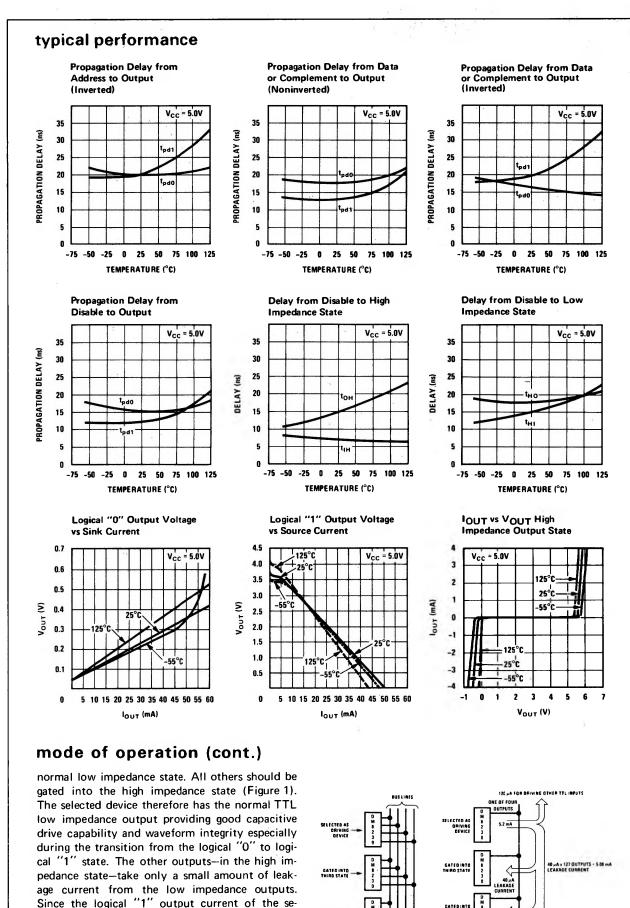

Figure 1

Figure 2

lected device is 13 times that of a conventional Series 54/74 device (5.2 mA vs 400  $\mu$ A), the output is easily able to supply that leakage current to

as many as 127 other DM7230/DM8230's and still have available drive for the bus-line. (Figure 2)

DM7230/DM8230

# 22

DM7230/DM8230