# National Semiconductor

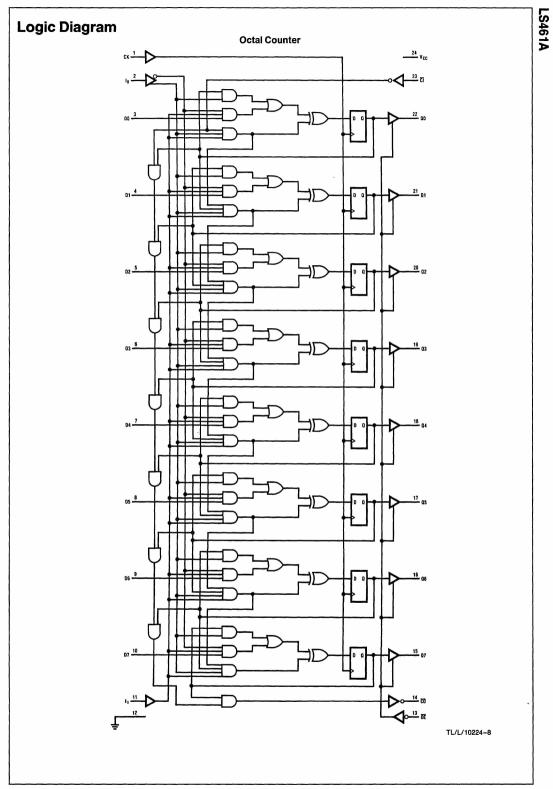

## DM54LS461A/DM74LS461A Octal Counter

## **General Description**

The LS461A is an 8-bit synchronous counter with parallel load, clear and hold capability. Two function select inputs (I0, I1) provide one of four operations which occur synchronously on the rising edge of the (CK).

The LOAD operation loads the inputs (D7–D0) into the output register (Q7–Q0). The CLEAR operation resets the output register to all LOWs. The HOLD operation holds the previous value regardless of the clock transitions. The IN-CREMENT operation adds one to the output register when the carry-in input is TRUE ( $\overline{CI} = LOW$ ), otherwise the operation is a HOLD. The carry-out ( $\overline{CO}$ ) is True ( $\overline{CO} = LOW$ ) when the output register (Q7–Q0) is all HIGHs, otherwise FALSE ( $\overline{CO} = HIGH$ ).

The output register (Q7–Q0) is enabled when  $\overline{\text{OE}}$  is LOW, and disabled (HI–Z) when  $\overline{\text{OE}}$  is HIGH. The output drivers will sink 24 mA required for many bus interface standards.

Two or more LS461A octal counters may be cascaded to provide larger counters. The operation codes were chosen such that when I1 is HIGH I0 may be used to select between LOAD and INCREMENT as in a program counter (JUMP/INCREMENT).

#### Features

- Octal counter for microprogram-counter, DMA controller for general purpose counting applications

- 8 bits match byte boundaries

- Low current PNP inputs reduce loading

- Bus-structured pinout

- TRI-STATE® outputs drive bus lines

- 24-pin SKINNYDIP saves space

- Expadable in 8-bit increments

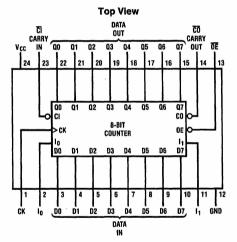

## **Connection Diagram**

TL/L/10224-1

## **Function Table**

| i | OE | СК | 11 | 10 | Ĉİ | D7-D0 | Q7-Q0    | Operation |

|---|----|----|----|----|----|-------|----------|-----------|

|   | Н  | х  | х  | х  | х  | х     | Z        | HI–Z      |

| 1 | L  | 1  | L  | L  | X  | х     | L        | CLEAR     |

| 1 | L  | 1  | L  | н  | х  | х     | Q        | HOLD      |

| 1 | L  | 1  | н  | L  | х  | D     | D        | LOAD      |

|   | L  | 1  | н  | н  | н  | Х     | Q        | HOLD      |

|   | L  | 1  | н  | Н  | L  | Х     | Q Plus 1 | INCREMENT |

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| V <sub>CC</sub> Supply Voltage | 7V   |

|--------------------------------|------|

| Input Voltage                  | 5.5V |

| Off-State Output Voltage       | 5.5V |

Storage Temperature ESD Tolerance Czap = 100 pFRzap =  $150\Omega$ Test Method: Human Bod -65°C to +150°C >1000V LS461A

10001

## **Recommended Operating Conditions**

| Symbol          | Parameter                      |     | Military |     |      | Units |      |       |

|-----------------|--------------------------------|-----|----------|-----|------|-------|------|-------|

| Cynibol         | i alanotoi                     | Min | Тур      | Max | Min  | Тур   | Max  | Unito |

| V <sub>CC</sub> | Supply Voltage                 | 4.5 | 5        | 5.5 | 4.75 | 5     | 5.25 | v     |

| T <sub>A</sub>  | Operating Free-Air Temperature | -55 | 25       |     | 0    | 25    | 75   | °C    |

| T <sub>C</sub>  | Operating Case Temperature     |     |          | 125 |      |       |      | °C    |

#### Electrical Characteristics Series 24A Over Recommended Operating Temperature Range

| Symbol          | Parameter                                                                     | т                                    | est Conditions              |     | Min   | Тур   | Max  | Units |

|-----------------|-------------------------------------------------------------------------------|--------------------------------------|-----------------------------|-----|-------|-------|------|-------|

| VIH             | High Level Input Voltage                                                      | (Note 2)                             |                             |     | 2     |       |      | v     |

| VIL             | Low Level Input Voltage                                                       | (Note 2)                             |                             |     |       | 0.8   | v    |       |

| VIC             | Input Clamp Voltage                                                           | $V_{CC} = Min, II = -18 mA$          |                             |     |       | -0.8  | -1.5 | v     |

| VOH             | High Level Output Voltage                                                     | V <sub>CC</sub> = Min                | I <sub>OH</sub> = -2 mA     | MIL |       |       |      |       |

|                 |                                                                               | $V_{IL} = 0.8V$<br>$V_{IH} = 2V$     | $I_{OH} = -3.2 \mathrm{mA}$ | СОМ | 2.4   | 2.9   |      | v     |

| V <sub>OL</sub> | Low Level Output Voltage                                                      | V <sub>CC</sub> = Min                | l <sub>OL</sub> = 12 mA     | MIL |       |       |      |       |

|                 |                                                                               | $V_{IL} = 0.8V$<br>$V_{IH} = 2V$     | $I_{OL} = 24 \text{ mA}$    | СОМ |       | 0.3   | 0.5  | V     |

| lozh            | Off-State Output Current (Note 3)                                             | $V_{CC} = Max$ $V_O = 2.4V$          |                             |     |       |       | 100  | μA    |

| IOZL            |                                                                               | $V_{IL} = 0.8V$<br>$V_{IH} = 2V$     | $V_{O} = 0.4V$              |     |       |       | -100 | μA    |

| lj –            | Maximum Input Current V <sub>CC</sub> = Max, V <sub>I</sub> = 5.5V            |                                      |                             |     |       |       | 1    | mA    |

| Iн              | High Level Input Current (Note 3)                                             | V <sub>CC</sub> = Max, V             | $V_{CC} = Max, V_I = 2.4V$  |     |       |       | 25   | μΑ    |

| կլ              | Low Level Input Current (Note 3) V <sub>CC</sub> = Max, V <sub>I</sub> = 0.4V |                                      |                             |     | -0.04 | -0.25 | mA   |       |

| los             | Output Short-Circuit Current                                                  | $V_{CC} = 5V$ $V_O = 0V$ (Note 4)    |                             |     | -30   | -70   | -130 | mA    |

| Icc             | Supply Current                                                                | Supply Current V <sub>CC</sub> = Max |                             |     |       | 135   | 180  | mA    |

Note 1: Absolute maximum ratings are those values beyond which the device may be permanently damaged. They do not mean that the device may be operated at these values.

Note 2: These are absolute voltages with respect to the ground pin on the device and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

Note 3: I/O leakage as the worst case of IOZX or IIX, e.g.,  $I_{\rm IL}$  and IOZL.

Note 4: During IOS measurement, only one output at a time should be grounded. Permanent damage otherwise may result.

| Symbol           | Parameter              | Test Conditions | Military               |                  |     | Commercial |                  |     | Units |    |

|------------------|------------------------|-----------------|------------------------|------------------|-----|------------|------------------|-----|-------|----|

| cynnool          | Set-Up Time from Input |                 | <b>Min</b><br>40       | <b>Typ</b><br>20 | Max | Min<br>30  | <b>Typ</b><br>20 | Max | ns    |    |

| ts               |                        |                 |                        |                  |     |            |                  |     |       |    |

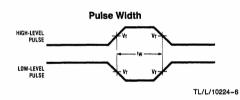

| tw               | Width of Clock         | High            |                        | 20               | 7   |            | 15               | 7   |       | ns |

|                  |                        | Low             |                        | 35               | 15  |            | 25               | 15  |       | ns |

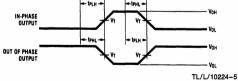

| T <sub>pd</sub>  | CBI to CBO Delay       |                 | $C_L = 50  pF$         |                  | 23  | 35         |                  | 23  | 30    | ns |

| T <sub>cik</sub> | Clock to Output        |                 | C <sub>L</sub> = 50 pF |                  | 10  | 25         |                  | 10  | 15    | ns |

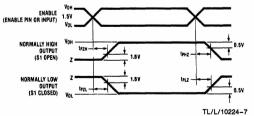

| Т <sub>рzx</sub> | Output Enable Delay    |                 | $C_L = 50  pF$         |                  | 19  | 35         |                  | 19  | 30    | ns |

| T <sub>pzx</sub> | Output Disable Delay   |                 | C <sub>L</sub> = 5 pF  |                  | 15  | 35         |                  | 15  | 30    | ns |

| t <sub>H</sub>   | Hold Time              |                 |                        | 0                | -15 |            | 0                | -15 |       | ns |

| f <sub>max</sub> | Maximum Frequency      |                 |                        | 15.3             | 32  |            | 22.2             | 32  |       | МН |

COM'L

R1 = 200

R2 = 390

• 3V

n٧

3V

3V

nν

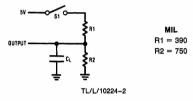

## **Test Load**

LS461A

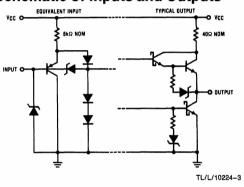

## Schematic of Inputs and Outputs

**Test Waveforms**

**tSET-UP**

CLOCK

INPUT

DATA INPUT

**Propagation Delay**

Set-Up and Hold

VT (SEE NOTE A)

- thold

Note A:  $V_T = 1.5V$ .

Note B: CL includes probe and jig capacitance.

Note C: In the examples above, the phase relationships between inputs and outputs have been chosen arbitrarily.