DLPA1000

SLVSDP7A - FEBRUARY 2017 - REVISED MAY 2017

# **DLPA1000 Power Management and LED Driver IC**

#### 1 Features

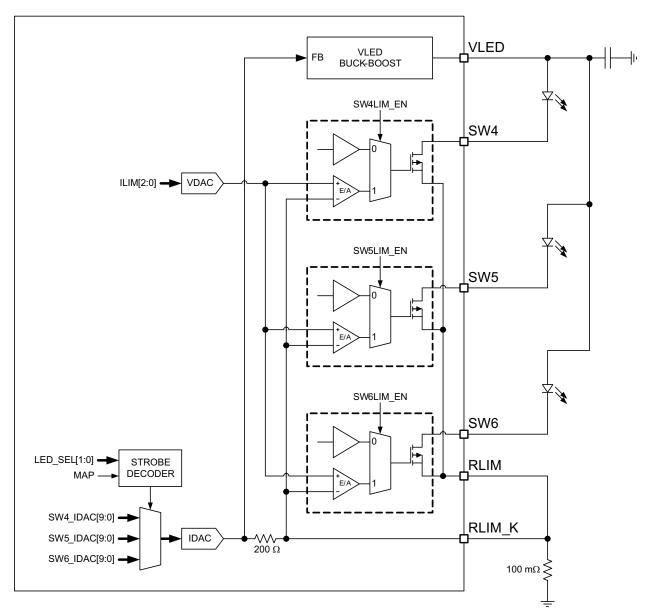

- High-Efficiency RGB LED Driver With Buck-Boost DC-to-DC Converter and Integrated MOSFETS

- Six Low-Impedance (<100 mΩ) MOSFET Switches for Channel Selection

- Independent, 10-Bit Current Control per Channel

- DMD Regulators

- Requires Only a Single Inductor

- VOFS: 8.5 VVBIAS: 16 VVRST: -10 V

- · Reset Generation and Power Supply Sequencing

- RGB LED Strobe Decoder Supports:

- Common-Anode RGBs

- Cathode-Cathode-Anode RGBs

- 33-MHz Serial Peripheral Interface (SPI)

- Multiplexer for Measuring Analog Signals

- Battery Voltage

- LED Voltage, LED Current

- Light Sensor (for White Point Correction)

- External Temperature Sensor

- Monitoring and Protection Circuits

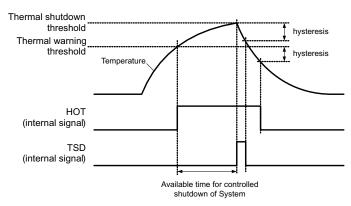

- Hot Die Warning and Thermal Shutdown

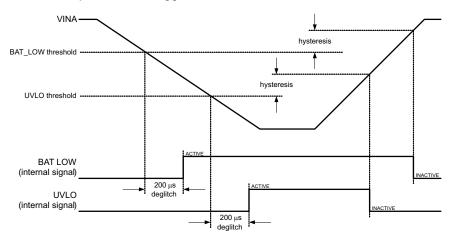

- Low-Battery and Undervoltage Lockout

- Overcurrent and Undervoltage Protection

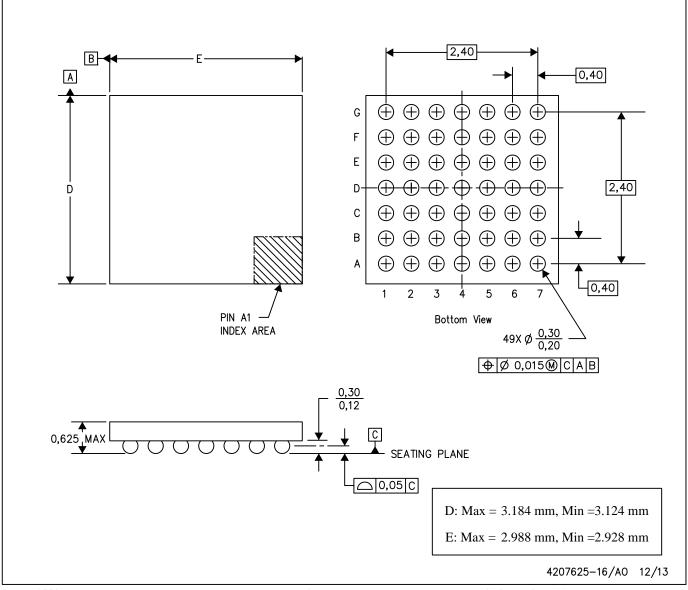

- 49-Ball 0.4-mm Pitch, DSBGA Package

## 2 Applications

- DLP<sup>®</sup> Pico<sup>™</sup> Projector

- Embedded Mobile Projection

- Smartphone

- Tablet

- Camera

- Laptop

- Mobile Accessories

- Wearable (Near-Eye) Displays

- · Battery-Operated Projectors

## 3 Description

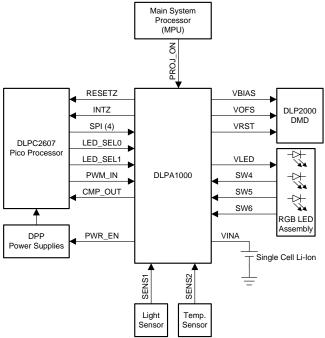

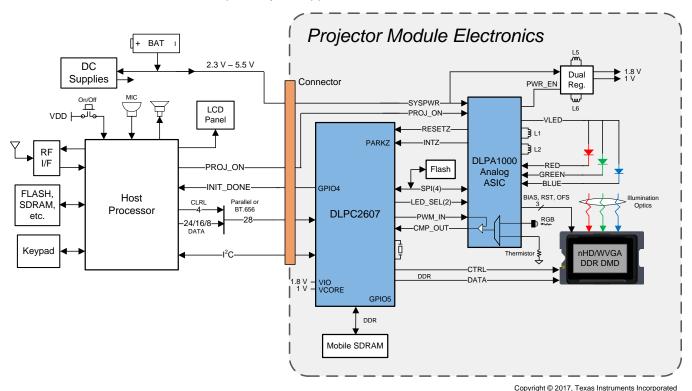

DLPA1000 is a dedicated PMIC / RGB LED driver for the DLP2000 Digital Micromirror Devices (DMD) when used with a DLPC2607 digital controller. For reliable operation of these chipsets, it is mandatory to use the DLPA1000.

#### Device Information<sup>(1)</sup>

| PART NUMBER |           | PACKAGE    | BODY SIZE (NOM)   |

|-------------|-----------|------------|-------------------|

|             | DI PA1000 | DSBGA (49) | 2.40 mm × 2.40 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

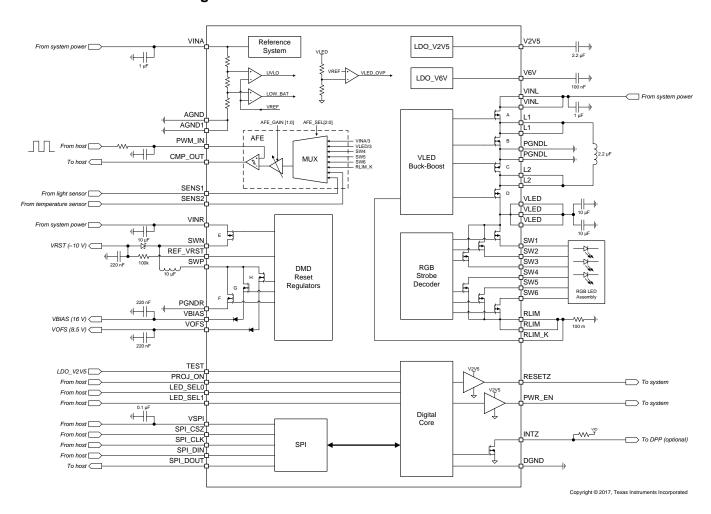

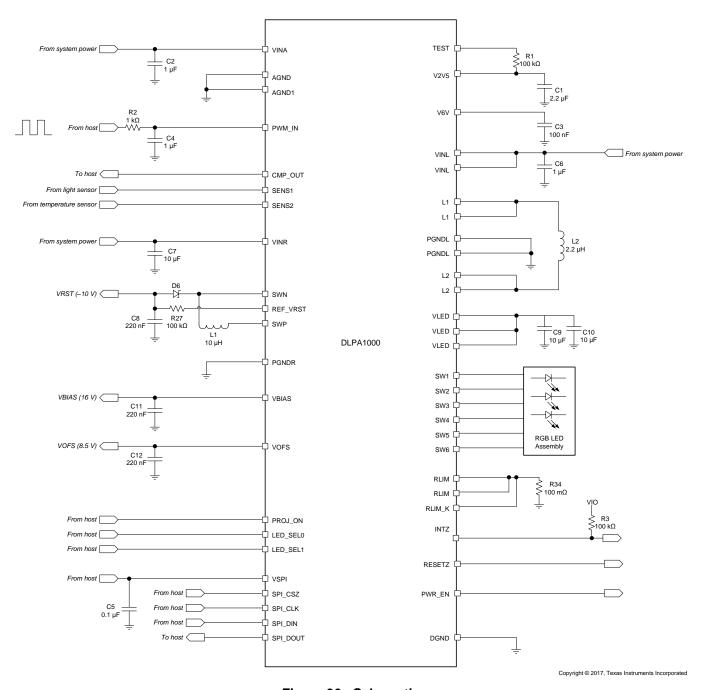

## Simplified Schematic

Copyright © 2017. Texas Instruments Incorporated

# **Table of Contents**

| 1 | Features 1                           | 7.5 Programming         |                            | 20               |

|---|--------------------------------------|-------------------------|----------------------------|------------------|

| 2 | Applications 1                       | 7.6 Register Maps       |                            | <mark>2</mark> 1 |

| 3 | Description 1                        | 8 Application and Imp   | olementation               | 35               |

| 4 | Revision History2                    | 8.1 Application Inform  | nation                     | 35               |

| 5 | Pin Configuration and Functions3     | 8.2 Typical Application | n                          | 35               |

| 6 | Specifications5                      | 9 Power Supply Reco     | mmendations                | 39               |

| • | 6.1 Absolute Maximum Ratings 5       | 10 Layout               |                            | 40               |

|   | 6.2 ESD Ratings                      | 10.1 Layout Guideline   | es                         | 40               |

|   | 6.3 Recommended Operating Conditions | 10.2 Layout Example     |                            | 41               |

|   | 6.4 Thermal Information              | 11 Device and Docum     | entation Support           | 42               |

|   | 6.5 Electrical Characteristics       | 11.1 Documentation      | Support                    | 42               |

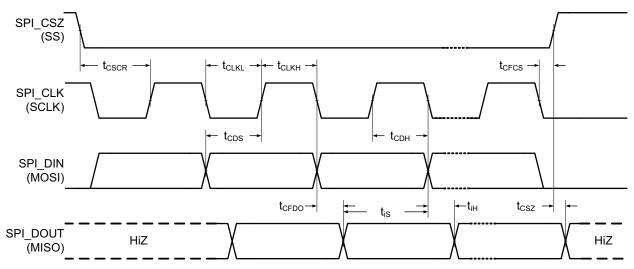

|   | 6.6 Timing Requirements9             | · ·                     | cation of Documentation Up | •                |

|   | 6.7 Typical Characteristics          | 11.3 Community Res      | ources                     | 42               |

| 7 | Detailed Description 11              | 11.4 Trademarks         |                            | 42               |

|   | 7.1 Overview 11                      | 11.5 Electrostatic Dis  | charge Caution             | 42               |

|   | 7.2 Functional Block Diagram 11      | 11.6 Glossary           |                            | 42               |

|   | 7.3 Feature Description 12           | 12 Mechanical, Packa    |                            |                  |

|   | 7.4 Device Functional Modes          | Information             |                            | 42               |

|   |                                      |                         |                            |                  |

# 4 Revision History

| Changes from Original (February 2017) to Revision A |                                         |   |    |  |

|-----------------------------------------------------|-----------------------------------------|---|----|--|

| •                                                   | Changed the Applications section        |   | 1  |  |

| •                                                   | Added the Documentation Support section | 4 | 12 |  |

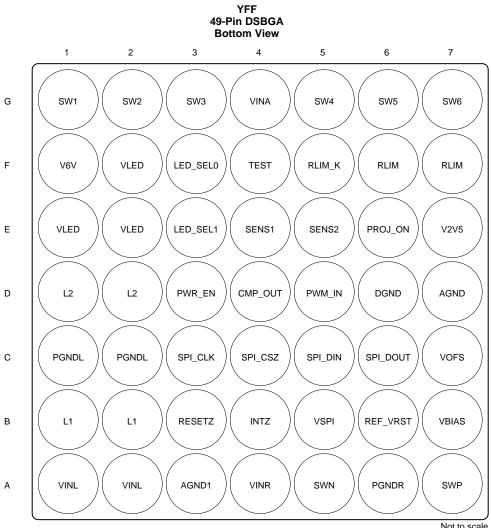

# 5 Pin Configuration and Functions

Not to scale

#### **Pin Functions**

| PIN      |     | 1/0    | DESCRIPTION                                                                           |  |

|----------|-----|--------|---------------------------------------------------------------------------------------|--|

| NAME     | NO. | 1/0    | DESCRIPTION                                                                           |  |

| VINL     | A1  | POWER  | Power supply input for VLED BUCK-BOOST power stage. Connect to system power.          |  |

| VINL     | A2  | POWER  | Power supply input for VLED BUCK-BOOST power stage. Connect to system power.          |  |

| AGND1    | A3  | GND    | Analog ground. Connect to ground plane.                                               |  |

| VINR     | A4  | POWER  | Power supply input for DMD switch mode power supply. Connect to system power.         |  |

| SWN      | A5  | IN (A) | onnection for the DMD SMPS-inductor (high-side switch).                               |  |

| PGNDR    | A6  | GND    | Power ground for DMD SMPS. Connect to ground plane.                                   |  |

| SWP      | A7  | IN(A)  | Connection for the DMD SMPS-inductor (low-side switch).                               |  |

| L1       | B1  | IN (A) | Connection for VLED BUCK-BOOST inductor.                                              |  |

| L1       | B2  | IN(A)  | Connection for VLED BUCK-BOOST inductor.                                              |  |

| RESETZ   | В3  | OUT(D) | Reset output to the DLP system (active low). Pin is held low to reset DLP system.     |  |

| INTZ     | B4  | OUT(D) | Interrupt output signal (open drain). Connect to pull-up resistor or short to ground. |  |

| VSPI     | B5  | POWER  | Power Supply input for SPI interface. Connect to system I/O voltage.                  |  |

| REF_VRST | В6  | IN(A)  | Reference pin for the VRST regulator. Connect to VRST rail through 100-kΩ resistor.   |  |

# Pin Functions (continued)

| PI       | N   |         | Fili Functions (continued)                                                                                                                                                  |  |

|----------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO. | 1/0     | DESCRIPTION                                                                                                                                                                 |  |

| VBIAS    | B7  | OUT(A)  | VBIAS output rail. Connect to ceramic capacitor.                                                                                                                            |  |

| PGNDL    | C1  | GND     | Power ground for VLED BUCK-BOOST. Connect to ground plane.                                                                                                                  |  |

| PGNDL    | C2  | GND     | Power ground for VLED BUCK-BOOST. Connect to ground plane.                                                                                                                  |  |

| SPI_CLK  | C3  | IN(D)   | Clock input for SPI interface.                                                                                                                                              |  |

| SPI_CSZ  | C4  | IN(D)   | SPI chip select (active low).                                                                                                                                               |  |

| SPI_DIN  | C5  | IN(D)   | SPI data input.                                                                                                                                                             |  |

| SPI_DOUT | C6  | OUT(D)  | SPI data output.                                                                                                                                                            |  |

| VOFS     | C7  | OUT(A)  | VOFS output rail. Connect to ceramic capacitor.                                                                                                                             |  |

| L2       | D1  | IN(A)   | Connection for VLED BUCK-BOOST inductor.                                                                                                                                    |  |

| L2       | D2  | IN(A)   | Connection for VLED BUCK-BOOST inductor.                                                                                                                                    |  |

| PWR_EN   | D3  | OUT(D)  | Enable pin for the external power supplies (active high).                                                                                                                   |  |

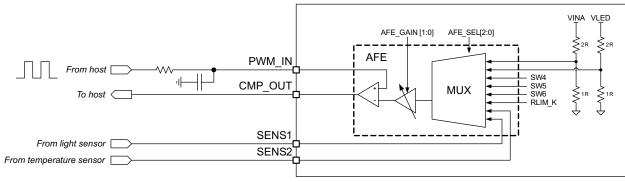

| CMP_OUT  | D4  | OUT(A)  | Analog-comparator output.                                                                                                                                                   |  |

| PWM_IN   | D5  | IN(D)   | Reference voltage input for analog comparator.                                                                                                                              |  |

| DGND     | D6  | GND     | Digital ground. Connect to ground plane.                                                                                                                                    |  |

| AGND     | D7  | GND     | Analog ground. Connect to ground plane.                                                                                                                                     |  |

| VLED     | E1  | OUT (A) | VLED BUCK-BOOST converter output pin.                                                                                                                                       |  |

| VLED     | E2  | OUT(A)  | LED BUCK-BOOST converter output pin.                                                                                                                                        |  |

| LED_SEL1 | E3  | IN(D)   | Digital input to the RGB STROBE DECODER.                                                                                                                                    |  |

| SENS1    | E4  | IN(A)   | Input signal from light sensor.                                                                                                                                             |  |

| SENS2    | E5  | IN(A)   | Input signal from temperature sensor.                                                                                                                                       |  |

| PROJ_ON  | E6  | IN(D)   | Input signal to enable/disable the IC and DLP projector.                                                                                                                    |  |

| V2V5     | E7  | OUT (D) | Internal supply filter pin for digital logic. Typical 2.45 V.                                                                                                               |  |

| V6V      | F1  | OUT(D)  | Internal supply filter pin for gate driver circuitry. Typical 6 V.                                                                                                          |  |

| VLED     | F2  | OUT(A)  | VLED BUCK-BOOST converter output pin.                                                                                                                                       |  |

| LED_SEL0 | F3  | IN(D)   | Digital input to the RGB STROBE DECODER.                                                                                                                                    |  |

| TEST     | F4  | IN(D)   | Test pin for digital, must be tied to the output capacitor of V2V5.                                                                                                         |  |

| RLIM_K   | F5  | IN(A)   | Kelvin sense connection for LED current sense resistor. For best accuracy, route signal with a dedicated trace separated from F6/F7 and connect directly at sense resistor. |  |

| RLIM     | F6  | OUT(A)  | Connection to LED current sense resistor. Connect to a 100-m $\Omega$ resistor.                                                                                             |  |

| RLIM     | F7  | OUT(A)  | Connection to LED current sense resistor. Connect to pin F6.                                                                                                                |  |

| SW1      | G1  | OUT(A)  | High-side MOSFET switch for LED anode. Connect to RGB LED assembly. If output is not used, short to VLED.                                                                   |  |

| SW2      | G2  | OUT(A)  | High-side MOSFET switch for LED anode. Connect to RGB LED assembly. If output is not used, short to VLED.                                                                   |  |

| SW3      | G3  | OUT(A)  | High-side MOSFET switch for LED anode. Connect to RGB LED assembly. If output is not used, short to VLED.                                                                   |  |

| VINA     | G4  | POWER   | Power supply input for sensitive analog circuitry.                                                                                                                          |  |

| SW4      | G5  | OUT(A)  | Low-side MOSFET switch for LED cathode. Connect to RGB LED assembly.                                                                                                        |  |

| SW5      | G6  | OUT(A)  | Low-side MOSFET switch for LED cathode. Connect to RGB LED assembly.                                                                                                        |  |

| SW6      | G7  | OUT(A)  | Low-side MOSFET switch for LED cathode. Connect to RGB LED assembly.                                                                                                        |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                  | perating free-air temperature range | ,                                                              | MIN       | MAX       | UNIT |

|------------------|-------------------------------------|----------------------------------------------------------------|-----------|-----------|------|

|                  | Input voltage                       | VINL, VINA, VINR                                               | -0.3      | 7         | V    |

|                  | Ground pins to system ground        |                                                                | -0.3      | 0.3       | V    |

|                  |                                     | SWN                                                            | -18       | 7         |      |

|                  |                                     | SWP, VBIAS                                                     | -0.3      | 20        |      |

|                  | Voltage                             | VOFS                                                           | -0.3      | 10        | V    |

|                  |                                     | V6V, VLED, L1, L2, SW1, SW2, SW3, SW4, SW5, SW6, INTZ, PROJ_ON | -0.3      | 7         |      |

|                  | All pins unless noted otherwise     |                                                                | -0.3      | 3.6       | V    |

|                  | Source current                      | RESETZ, PWR_EN, CMP_OUT                                        | 1         |           | A    |

|                  | Source current                      | SPI_DOUT                                                       | 5         | .5        | mA   |

|                  | Cial accompany                      | RESETZ, PWR_EN, CMP_OUT                                        |           | 1         | A    |

|                  | Sink current                        | SPI_DOUT, INTZ                                                 | 5         | .5        | mA   |

|                  | Peak output current                 |                                                                | Internall | y limited | mA   |

|                  | Continuous total power dissipation  |                                                                | Internall | y limited | W    |

| T <sub>A</sub>   | Operating ambient temperature       |                                                                | -30       | 85        | °C   |

| T <sub>stg</sub> | Storage temperature                 |                                                                | -65       | 150       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|---------------------------------------|

|                    |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V                                     |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|       |                                   |                                                    | MIN | NOM | MAX | UNIT     |

|-------|-----------------------------------|----------------------------------------------------|-----|-----|-----|----------|

|       | Input voltage at VINL, VINA, VINR | Full functional and parametric performance         | 2.7 | 3.6 | 6   |          |

|       |                                   | Extended operation, limited parametric performance | 2.3 | 3.6 | 6   | V        |

|       | Voltage at VSPI                   |                                                    | 1.7 | 1.8 | 3.6 | <b>V</b> |

| $T_A$ | Operating ambient temperature     |                                                    | -10 |     | 85  | °C       |

| $T_J$ | Operating junction temperature    |                                                    | -10 |     | 125 | °C       |

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# TEXAS INSTRUMENTS

#### 6.4 Thermal Information

|                      |                                              | DLPA1000    |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT |

|                      |                                              | 49 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 49          | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.1         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.9         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.1         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.9         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

$V_{IN} = 3.6 \text{ V}$ ,  $T_A = -10^{\circ}\text{C}$  to 85°C, typical values are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

|                       | PARAMETER                                   | TEST CONDITIONS                                                                                | MIN | TYP    | MAX | UNIT |

|-----------------------|---------------------------------------------|------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| INPUT VOL             | TAGE                                        |                                                                                                |     |        | '   |      |

|                       | Input voltage range                         | VINIA VINID VINI                                                                               | 2.7 | 3.6    | 6   |      |

| $V_{IN}$              | Extended input voltage range <sup>(1)</sup> | VINA, VINR, VINL                                                                               | 2.3 | 3.6    | 6   | V    |

|                       | Low battery warning threshold               | V <sub>INA</sub> falling                                                                       |     | 3      |     | V    |

| $V_{LOW\_BAT}$        | Hysteresis                                  | V <sub>INA</sub> rising                                                                        |     | 100    |     | mV   |

|                       | Undervoltage lockout threshold              | V <sub>INA</sub> falling                                                                       |     | 2.3    |     | V    |

| $V_{UVLO}$            | Hysteresis                                  | V <sub>INA</sub> rising                                                                        |     | 100    |     | mV   |

| V <sub>STARTUP</sub>  | Startup voltage                             | VBIAS, VOFS, VRST loaded with 2 mA                                                             | 2.5 |        |     | V    |

| INPUT CUE             | RRENT                                       |                                                                                                |     |        | ,   |      |

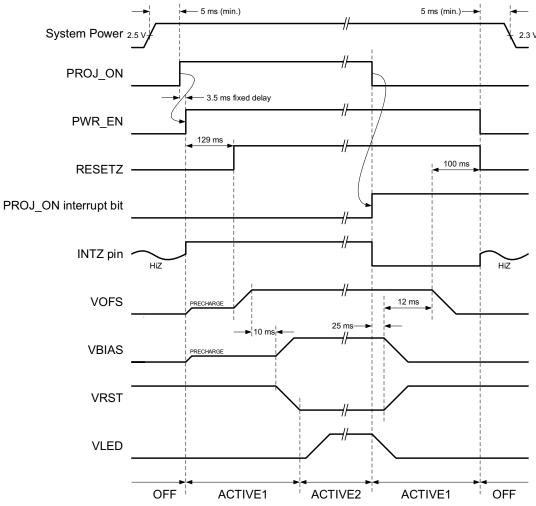

| IQ                    |                                             | ACTIVE2 mode                                                                                   |     | 12     |     | mA   |

| I <sub>STD</sub>      |                                             | STANDBY mode                                                                                   |     | 360    |     | μA   |

| I <sub>SLEEP</sub>    |                                             | SLEEP mode                                                                                     |     | 10     |     | μA   |

| INTERNAL              | SUPPLIES                                    |                                                                                                |     |        | •   |      |

| V <sub>V6V</sub>      | Internal supply, analog                     |                                                                                                |     | 6.25   |     | V    |

| C <sub>LDO_V6V</sub>  | Filter capacitor for V6V LDO                |                                                                                                |     | 100    |     | nF   |

| V <sub>V2V5</sub>     | Internal supply, logic                      |                                                                                                |     | 2.5    |     | V    |

| C <sub>LDO_V2V5</sub> | Filter capacitor for V2V5 LDO               |                                                                                                |     | 2.2    |     | μF   |

| DMD REGI              | JLATOR                                      |                                                                                                |     |        | ,   |      |

| <b>D</b>              | MOOFFT                                      | Switch E (from VINR to SWN)                                                                    |     | 1000   |     | 0    |

| R <sub>DS(ON)</sub>   | MOSFET on resistance                        | Switch F (from SWP to PGND)                                                                    |     | 320    |     | mΩ   |

| V                     | Commend walks are done.                     | Switch G (from SWP to VBIAS) <sup>(2)</sup><br>VINR = 5 V, VSWP = 2 V, I <sub>F</sub> = 100 mA |     | 1.3    |     | V    |

| $V_{FW}$              | Forward voltage drop                        | Switch H (from SWP to VOFS)<br>VINR = 5 V, VSWP = 2 V, I <sub>F</sub> = 100 mA                 |     | 1.3    |     | V    |

| R <sub>DIS</sub>      | Discharge resistor (SWP to GND)             | Active when all rails are disabled                                                             |     | 2      |     | kΩ   |

| t <sub>PG</sub>       | Power-good timeout                          | Not tested in production                                                                       |     | 6      |     | ms   |

| I <sub>LIMIT</sub>    | Switch current limit                        |                                                                                                |     | 200(3) |     | mA   |

| L                     | Inductor value                              |                                                                                                |     | 10     |     | μH   |

<sup>(1)</sup> Full functional but limited parametric performance.

<sup>(2)</sup> Including rectifying diode.

<sup>(3)</sup> Contact factory for 100-mA and 300-mA options.

# **Electrical Characteristics (continued)**

$V_{IN} = 3.6 \text{ V}$ ,  $T_A = -10^{\circ}\text{C}$  to 85°C, typical values are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

|                       | PARAMETER                            | TEST CONDITIONS                                                             | MIN  | TYP  | MAX | UNIT  |

|-----------------------|--------------------------------------|-----------------------------------------------------------------------------|------|------|-----|-------|

| V <sub>OFS</sub> REG  | ULATOR                               |                                                                             |      |      |     |       |

|                       | Output voltage                       |                                                                             |      | 8.5  |     | V     |

|                       | DC output voltage accuracy           | I <sub>OUT</sub> = 2 mA                                                     | -2%  |      | 2%  |       |

| $V_{OFS}$             | DC load regulation                   | V <sub>IN</sub> = 3.6 V, I <sub>OUT</sub> = 0 mA to 4 mA                    |      | -19  |     | V/A   |

|                       | DC line regulation                   | VINA, VINL, VINR 2.7 V to 6 V,<br>I <sub>OUT</sub> = 2 mA                   |      | 35   |     | mV/V  |

| V <sub>RIPPLE</sub>   | Output ripple                        | $V_{IN} = 3.6 \text{ V}, I_{OUT} = 4 \text{ mA}, C_{OUT} = 220 \text{ nF}$  |      | 240  |     | mV    |

| I <sub>OUT</sub>      | Output current                       | 110 010 1, 1001                                                             | 0    |      | 3   | mA    |

|                       | Power-good threshold                 | V <sub>OFS</sub> rising                                                     |      | 85%  |     |       |

| PG                    | (fraction of nominal output voltage) | V <sub>OFS</sub> falling                                                    |      | 62%  |     |       |

| R <sub>DIS</sub>      | Output discharge resistor            | Active when rail is disabled                                                |      | 2    |     | kΩ    |

| C                     | Output capacitor                     | Recommended value                                                           | 110  | 220  |     | nF    |

| V <sub>BIAS</sub> REG | ULATOR                               |                                                                             |      |      |     |       |

| DIAG                  | Output voltage                       |                                                                             |      | 16   |     | V     |

|                       | DC output voltage accuracy           | I <sub>OUT</sub> = 2 mA                                                     | -2%  |      | 2%  |       |

| $V_{BIAS}$            | DC load regulation                   | $V_{IN} = 3.6 \text{ V}, I_{OUT} = 0 \text{ mA to 4 mA}$                    |      | -14  |     | V/A   |

|                       | DC line regulation                   | VINA, VINL, VINR 2.7 V to 6 V,<br>I <sub>OUT</sub> = 2 mA                   |      | 18   |     | mV/V  |

| V <sub>RIPPLE</sub>   | Output ripple                        | V <sub>IN</sub> = 3.6 V, I <sub>OUT</sub> = 4 mA, C <sub>OUT</sub> = 220 nF |      | 240  |     | mV    |

| I <sub>OUT</sub>      | Output current                       | 7 301                                                                       | 0    |      | 4   | mA    |

|                       | Power-good threshold                 | V <sub>OFS</sub> rising                                                     |      | 85%  |     |       |

| PG                    | (fraction of nominal output voltage) | V <sub>OFS</sub> falling                                                    |      | 62%  |     |       |

| R <sub>DIS</sub>      | Output discharge resistor            | Active when rail is disabled                                                |      | 2    |     | kΩ    |

| С                     | Output capacitor                     | Recommended value                                                           | 110  | 220  |     | nF    |

| V <sub>RST</sub> REGI | •                                    |                                                                             |      |      |     |       |

| NOI -                 | Output voltage                       |                                                                             |      | -10  |     | V     |

|                       | DC output voltage accuracy           | I <sub>OUT</sub> = 2 mA                                                     | -2%  |      | 2%  | -     |

| $V_{RST}$             | DC load regulation                   | $V_{IN} = 3.6 \text{ V}, I_{OUT} = 0 \text{ mA to 4 mA}$                    |      | 13   |     | V/A   |

|                       | DC line regulation                   | VINA, VINL, VINR 2.7 V to 6 V,<br>I <sub>OUT</sub> = 2 mA                   |      | -21  |     | mV/V  |

| V <sub>RIPPLE</sub>   | Output ripple                        | $V_{IN} = 3.6 \text{ V}, I_{OUT} = 4 \text{ mA}, C_{OUT} = 220 \text{ nF}$  |      | 240  |     | mV    |

| V <sub>REF_VRST</sub> | Reference voltage                    | 11N 212 1, 1001 1 1 1 2 2 1 1                                               |      | 500  |     | mV    |

| I <sub>OUT</sub>      | Output current                       |                                                                             | 0    |      | 4   | mA    |

| PG                    | Power-good threshold                 |                                                                             |      | -9.1 |     | V     |

| С                     | Output capacitor                     | Recommended value                                                           | 110  | 220  |     | nF    |

| V <sub>LED</sub> BUCI | <u>'</u>                             |                                                                             |      |      |     |       |

|                       | Output voltage range                 |                                                                             | 1.2  |      | 5.9 |       |

| $V_{LED}$             | Default output voltage               | SW4/5/6 in OPEN position                                                    |      | 3.5  | 0.0 | V     |

| V <sub>OVP</sub>      | Output overvoltage protection        | Clamps buck-boost output                                                    |      | 5.9  |     | V     |

| V <sub>LED_OVP</sub>  | Fault detection threshold            | Triggers VLED_OVP interrupt                                                 |      | 5.4  |     | V     |

| I <sub>SW</sub>       | Switch current limit                 | mggere verb_evr interrupt                                                   | 1.65 | 2.2  | 2.5 | A     |

| · 3 V V               | C.Mon Ganone mine                    | Switch A (from VINL to L1)                                                  | 1.00 | 100  | 2.0 | ,,    |

|                       |                                      | Switch B (from L1 to GND)                                                   |      | 100  |     |       |

| R <sub>DS(ON)</sub>   | MOSFET on resistance                 | Switch C (from L2 to GND)                                                   |      | 100  |     | mΩ    |

|                       |                                      | Switch D (from L2 to VLED)                                                  |      | 100  |     |       |

| f <sub>SW</sub>       | Switching frequency                  | SWILCH D (HOIH LZ to VLED)                                                  |      | 2.25 |     | MHz   |

| LOVA                  | Switching frequency                  |                                                                             | 1    | ۷.۷۵ |     | IVI□Z |

Copyright © 2017, Texas Instruments Incorporated

Submit Documentation Feedback

# **Electrical Characteristics (continued)**

$V_{IN}$  = 3.6 V,  $T_A$  = -10°C to 85°C, typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                       | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                                | MIN  | TYP  | MAX | UNIT |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|-----|------|

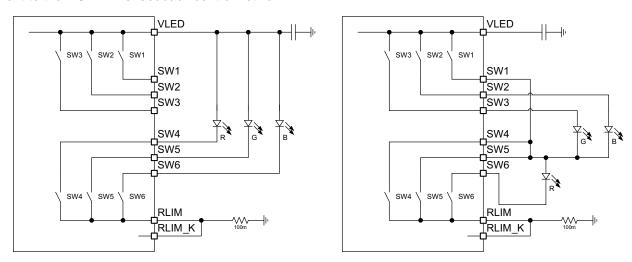

| RGB STR               | ROBE CONTROLLER SWITCHES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                |      |      |     |      |

| Б                     | Danie a company and a contract of the contract | SW1, SW2, SW3                                                                  |      | 50   | 100 | 0    |

| R <sub>DS(ON)</sub>   | Drain-source on resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SW4, SW5, SW6                                                                  |      | 40   | 100 | mΩ   |

| I <sub>LEAK</sub>     | Off-state leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VDS = 5 V                                                                      |      |      | 1   | μA   |

| LED CUR               | RENT CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |      |      |     |      |

| V <sub>f</sub>        | LED forward voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I <sub>LED</sub> = 1 A                                                         |      |      | 4.8 | V    |

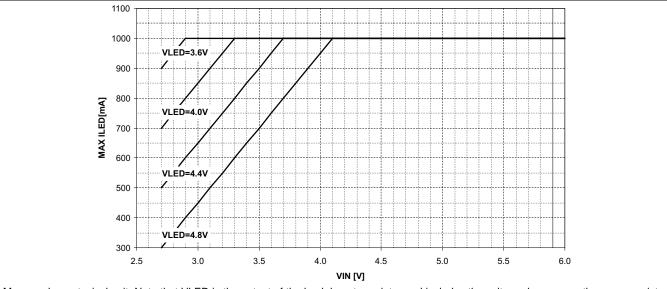

|                       | Maximum LED drive current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{IN} = 3.1 \text{ V}, V_{LED} = 4.4 \text{ V}$                              |      | 700  |     | mA   |

|                       | Maximum LED drive current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{IN} = 4 \text{ V}, V_{LED} = 4.4 \text{ V}$                                |      | 1000 |     | mA   |

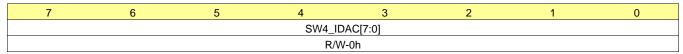

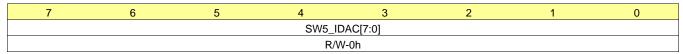

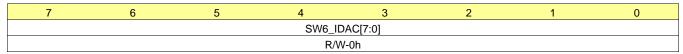

| I <sub>LED</sub>      | DC current accuracy, SW4, 5, 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SWx_IDAC[9:0] = 0x100h<br>$R_{LIM}$ = 100 m $\Omega$ , 0.1%, $T_A$ = 25°C      | 258  | 272  | 286 | mA   |

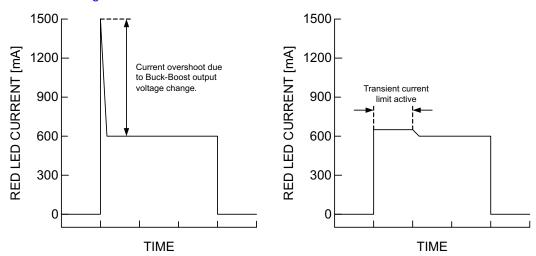

|                       | Transiant I ED aurrant limit range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ILIM[2:0] = 000                                                                |      | 260  |     | A    |

|                       | Transient LED current limit range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ILIM[2:0] = 111                                                                |      | 1250 |     | mA   |

| t <sub>rise</sub>     | Current rise time (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $I_{LED}$ from 5% to 95%, $I_{LED}$ = 300 mA, transient current limit disabled |      |      | 50  | μs   |

| MEASUR                | EMENT SYSTEM (AFE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                                                              | •    |      | •   |      |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AFE_GAIN[1:0] = 01                                                             |      | 1    |     |      |

| G                     | Amplifier gain (PGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AFE_GAIN[1:0] = 10                                                             |      | 9.5  |     | V/V  |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AFE_GAIN[1:0] = 11                                                             |      | 18   |     |      |

| V                     | Input referred offset voltage (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PGA, AFE_CAL_DIS = 1                                                           | -1   |      | 1   | m\/  |

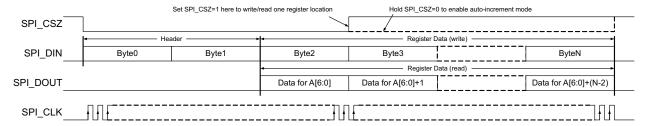

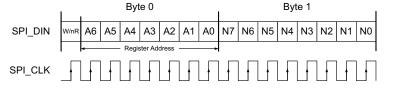

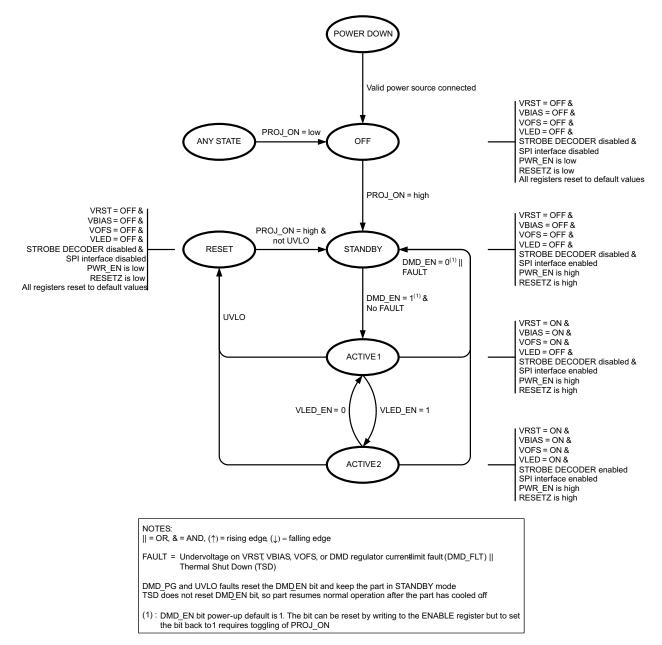

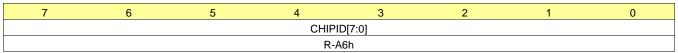

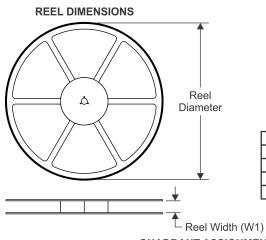

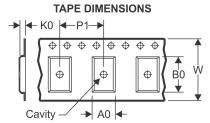

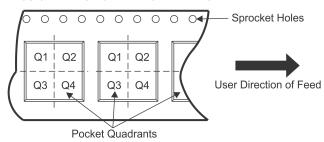

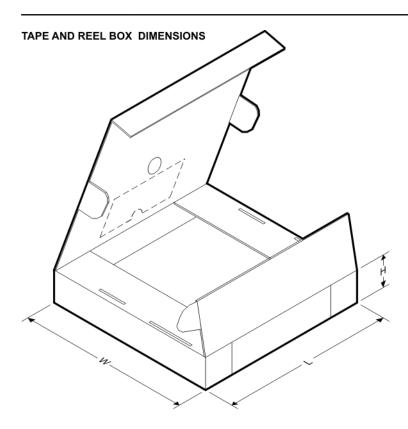

| $V_{OFS}$             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Comparator                                                                     | -1.5 |      | 1.5 | mV   |