ADVANCE INFORMATION DAC 3560C Audio-Subsystem for Portable Applications Edition Feb. 5, 2003 **\***MICRONAS 6251-588-1AI

## Contents

| Page | Section  | Title                                      |

|------|----------|--------------------------------------------|

| 4    | 1.       | Introduction                               |

| 4    | 1.1.     | Features                                   |

| 4    | 1.2.     | Target Systems                             |

| 6    | 2.       | Functional Description                     |

| 6    | 2.1.     | Digital Audio Interface (I <sup>2</sup> S) |

| 7    | 2.2.     | Clock System                               |

| 7    | 2.3.     | Control Interface                          |

| 7    | 2.4.     | Registers                                  |

| 8    | 2.5.     | I <sup>2</sup> C Bus Interface             |

| 8    | 2.6.     | SPI Bus Interface                          |

| 8    | 2.7.     | Noise Shaper and Multibit DAC              |

| 8    | 2.8.     | Analog Low-Pass                            |

| 8    | 2.9.     | Analog Input                               |

| 9    | 2.10.    | Analog Audio Driver Output                 |

| 9    | 2.11.    | LDO                                        |

| 9    | 2.12.    | Charge Pump                                |

| 9    | 2.13.    | Reference Block                            |

| 9    | 2.14.    | Temperature Overload Protection            |

| 9    | 2.15.    | Power Management                           |

| 9    | 2.16.    | Click and Pop Suppression                  |

| 10   | 3.       | Control Registers                          |

| 10   | 3.1.     | Register Map                               |

| 15   | 4.       | Specifications                             |

| 15   | 4.1.     | Outline Dimensions                         |

| 16   | 4.2.     | Pin Connections and Short Descriptions     |

| 17   | 4.3.     | Pin Descriptions                           |

| 17   | 4.3.1.   | Power Supply Pins                          |

| 18   | 4.3.2.   | Analog Reference Pins                      |

| 18   | 4.3.3.   | Analog Audio Pins                          |

| 18   | 4.3.4.   | Digital Audio Input Pins                   |

| 18   | 4.3.5.   | Control Interface Pins                     |

| 18   | 4.3.6.   | Other Pins                                 |

| 19   | 4.4.     | Pin Configurations                         |

| 19   | 4.5.     | Pin Circuits                               |

| 21   | 4.6.     | Electrical Characteristics                 |

| 21   | 4.6.1.   | Absolute Maximum Ratings                   |

| 22   | 4.6.2.   | Recommended Operating Conditions           |

| 23   | 4.6.3.   | Characteristics (LDO Mode)                 |

| 26   | 4.6.4.   | Characteristics (Non-LDO Mode)             |

| 28   | 4.6.5.   | Terminology                                |

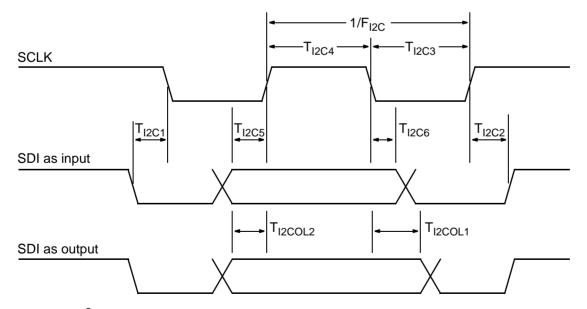

| 29   | 4.6.6.   | I <sup>2</sup> C Bus Characteristics       |

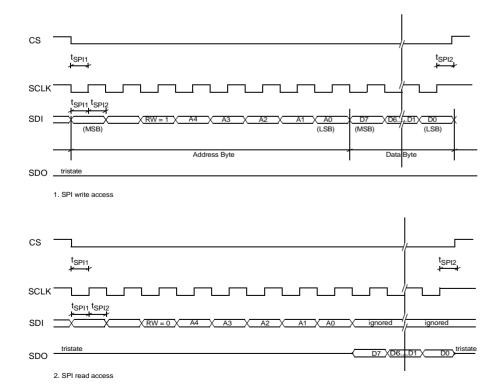

| 30   | 4.6.6.1. | I <sup>2</sup> S Bus Characteristics       |

| 31   | 4.6.6.2. | SPI-Bus Characteristics                    |

| 32   | 4.6.7.   | Power Consumption (LDO Mode)               |

## Contents, continued

| Page | Section | Title                                              |

|------|---------|----------------------------------------------------|

| 33   | 5.      | Detailed Mode Description                          |

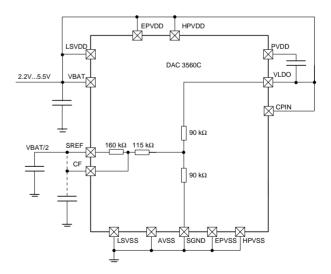

| 33   | 5.1.    | LDO Mode, Using the internal Low-Dropout Regulator |

| 33   | 5.2.    | Non-LDO Mode, Using the DAC 3560C without the LDO  |

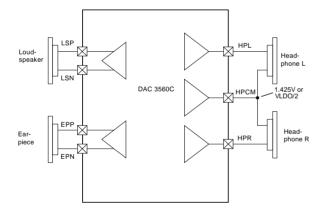

| 34   | 5.3.    | Headphone Common Driver                            |

| 34   | 5.4.    | Stereo, Mono Mode Operation of the DAC 3560C       |

| 35   | 5.4.1.  | Digital Supply                                     |

| 35   | 5.4.2.  | Power On/Off Sequence                              |

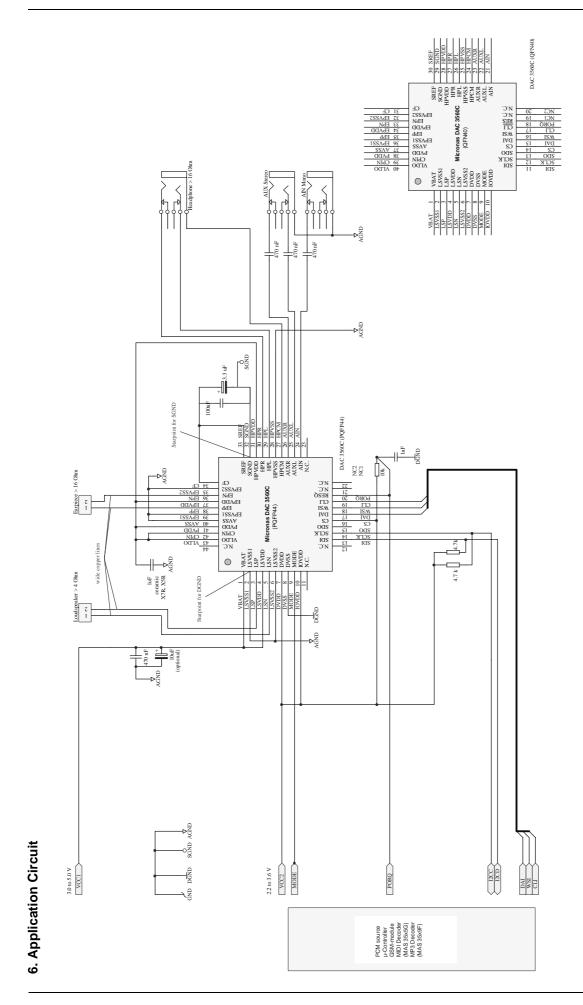

| 36   | 6.      | Application Circuit                                |

| 38   | 7.      | Data Sheet History                                 |

#### **Audio-Subsystem for Portable Applications**

#### 1. Introduction

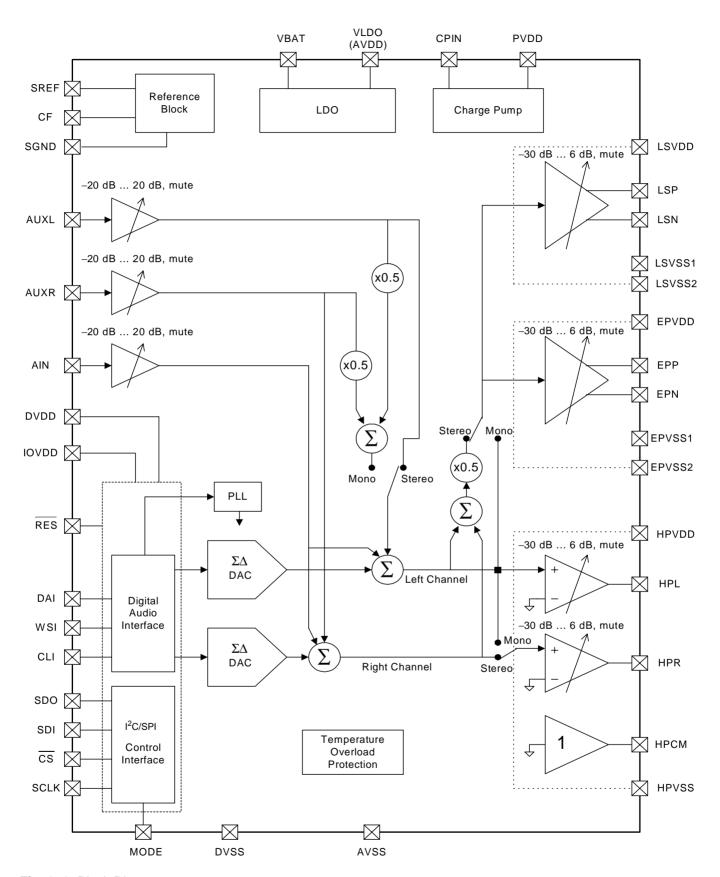

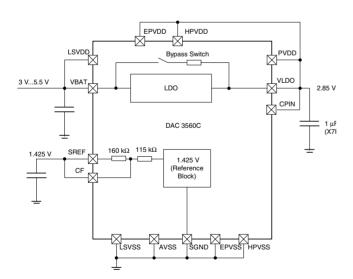

The DAC 3560C is a single-chip, high-precision, dual digital-to-analog converter designed for audio applications. The employed conversion technique is based on oversampling with noise-shaping.

With Micronas' unique multibit sigma-delta technique, less sensitivity to clock jitter, high linearity, and a superior S/N ratio have been achieved. The DAC 3560C is controlled via SPI or I<sup>2</sup>C bus.

Digital audio input data is received via a versatile I<sup>2</sup>S interface. The DAC 3560C provides three integrated power audio drivers: a stereo headphone, a mono earpiece and a mono loudspeaker driver. Moreover, mixing additional analog sources to the D/A-converted signal is supported.

For applications with a noise-critical power supply environment, the DAC 3560C is equipped with an integrated Low Drop-Out Voltage Regulator (LDO). The LDO provides a stable 2.85 V output voltage and is intended for supplying the headphone and earpiece drivers. With the LDO, the Power Supply Rejection Ratio (PSRR) of the audio outputs is improved to more than 100 dB.

The DAC 3560C is designed for all kinds of applications in the audio and multimedia field, such as: mobile phones, PDAs, and digital audio players.

#### 1.1. Features

- Three Integrated Short-Circuit-Protected Power Audio Drivers:

- Stereo headphone output (25 mW at V<sub>SUP</sub>=2.85 V, or 80 mW at V<sub>SUP</sub>=5 V respectively)

- Mono earpiece output (100 mW at V<sub>SUP</sub>=2.85 V, or 300 mW at V<sub>SUP</sub>=5 V, respectively)

- Mono loudspeaker output (400 mW at V<sub>SUP</sub>=3 V, or 1.1 W at V<sub>SUP</sub>=5 V, respectively)

- Integrated LDO (Low Drop-Out Regulator)

- 100 dB PSRR

- 98 dB (A) Dynamic Range Multi-Bit Sigma Delta DAC

- Continuous Sample Rates from 8 kHz to 192 kHz

- Capacitor-free Headset Connection

- Analog Stereo and Mono Line Inputs with Programmable Gain

- I<sup>2</sup>C/SPI Compatible Serial Control Ports

- I<sup>2</sup>S Digital Audio Interface

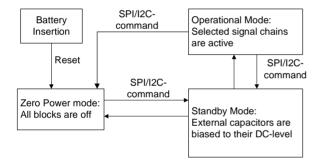

- Programmable Power Management

- -30 dB to 6 dB Analog Volume, Mute

- 2.2 V to 5.5 V Supply Voltage

- 1.8 V to 5.5 V Digital I/O Voltage

- Standby Mode

- Zero-Power Mode (< 10 μA)

- PQFN40 Package

### 1.2. Target Systems

- PDAs

- Hand-held Terminals

- Mobile and Cordless Phones

- Portable MP3 and CD Players

Fig. 1-1: Block Diagram

5

#### 2. Functional Description

The main blocks are described in the following chapters. All functions are controlled via I<sup>2</sup>C/SPI protocol.

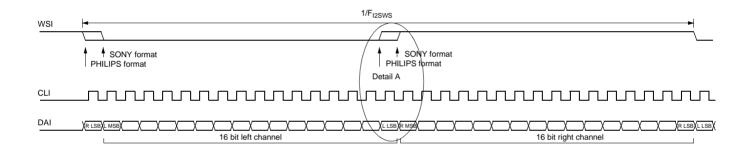

## 2.1. Digital Audio Interface (I<sup>2</sup>S)

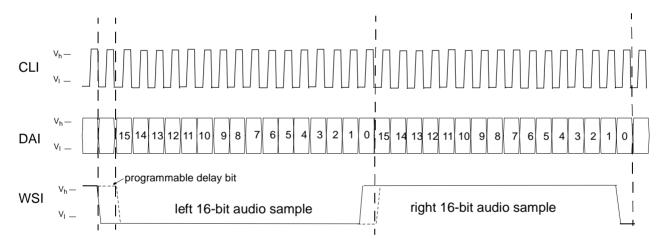

The I<sup>2</sup>S interface is the digital audio interface between the DAC 3560C and external digital audio sources. It covers most of the I<sup>2</sup>S-compatible formats. All modes have two common features:

- 1. The MSB is left-justified to an I<sup>2</sup>S frame identification (WSI) transition.

- 2. Data is valid on the rising edge of the bit clock CLI.

#### 16-bit mode:

In this case, the bit clock is 32 x fs<sub>audio</sub>. Maximum word length is 16 bit.

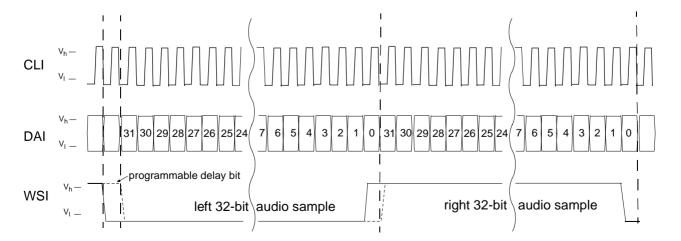

## 32-bit mode:

In this case, the bit clock is 64 x fs<sub>audio</sub>. Maximum word length is 32 bit.

#### **Automatic Detection:**

No I<sup>2</sup>C/SPI control is required to switch between 16-bit and 32-bit mode. It is recommended to switch the DAC 3560C into mute position while alternating between the two modes. For high-quality audio, it is recommended to use the 32-bit mode of the I<sup>2</sup>S interface to make use of the full dynamic range (if more than 16 bits are available).

## Left-Right Selection:

Standard I<sup>2</sup>S format defines an audio frame always starting with the left channel and low-state of WSI. However, the DAC 3560C permits to change the polarity of WSI.

## **Delay Bit:**

The standard I<sup>2</sup>S format requires a delay of one clock cycle between transitions of WSI and data MSB. In order to fit other formats, however, this characteristic can be switched on or off.

**Note:** Volume mute should be applied before changing I<sup>2</sup>S mode in order to avoid audible clicks

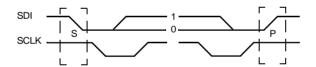

Fig. 2-1: I<sup>2</sup>S 16-bit mode

Fig. 2-2: I<sup>2</sup>S 32-bit mode

#### 2.2. Clock System

Most DACs need 256 x fs<sub>audio</sub>, 384 x fs<sub>audio</sub>, or at least an asynchronous clock. The DAC 3560C does not need an external Master clock. No crystal is required.

All internal clocks are generated by an internal PLL circuit, which locks to the  $I^2S$  bit clock (CLI). If no  $I^2S$  clock is present, the IC can still be controlled and the analog signal path is still available as no  $I^2S$  clock is needed for this.

The PLL also generates the clock for the DAC and the noise shaping system. Audible oversampling artifacts even at low audio sampling frequencies are eliminated.

#### 2.3. Control Interface

The DAC 3560C has many register-programmable features. The control interface is used to program the registers of the device. It uses four pins:

SCLK - Serial Data Clock

SDI - Serial Data Input (Input/Output for I<sup>2</sup>C)

SDO - Serial Data Output (SPI)

CS - Chip Select (SPI)

Table 2-1: Standard Protocols

| MODE Pin | Control Protocol |

|----------|------------------|

| 1        | I <sup>2</sup> C |

| 0        | SPI              |

The control interface supports two standard protocols, the I<sup>2</sup>C protocol (two-wire operation) and the SPI protocol (three or four-wire operation). The state of the MODE pin selects the control interface type.

#### 2.4. Registers

All registers of the DAC 3560C are 8 bits wide and offer read/write access.

In Section 3. "Control Registers", a definition of the DAC 3560C control registers is shown. A hardware reset initializes all control registers to 0, which is the default value for all registers. The registers are addressed by the sub-address byte, which follows the device address in I<sup>2</sup>C mode and is the first byte to be sent in SPI mode. The structure of the sub-address is identical in both modes (R/W is ignored in I<sup>2</sup>C mode).

Table 2-2: Sub-Address Byte

| Bit      | D7 | D6 | D5  | D4 | D3 | D2 | D1 | D0 |

|----------|----|----|-----|----|----|----|----|----|

| Function | 0  | 0  | R/W | A4 | А3 | A2 | A1 | A0 |

Table 2-3: Structure of the Sub-Address Byte

| R                 | Reserved                               | Set to 0 |         |

|-------------------|----------------------------------------|----------|---------|

| R/W <sup>1)</sup> | Read/Write Access                      | 1=Read   | 0=Write |

| A [4:0]           | Control Interface<br>Sub-Address       |          |         |

| 1) R/W n          | nust be set to 0 in I <sup>2</sup> C r | mode     |         |

Note: Pin  $\overline{\text{CS}}$  must be set to IOVDD when using I<sup>2</sup>C mode.

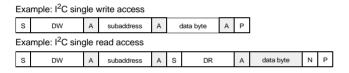

#### 2.5. I<sup>2</sup>C Bus Interface

The DAC 3560C is equipped with an I<sup>2</sup>C bus slave interface. The I<sup>2</sup>C bus interface uses one level of subaddressing: the I<sup>2</sup>C device address is used to address the IC. The registers are read/write. The register address is incremented automatically at each data byte unless a stop condition occurs. The I<sup>2</sup>C device address is given below.

Table 2-4: I<sup>2</sup>C device address byte

| A7 | <b>A6</b> | <b>A</b> 5 | <b>A4</b> | А3 | A2 | <b>A</b> 1 | W/R |

|----|-----------|------------|-----------|----|----|------------|-----|

| 1  | 0         | 0          | 1         | 1  | 0  | 1          | 0/1 |

Fig. 2–3 shows I<sup>2</sup>C bus protocols for write and read operations of the interface; the read operations require an extra start condition and repetition of the chip address with the device read command (DR). Fields with signals/data originating from the DAC 3560C are marked with a gray background.

**Fig. 2–3:** Example of an I<sup>2</sup>C protocol for the DAC 3560C (MSB first; data must be stable while clock is high)

## **Abbreviations:**

A = Acknowledge

N = Not Acknowledge (NAK)

S = Start

P = Stop

$DW = I^2C$  Device Write Address (9A<sub>hex</sub>)

$DR = I^2C$  Device Read Address (9B<sub>hex</sub>)

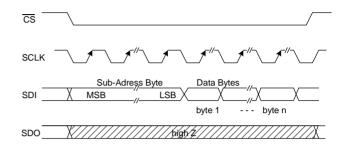

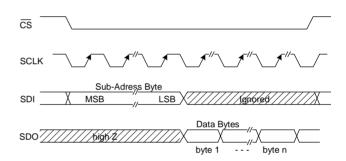

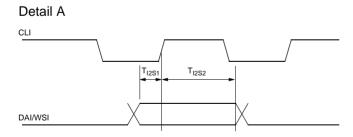

#### 2.6. SPI Bus Interface

The SPI bus is a 4-wire serial communications interface. Unlike the I<sup>2</sup>C bus, the SPI uses two separate pins for input and output and CS signal instead of individual device addresses.

Read and write starts with a low signal at  $\overline{CS}$ . The first byte is always interpreted as sub-address byte, which

contains the Register address. The following byte or bytes are then read/write register data.

If more than one data byte appears without changing CS, the register address will be incremented automatically at each data byte.

Fig. 2-4: SPI Control Port - Write Access

Fig. 2-5: SPI Control Port - Read Access

## 2.7. Noise Shaper and Multibit DAC

The input signal is interpolated to a higher sampling rate. A successive noise shaper converts the oversampled audio signal into a multibit noise-shaped signal. This technique results in extremely low quantization noise in the audio band.

## 2.8. Analog Low-Pass

The analog low-pass follows the multibit DAC and is a third order low pass filter with approximately 70 kHz cut-off frequency. It removes the out-of-band components of the oversampled audio signal.

## 2.9. Analog Input

In addition to the digital audio input, the DAC 3560C provides three analog inputs, (AUXL, AUXR, AIN) for stereo and mono signals. The analog audio signals can be mixed to the digital audio signal as well as being used without digital audio. All three analog inputs are equipped with 20 dB to –20 dB gain controls for individual input level adjustments in steps of 2 dB.

#### 2.10. Analog Audio Driver Output

The device provides three integrated audio drivers.

Table 2-5: Analog Audio Driver Output

| Integrated Audio Drivers   |                                               |  |  |

|----------------------------|-----------------------------------------------|--|--|

| Stereo headphone driver    | 25 mW at 2.85 V supply<br>80 mW at 5 V supply |  |  |

| Mono earpiece driver       | 100 mW at 2.85 V supply 300 mW at 5 V supply  |  |  |

| Mono loudspeaker<br>driver | 400 mW at 3 V supply 1.1 W at 5 V supply      |  |  |

All drivers are equipped with analog volume controls, which are individually adjustable from 6 dB to -30 dB in 1.5 dB steps. The earpiece driver and the loud-speaker driver have differential outputs, while the headphone drivers are single-ended. Single-ended drivers usually require a large coupling capacitor to block the DC bias from the headphone. The DAC 3560C provides a headphone common output (HPCM), which eliminates the need for such bulky DC-blocking capacitors. All driver outputs are short-circuit-protected.

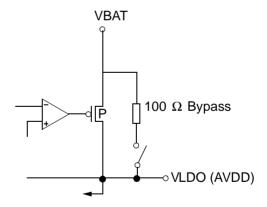

#### 2.11. LDO

For applications with a noise-critical power supply environment, the DAC 3560C is equipped with an integrated Low-Dropout Voltage Regulator (LDO). The LDO provides a stable 2.85 V output voltage and is intended to supply the headphone and earpiece drivers. With the LDO, the Power Supply Rejection Ratio (PSRR) of the audio outputs is improved to more than 100 dB.

For applications where the LDO cannot be used, e.g., for supply voltages below 2.85 V, it can be disabled via the Mode-Control-Register, (see Section 5.) for details on using the DAC 3560C with or without the internal LDO. The LDO is short-circuit-protected.

## 2.12. Charge Pump

The DAC 3560C offers an internal charge pump circuit that allows to operate the IC with a supply voltage as low as 2.2 V. An additional capacitor must be connected between pin PVDD and pin VLDO for the charge pump to work properly. The switching frequency is far above the audio range and therefore does not interfere with the audio signals. The charge

pump must be turned on if the supply voltage of the IC drops below 2.7 V. (see Section 5.) for details on using the DAC 3560C with a lowered supply voltage of 2.2 V.

#### 2.13. Reference Block

This block provides the reference level for the analog audio signals. Two modes are possible:

**LDO-Mode:** The audio reference level is fixed to 1.425 V (Pin SREF), which is one half of the LDO output voltage.

**Non-LDO-Mode:** The audio reference level at Pin SREF is derived from an internal voltage divider to VBAT/2.

A capacitor connected between SREF and SGND reduces the noise coming from SREF. In addition, a second capacitor can be connected to pin CF to form a second order noise filter. (See Section 5. for details).

## 2.14. Temperature Overload Protection

The DAC 3560C has an internal temperature overload protection, which disables all audio drivers and the LDO, if the junction temperature exceeds 140 °C. Once the chip has cooled down to 120 °C, the LDO and the audio drivers are enabled again.

#### 2.15. Power Management

As the device has more than one signal path, the DAC 3560C offers a Block-Control-Register, which permits individual control over the power state of the signal chain for optimized power consumption. A zero power and a stand-by mode are also provided.

## 2.16. Click and Pop Suppression

The DAC 3560C has on-chip facilities allowing to turn the audio output drivers on or off without audible click and pop transients.

## 3. Control Registers

The DAC 3560C contains 11 registers (all 8 bits). All registers, with the exception of the Reset Register, (write only), allow read and write access.

**Note:** The default value for all registers after software or hardware reset is 0.

## 3.1. Register Map

Table 3-1: Register Map Table

| Sub-Address | Register                                    |

|-------------|---------------------------------------------|

| 00h         | Reset Register                              |

| 01h         | Block Control Register                      |

| 02h         | Mode Control Register                       |

| 03h         | I <sup>2</sup> S-Interface Control Register |

| 04h         | Left Headphone Volume Control               |

| 05h         | Right Headphone Volume Control              |

| 06h         | Earpiece Volume Control                     |

| 07h         | Loudspeaker Volume Control                  |

| 08h         | Left Input Aux Gain Control                 |

| 09h         | Right Input Aux Gain Control                |

| 0Ah         | Ain Input Gain Control                      |

| 0BhFFh      | Reserved                                    |

Table 3–2: Register Description

| Name                      | Sub-Address | Dir | Default<br>after<br>Reset | Function                                                                            |  |  |  |  |  |

|---------------------------|-------------|-----|---------------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| DACC-Register             |             |     |                           |                                                                                     |  |  |  |  |  |

| Reset Register            | h00         | w   | h00                       |                                                                                     |  |  |  |  |  |

| Reset                     | h0X         | W   | 0                         | Writing to this Register clears all internal registers to their default reset value |  |  |  |  |  |

| Block Control<br>Register | h01         | RW  | h00                       | Ignored, if in Standby or Zero Power Mode                                           |  |  |  |  |  |

| PDAC                      | h01[7]      | RW  | 0                         | 1 = On, 0 = Off (Power DAC)                                                         |  |  |  |  |  |

| PAIN                      | h01[6]      | RW  | 0                         | 1 = On, 0 = Off (Power Ain) Gain                                                    |  |  |  |  |  |

| PAUX                      | h01[5]      | RW  | 0                         | 1 = On, 0 = Off (Power Aux) Gain                                                    |  |  |  |  |  |

| PL                        | h01[4]      | RW  | 0                         | 1 = On, 0 = Off (Power Loudspeaker) Driver                                          |  |  |  |  |  |

| PE                        | h01[3]      | RW  | 0                         | 1 = On, 0 = Off (Power Earpiece) Driver                                             |  |  |  |  |  |

| PRH                       | h01[2]      | RW  | 0                         | 1 = On, 0 = Off (Power Right Headphone) Driver                                      |  |  |  |  |  |

| PLH                       | h01[1]      | RW  | 0                         | 1 = On, 0 = Off (Power Left Headphone) Driver                                       |  |  |  |  |  |

| ENHPC                     | h01[0]      | RW  | 0                         | 1 = On, 0 = Off (Enable Headphone Common Output) Driver                             |  |  |  |  |  |

| Mode Control<br>Register  | h02         | RW  | h00                       | For details, please refer to Section 5.                                             |  |  |  |  |  |

| _                         | h02[7]      | RW  | 0                         | Reserved                                                                            |  |  |  |  |  |

| RDWN                      | h02[6]      | RW  | 0                         | 1 = On, 0 = Off (Ramp down SREF during Stand-<br>by Mode)                           |  |  |  |  |  |

| CPON                      | h02[5]      | RW  | 0                         | 1 = On, 0 = Off (Charge pump on (only in NON-LDO Mode)                              |  |  |  |  |  |

| BYPLDO                    | h02[4]      | RW  | 0                         | 1 = On, 0 = Off (Bypass LDO (only in Standby, Zero Power)                           |  |  |  |  |  |

| SNLDOM                    | h02[3]      | RW  | 0                         | 1 = On, 0 = Off (Select Non-LDO Mode)                                               |  |  |  |  |  |

| SMM                       | h02[2]      | RW  | 0                         | 1 = Mono, 0 = Stereo (Select Stereo or Mono<br>Mode)                                |  |  |  |  |  |

| PM                        | h02[1:0]    | RW  | 0                         | PM[1:0] 00 Zero Power Mode 01 Standby Mode 11 Operating Mode 10 Reserved            |  |  |  |  |  |

Table 3-2: Register Description, continued

| Name                                     | Sub-Address | Dir | Default<br>after<br>Reset | Function                                                                                                                                                                                                                                            |

|------------------------------------------|-------------|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2S Interface<br>Control<br>Register     | h03         | RW  | h00                       |                                                                                                                                                                                                                                                     |

| _                                        | h03[7:5]    | RW  | 0                         | Reserved                                                                                                                                                                                                                                            |

| POL                                      | h03[4]      | RW  | 0                         | Invert Polarity of Word Strobe Input  POL=0 - Left Channel → WSI=0  POL=1 - Right Channel → WSI=0                                                                                                                                                   |

| DEL                                      | h03[3]      | RW  | 0                         | 1 = Delay, 0 = no Delay (Delay Bit)                                                                                                                                                                                                                 |

| SR                                       | h03[2:0]    | RW  | 0                         | SR[2:0] 000 32 kHz - 48 kHz Sample Rate 001 24 kHz - 32 kHz Sample Rate 010 16 kHz - 24 kHz Sample Rate 011 12 kHz - 16 kHz Sample Rate 100 8 kHz - 12 kHz Sample Rate 101 6 kHz - 8 kHz Sample Rate 110 96 kHz Sample Rate 111 192 kHz Sample Rate |

| Left<br>Headphone<br>Volume<br>Register  | h04         | RW  | h00                       |                                                                                                                                                                                                                                                     |

| _                                        | h04[7:5]    | RW  | 0                         | Reserved                                                                                                                                                                                                                                            |

| LHV                                      | h04[4:0]    | RW  | 0                         | LHV[4:0] Left Headphone Volume  00000 Mute 00001 -30 dB in steps of 1.5 dB 11001 6 dB 11011-11111 6 dB                                                                                                                                              |

| Right<br>Headphone<br>Volume<br>Register | h05         | RW  | h00                       |                                                                                                                                                                                                                                                     |

| _                                        | h05[7:5]    | RW  | 0                         | Reserved                                                                                                                                                                                                                                            |

| RHV                                      | h05[4:0]    | RW  | 0                         | RHV[4:0] Right Headphone Volume 00000 Mute 00001 -30 dB in steps of 1.5 dB 11001 6 dB 11011-11111 6 dB                                                                                                                                              |

Table 3-2: Register Description, continued

| Name                              | Sub-Address | Dir | Default<br>after<br>Reset | Function                                                                                                     |

|-----------------------------------|-------------|-----|---------------------------|--------------------------------------------------------------------------------------------------------------|

| Earpiece<br>Volume<br>Register    | h06         | RW  | h00                       |                                                                                                              |

| -                                 | h06[7:5]    | RW  | 0                         | Reserved                                                                                                     |

| EV                                | h06[4:0]    | RW  | 0                         | EV[4:0] Earpiece Volume 00000 Mute 00001 -30 dB in steps of 1.5 dB 11001 6 dB 11011-11111 6 dB               |

| Loudspeaker<br>Volume<br>Register | h07         | RW  | h00                       |                                                                                                              |

| -                                 | h07[7:5]    | RW  | 0                         | Reserved                                                                                                     |

| LV                                | h07[4:0]    | RW  | 0                         | LV[4:0] Loudspeaker Volume  00000 Mute 00001 -30 dB in steps of 1.5 dB 11001 6 dB 11011-11111 6 dB           |

| Left Aux Gain<br>Register         | h08         | RW  | h00                       |                                                                                                              |

| _                                 | h08[7:5]    | RW  | 0                         | Reserved                                                                                                     |

| ALV                               | h08[4:0]    | RW  | 0                         | ALV[4:0] Left AUX Pre-Amplifier Gain 00000 Mute 00001 –20 dB in steps of 2 dB 10101 20 dB 10110-11111 20 dB  |

| Right AUX<br>Gain Register        | h09[7:5]    | RW  | h00                       |                                                                                                              |

| _                                 | h09[7:5]    | RW  | 0                         | Reserved                                                                                                     |

| ARV                               | h09[4:0]    | RW  | 0                         | ARV[4:0] Right AUX Pre-Amplifier Gain 00000 Mute 00001 –20 dB in steps of 2 dB 10101 20 dB 10110-11111 20 dB |

Table 3–2: Register Description, continued

| Name                 | Sub-Address | Dir | Default<br>after<br>Reset | Function                                                                                               |

|----------------------|-------------|-----|---------------------------|--------------------------------------------------------------------------------------------------------|

| AIN Gain<br>Register | h0A[7:5]    | RW  | h00                       |                                                                                                        |

| _                    | h0A[7:5]    | RW  | 0                         | Reserved                                                                                               |

| AIV                  | h0A[4:0]    | RW  | 0                         | AIV[4:0] AIN Pre-Amplifier Gain 00000 Mute 00001 -20 dB in steps of 2 dB 10101 20 dB 10110-11111 20 dB |

## 4. Specifications

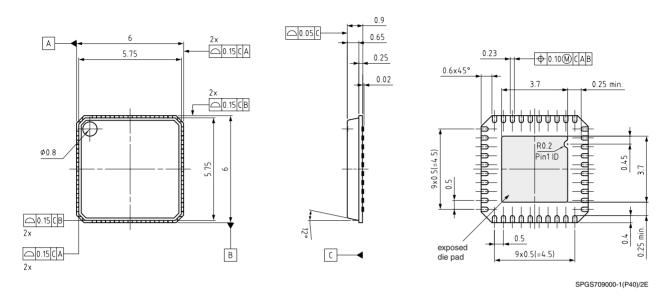

## 4.1. Outline Dimensions

Fig. 4–1: 40-Pin Plastic Quad Flat No leads package (PQFN40) Weight approximately 0.096 g Dimensions in mm

## 4.2. Pin Connections and Short Descriptions

NC = not connected LV = leave vacant I = Input, O = Output, I/O = Input/Output P = Power GND = Ground OBL = obligatory; connect as described in the circuit diagram

| Pin No.<br>PQFN<br>40-pin | Pin Name | Туре | Connection<br>(If not used) | Short Description                             |

|---------------------------|----------|------|-----------------------------|-----------------------------------------------|

| 1                         | VBAT     | Р    | -                           | Power Supply                                  |

| 2                         | LSVSS1   | Р    | GND                         | Loudspeaker Driver Ground                     |

| 3                         | LSP      | 0    | LV                          | Loudspeaker Differential Positive Output      |

| 4                         | LSVDD    | Р    | VBAT                        | Loudspeaker Power Supply Driver               |

| 5                         | LSN      | 0    | LV                          | Loudspeaker Differential Negative Output      |

| 6                         | LSVSS2   | Р    | GND                         | Loudspeaker Driver Ground                     |

| 7                         | DVDD     | Р    | -                           | Digital Power Supply                          |

| 8                         | DVSS     | Р    | GND                         | Digital Ground                                |

| 9                         | MODE     | I    | OBL                         | I <sup>2</sup> C / SPI Control Mode Selection |

| 10                        | IOVDD    | Р    | -                           | Digital I/O Power Supply                      |

| 11                        | SDI      | I/O  | OBL                         | SPI / Data In (I <sup>2</sup> C Data In/Out)  |

| 12                        | SCLK     | 1    | OBL                         | SPI / I <sup>2</sup> C CLK                    |

| 13                        | SDO      | 0    | LV                          | SPI / Data Out                                |

| 14                        | CS       | 1    | IOVDD                       | SPI Chip Select (active Low)                  |

| 15                        | DAI      | I    | GND                         | I <sup>2</sup> S Data In                      |

| 16                        | WSI      | I    | GND                         | I <sup>2</sup> S Word Strobe Input            |

| 17                        | CLI      | I    | GND                         | I <sup>2</sup> S Clock In                     |

| 18                        | RES      | I    | OBL                         | Reset Input (active Low)                      |

| 19                        | NC       |      | NC                          |                                               |

| 20                        | NC       |      | NC                          |                                               |

| 21                        | AIN      | I    | LV                          | Analog Mono Input                             |

| 22                        | AUXL     | I    | LV                          | Analog AUX Input Left Channel                 |

| 23                        | AUXR     | I    | LV                          | Analog AUX Input Right Channel                |

| 24                        | НРСМ     | 0    | LV                          | Headphone Common Output                       |

| 25                        | HPVSS    | Р    | GND                         | Headphone Driver Ground                       |

| 26                        | HPL      | 0    | LV                          | Headphone Output Left Channel                 |

| 27                        | HPR      | 0    | LV                          | Headphone Output Right Channel                |

| 28                        | HPVDD    | Р    | VLDO                        | Headphone Driver Power Supply                 |

| Pin No.<br>PQFN<br>40-pin | Pin Name    | Туре | Connection<br>(If not used) | Short Description                                       |

|---------------------------|-------------|------|-----------------------------|---------------------------------------------------------|

| 29                        | SGND        | Р    | GND                         | Ground for Audio Signal reference level, Connect to GND |

| 30                        | SREF        | 0    | OBL                         | Audio Signal reference level                            |

| 31                        | CF          | 0    | SREF                        | Audio Signal reference level                            |

| 32                        | EPVSS2      | Р    | GND                         | Earpiece Driver Supply Return, Connect to GND           |

| 33                        | EPN         | 0    | LV                          | Earpiece Differential Negative Output                   |

| 34                        | EPVDD       | Р    | VLDO                        | Earpiece Driver Power Supply                            |

| 35                        | EPP         | 0    | LV                          | Earpiece Differential Positive Output                   |

| 36                        | EPVSS1      | Р    | GND                         | Earpiece Driver Ground                                  |

| 37                        | AVSS        | Р    | GND                         | Analog Ground                                           |

| 38                        | PVDD        | 0    | VLDO                        | Charge Pump Out                                         |

| 39                        | CPIN        | Р    | OBL                         | Charge Pump In                                          |

| 40                        | VLDO (AVDD) | Р    | VBAT                        | LDO Output, Analog Power Supply                         |

Note: Pins CPIN, EPVDD and HPVDD must be connected to Pin VLDO

## 4.3. Pin Descriptions

## 4.3.1. Power Supply Pins

The power supply pins are divided into functional regions: LDO region, digital region, digital input region, three analog regions. Two major applications are possible: LDO mode or Non-LDO mode. They are described in detail in Section 5.1. and Section 5.2.

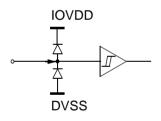

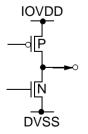

## DVDD, IOVDD, DVSS (see Fig. 4–8, Fig. 4–9, Fig. 4–10):

- The DVDD and DVSS power supply pair is connected internally with all digital parts of the DAC 3560C.

- The IOVDD and DVSS power supply pair is connected internally with all digital inputs and outputs of the DAC 3560C.

- DVSS is the ground connection for all digital circuits.

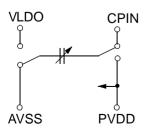

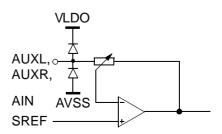

## AVSS, PVDD, CPIN (see Fig. 4–3): VBAT, VLDO (see Fig. 4–4):

VBAT is the input of the internal LDO. VLDO is the output of the LDO. If the LDO function is not used, VBAT must be connected to VLDO. At PVDD an internal supply can be generated. Pin CPIN must be connected to VLDO. This function is necessary in Non-LDO mode and external power voltages below 2.7 V. At these low supply voltages, an internal charge pump ensures proper functioning of the chip down to 2.2 V. An external capacitor of 47 nF must be connected from PVDD to VLDO. AVSS serves as ground pin for the aforementioned capacitor and must be connected to DVSS.

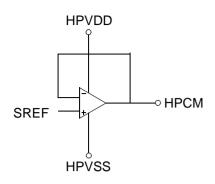

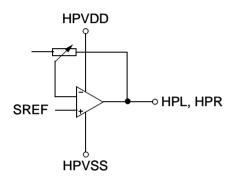

## HPVDD, HPVSS (see Fig. 4-6, Fig. 4-7)

The HPVDD and HPVSS pins supply the headphone drivers. HPVDD must be connected to VLDO. HPVSS must be connected to AVSS.

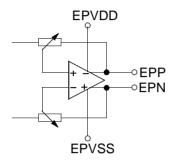

## EPVDD, EPVSS (see Fig. 4-11)

The EPVDD and EPVSS pins supply the earpiece drivers. EPVDD must be connected to VLDO. EPVSS must be connected to AVSS.

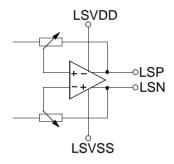

## LSVDD, LSVSS (see Fig. 4-12)

The LSVDD and LSVSS pins supply the loudspeaker drivers. LSVDD must be connected to VBAT. LSVSS must be connected to AVSS.

#### 4.3.2. Analog Reference Pins

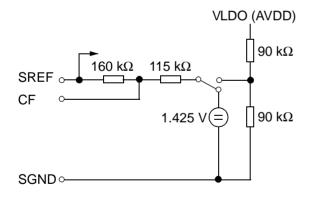

## SREF, CF (see Fig. 4-2):

Reference for analog audio signals. SREF is used as reference for the internal op amps and drivers. There are two modes of usage:

1) LDO mode:

SREF must be blocked against SGND with a 3.3 µF (plus optional 10 nF) capacitor.

CF must be connected to SREF.

The internal reference is fixed at 1.425 V.

- 2) Non-LDO mode (ratiometric mode):

- a) SREF and CF are connected together. Both are blocked against SGND with a 3.3 µF (+ optional 10 nF capacitor). The PSRR of SREF is reduced compared to the Bandgap mode.

- b) SREF is blocked against SGND with a 1 µF (+ optional 10 nF) capacitor and CF is blocked with a 1.0 µF capacitor. PSRR is improved with respect to

The internal reference is VLDO/2.

Note: SREF can be used as reference input for external op amps, if no current load is applied. Keep the traces at SREF and CF as short as possible to avoid system noise pickup.

## SGND (see Fig. 4-2):

Reference ground for the internal bandgap and biasing circuits. This pin should be connected to a clean ground potential. Any external distortions on this pin will affect the analog performance of the DAC 3560C. SGND must be connected to AVSS.

## 4.3.3. Analog Audio Pins

## AUXL, AUXR, AIN (see Fig. 4-5):

These pins provide analog stereo/mono inputs. Auxiliary input signals, e.g. the output of a conventional receiver circuit or the output of a tape recorder can be connected here.

The input gain is programmable between -20 dB and +20 dB in steps of 2 dB.

The input signals have to be connected by capacitive

Each signal can be mixed to the output of the embedded DAC.

## HPL, HPR, HPCM (see Fig. 4-6, Fig. 4-7):

The HPL/R pins are connected to the internal headphone drivers. They can be used for single-ended stereo headphones of greater or equal than 16 Ohm. There are two modes of applying the load:

1) Load to ground: Each channel must be coupled capacitively.

2) Load to HPCM: Channels can be coupled directly to HPCM. The common mode buffer at HPCM must be enabled before activating the drivers.

## **EPP**, **EPN** (see Fig. 4–11):

The EPP/N pins are connected to the internal earpiece driver. They can be used for differential mono earpiece speakers of greater than, or equal to, 16 Ohm.

## LSP, LSN (see Fig. 4-12):

The LSP/N pins are connected to the internal loudspeaker driver. They can be used for differential mono loudspeakers of greater or equal than 4 Ohm.

All analog outputs show a programmable gain range of -30 dB to +6 dB plus Mute.

Note: Any occurrence of a short circuit at these pins may result in initialization of the built-in temperature protection unit, which turns off the output drivers. When the short-circuit condition is removed, the drivers will be turned on again.

#### 4.3.4. Digital Audio Input Pins

#### CLI, DAI, WSI (see Fig. 4-8):

These three pins are inputs for the digital audio data DAI, frame indication signal WSI, and bit clock CLI. The digital audio data is transmitted in an I<sup>2</sup>S-compatible format. Audio word lengths of 16 and 32 bits are supported, as well as SONY and Philips I<sup>2</sup>S protocol.

#### 4.3.5. Control Interface Pins

## SCLK, SDI, SDO, MODE, CS (see Fig. 4-8, Fig. 4-9, Fig. 4-10):

Two protocol control modes are possible:

#### 1) I<sup>2</sup>C mode:

SCLK and SDI provide the connection to the serial control interface.

#### 2) SPI mode:

Two additional signals are needed: CS serves as the interface chip select.

SDO sends out data after a read command.

MODE toggles between the two control modes.

## 4.3.6. Other Pins

#### **RES** (see Fig. 4-8):

This pin may be used to reset the chip. After power-up it should be raised from DVSS potential to IOVDD level. Signal function is active low.

## 4.4. Pin Configurations

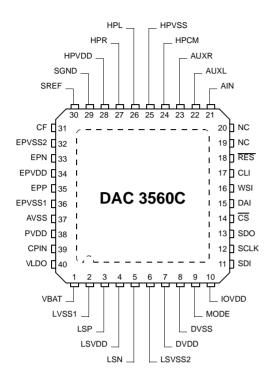

Fig. 4-2: PQFN40 package

## 4.5. Pin Circuits

Fig. 4-3: Reference Pins: SREF, CF, SGND, VLDO

Fig. 4-4: Supply Pins: CPIN, PVDD

Fig. 4-5: Supply Pins: VLDO, VBAT

Fig. 4-6: Input Pins: AUXL, AUXR, AIN

Fig. 4-7: Output Pin: HPCM

Fig. 4-8: Output Pins: HPL, HPR

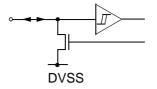

Fig. 4-9: Input Pins: Mode, CS, DAI, WSI, CLI, RES

Fig. 4-10: Output Pin: SDO

Fig. 4-11: In/Out Pins: SDI, SCLK

Fig. 4-12: Output Pins: EPP, EPN, EPVDD, EPVSS

Fig. 4-13: Output Pins: LSP, LSN, LSVDD, LSVSS

#### 4.6. Electrical Characteristics

## 4.6.1. Absolute Maximum Ratings

| Symbol            | Parameter                                                               | Pin Name                                                    | Min.       | Max.       | Unit |

|-------------------|-------------------------------------------------------------------------|-------------------------------------------------------------|------------|------------|------|

| V <sub>SUP</sub>  | Supply Voltage                                                          | VBAT, LSVDD,<br>VLDO, HPVDD,<br>EPVDD, CPIN,<br>DVDD, IOVDD | -0.3       | 6          | V    |

| V <sub>Iana</sub> | Analog Input Voltages                                                   | AIN, AUXL,<br>AUXR, SREF,<br>CF                             | -0.3       | VLDO+0.3   | V    |

| V <sub>Idig</sub> | Digital Input Voltages                                                  | MODE, SDO,<br>SDI, SCLK, CS,<br>DAI, WSI, CLI,<br>RES       | -0.3       | IOVDD+0.3  | V    |

| V <sub>II2C</sub> |                                                                         | SDI, SCLK                                                   | -0.3       | 6          | V    |

| I <sub>Iana</sub> | Analog Input Currents                                                   | AIN, AUXL,<br>AUXR, SREF,<br>CF                             | -5         | 5          | mA   |

| I <sub>Idig</sub> | Digital Input Currents                                                  | MODE, SDO,<br>SDI, SCLK, CS,<br>DAI, WSI, CLI,<br>RES       | -5         | 5          | mA   |

| l <sub>Odig</sub> | Digital Output Currents                                                 | SDO, SDI,<br>SCLK                                           | -50        | 50         | mA   |

| I <sub>OLDO</sub> | Analog Output Currents                                                  | LDO                                                         | internally | 50         | mA   |

| I <sub>OHP</sub>  |                                                                         | HPL, HPR,<br>HPCM                                           | limited    | internally | mA   |

| I <sub>OEP</sub>  |                                                                         | EPN, EPP                                                    |            | limited    |      |

| I <sub>OLS</sub>  |                                                                         | LSP, LSN                                                    |            |            |      |

| T <sub>S</sub>    | Storage Temperature                                                     |                                                             | -40        | 125        | °C   |

| T <sub>J</sub>    | Junction Temperature                                                    |                                                             | -40        | 125        | °C   |

| Ртот              | Continuous Power Dissipation at TA = 85 °C, exposed pad soldered to PCB |                                                             |            | 1          | W    |

Stresses beyond those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions/Characteristics" of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

Note: Positive currents flow into the device

## 4.6.2. Recommended Operating Conditions

| Symbol              | Parameter                                                       | Pin Name                                    | Min.     | Тур. | Max.     | Unit     |

|---------------------|-----------------------------------------------------------------|---------------------------------------------|----------|------|----------|----------|

| T <sub>A</sub>      | Ambient Operating Temperature                                   |                                             |          |      |          |          |

|                     | -Operating Conditions -Extended Temperature Range <sup>1)</sup> |                                             | 0<br>-40 |      | 85<br>85 | °C<br>°C |

| V <sub>SUPA1</sub>  | Analog Supply Voltage<br>(Non-LDO mode)<br>Charge pump: on      | VBAT, LSVDD,<br>VLDO, HPVDD,<br>EPVDD, CPIN | 2.2      |      | 3.4      | V        |

|                     | Analog Supply Voltage<br>(Non-LDO mode)                         |                                             | 2.7      |      | 5.5      | V        |

|                     | Charge pump: off                                                |                                             |          |      |          |          |

| V <sub>SUPA2</sub>  | Analog Supply Voltage (LDO mode)                                | VBAT, LSVDD                                 | 3        |      | 5.5      | V        |

| V <sub>SUPD</sub>   | Digital Supply Voltage                                          | DVDD                                        | 2.2      |      | 5.5      | V        |

| V <sub>SUPIO</sub>  | Digital Interface Voltage                                       | IOVDD                                       | 1.8      |      | 5.5      | V        |

| C <sub>LDOout</sub> | LDO Output Capacitor                                            | VLDO, use<br>Ceramic X7R,<br>X5R            | 0.8      | 1.0  | 1.3      | μF       |

| C <sub>LDOin</sub>  | LDO Input Capacitor                                             | VBAT                                        | 0.47     |      |          | μF       |

| C <sub>Pout</sub>   | Charge Pump Output Capacitor                                    | PVDD, VLDO                                  |          | 47   |          | nF       |

| C <sub>Ain</sub>    | Analog Input Coupling Capacitor                                 | AUXL, AUXR,<br>AIN                          | 470      |      |          | nF       |

| C <sub>Sref</sub>   | SREF Bypass Capacitor                                           | SREF                                        | 3.3      |      |          | μF       |

| R <sub>LHP</sub>    | Headphone Load Resistance                                       | HPL, HPR,<br>HPCM                           | 16       | 32   |          | Ω        |

| R <sub>LEP</sub>    | Earpiece Load Resistance                                        | EPP, EPN                                    | 16       | 32   |          | Ω        |

| R <sub>LS</sub>     | Loudspeaker Load Resistance                                     | LSP, LSN                                    | 4        | 8    |          | Ω        |

<sup>&</sup>lt;sup>1)</sup> The functionality of the device in the "Extended Temperature Range" was checked by electrical characterization on sample base. Data sheet parameters are valid for "operating conditions" only.

## 4.6.3. Characteristics (LDO Mode)

Unless noted otherwise: LSVDD = VBAT = 3.6 V, EPVDD = HPVDD = CPIN = PVDD = VLDO = 2.85 V (LDO-mode),  $T_A = 0$  °C ...85 °C. Typical values are at  $T_A = 25$  °C.

| Symbol                             | Parameter                                 | Pin Name                             | Min.   | Тур.     | Max. | Unit            | Test Conditions                                                |

|------------------------------------|-------------------------------------------|--------------------------------------|--------|----------|------|-----------------|----------------------------------------------------------------|

| POWER MA                           | ANAGEMENT, LDO                            |                                      | •      | •        |      | •               | •                                                              |

| $V_{LDO}$                          | LDO Output Voltage in<br>Operational Mode | VLDO                                 | 2.75   | 2.85     | 2.95 | V               | no load connected                                              |

| $V_{LDO}$                          | LDO Output Voltage in Standby Mode        | VLDO                                 | 2.75   | 2.85     | 2.95 | V               | LDO not bypassed, no load connected                            |

|                                    |                                           |                                      |        | VBAT     |      | V               | LDO bypassed with internal 100Ω switch, no load connected      |

| V <sub>LDO</sub>                   | LDO Output Voltage in Zero Power Mode     | VLDO                                 |        | HIGH-Z   |      | ٧               | LDO not bypassed                                               |

|                                    | Zero Power Mode                           |                                      |        | VBAT     |      | V               | LDO bypassed with internal 100Ω switch, no load connected      |

| I <sub>LDO</sub>                   | LDO Output Current                        | VLDO                                 |        |          | 260  | mA              |                                                                |

| $V_{Drop}$                         | LDO Drop Out Voltage                      | VBAT, VLDO                           |        | 70       |      | mV              | I <sub>load</sub> = 100 mA                                     |

| I <sub>Short</sub>                 | LDO Short Circuit Current                 | VLDO                                 |        | 650      |      | mA              | VLDO = 0V, Standby or<br>Operational Mode, LDO not<br>bypassed |

| I <sub>SupTot</sub> Supply Current | Supply Current                            | VBAT, LSVDD,<br>VLDO, EPVDD,         |        |          | 10   | μΑ              | Zero Power Mode                                                |

|                                    |                                           | HPVDD, CPIN,<br>PVDD, IOVDD,<br>DVDD |        | 170      |      | μА              | Standby Mode, LDO<br>bypassed, HPCM-Output<br>enabled          |

|                                    |                                           |                                      |        | 350      |      | μА              | Standby Mode, LDO<br>bypassed, HPCM-Output off                 |

|                                    |                                           |                                      |        | 450      |      | μА              | Standby Mode, LDO on,<br>HPCM-Output enabled                   |

|                                    |                                           |                                      |        | 620      |      | μА              | Standby Mode, LDO on,<br>HPCM-Output off                       |

|                                    |                                           |                                      | See Ta | ble 4–1. |      |                 | Operational Mode                                               |

| $T_TS$                             | Thermal Shutdown Temperature              |                                      | 125    | 140      | 160  | °C              |                                                                |

| H <sub>TS</sub>                    | Thermal Shutdown Hysteresis               |                                      |        | 20       |      | °C              |                                                                |

| ANALOG A                           | UDIO INPUTS - AIN, AUXL, AUXR             |                                      |        |          |      |                 |                                                                |

| V <sub>AI1</sub>                   | 0 dB (Full Scale) Input Level             | AIN, AUXL,<br>AUXR                   |        | 2.04     |      | V <sub>pp</sub> | Gains set to 0 dB                                              |

| $V_{Al2}$                          | Input Clipping Level                      | AIN, AUXL,<br>AUXR                   |        | 2.85     |      | V <sub>pp</sub> | Gains set to -20 dB                                            |

| R <sub>I</sub>                     | Input Resistance                          | AIN, AUXL,                           | 9      | 12.5     | 15   | kΩ              | Gain = +20 dB                                                  |

|                                    |                                           | AUXR                                 | 57     | 69       | 83   |                 | Gain = 0 dB                                                    |

|                                    |                                           |                                      | 100    | 125      | 150  |                 | Gain = −20 dB                                                  |

| G <sub>AI</sub>                    | Gain Setting Range                        | AIN, AUXL,<br>AUXR                   | -20    |          | 20   | dB              |                                                                |

| d <sub>GAI</sub>                   | Gain Step Size                            | AIN, AUXL,<br>AUXR                   |        | ±2       |      | dB              |                                                                |

| Symbol                               | Parameter                                                                     | Pin Name                                                 | Min.  | Тур.       | Max. | Unit            | Test Conditions                                                    |

|--------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|-------|------------|------|-----------------|--------------------------------------------------------------------|

| E <sub>GAI</sub>                     | Gain Step Size Error                                                          | AIN, AUXL,<br>AUXR                                       | -0.5  |            | 0.5  | dB              |                                                                    |

| ANALOG AU                            | IDIO OUTPUTS – HEADPHONE, EA                                                  | RPIECE, LOUDSPI                                          | EAKER |            |      |                 |                                                                    |

| G <sub>AO</sub>                      | Volume Range                                                                  | HPL, HPR, EPP,<br>EPN, LSP, LSN                          | -30   |            | 6    | dB              |                                                                    |

| $dG_{AO}$                            | Volume Step Size                                                              | HPL, HPR, EPP,<br>EPN, LSP, LSN                          |       | ±1.5       |      | dB              |                                                                    |

| E <sub>GAO</sub>                     | Volume Step Size Error                                                        | HPL, HPR, EPP,<br>EPN, LSP, LSN                          | -0.5  |            | 0.5  | dB              |                                                                    |

| P <sub>HP</sub>                      | Headphone Output Power                                                        | HPL, HPR,<br>(HPCM)                                      |       | 25<br>(22) |      | mW              | THD < 0.1%, f=1 kHz, R <sub>L</sub> = 32 $\Omega$                  |

| P <sub>EP</sub>                      | Earpiece Output Power                                                         | EPP, EPN                                                 |       | 100        |      | mW              | THD < 0.2%, f=1 kHz,<br>R <sub>L</sub> = 32 $\Omega$ (one channel) |

| P <sub>LS</sub>                      | Loudspeaker Output Power                                                      | LSP, LSN                                                 |       | 410        |      | mW              | THD < 1%, f=1 kHz, $R_L$ = 8 $\Omega$                              |

| I <sub>HPshort</sub>                 | Headphone Short-circuit Current                                               | HPL, HPR,<br>HPCM, VLDO,<br>AVSS                         | 0.1   | 0.45       |      | A               | not tested                                                         |

| I <sub>EPshort</sub>                 | Earpiece Short-circuit<br>Current                                             | EPP, EPN,<br>VLDO, AVSS                                  | 0.15  | 0.5        |      | А               | not tested                                                         |

| I <sub>LSshort</sub>                 | Loudspeaker Short-circuit<br>Current                                          | LSP, LSN, VLDO,<br>AVSS                                  | 0.5   | 1.2        |      | A               | not tested                                                         |

| REFERENCE                            | ES                                                                            |                                                          |       |            |      |                 |                                                                    |

| V <sub>OREF1</sub>                   | Output Signal Reference Level                                                 | HPL, HPR,<br>HPCM, EPP,<br>EPN                           |       | 1.425      |      | V               | SREF settled                                                       |

| V <sub>OREF2</sub>                   | Output Signal Reference Level                                                 | LSP, LSN                                                 |       | 1.5        |      | ٧               | SREF settled                                                       |

| SIGNAL CHA                           | AINS – DYNAMIC PERFORMANCE                                                    |                                                          |       | 1          | 1    | •               | •                                                                  |

| Bandwidth =                          | kHz with 24-Bit data,<br>20 Hz20 kHz,<br>are unweighted, values in dBA are A- | weighted.                                                |       |            |      |                 |                                                                    |

| V <sub>AOHP</sub>                    | 0dB (full scale) Output Level<br>Headphone                                    | HPL, HPR                                                 |       | 2.04       |      | V <sub>pp</sub> | Gains, Volumes = 0 dB.<br>No load connected.                       |

| V <sub>AOEP</sub>                    | 0dB (full scale) Output Level<br>Earpiece                                     | EPP, EPN,                                                |       | 4.08       |      | V <sub>pp</sub> | Gains, Volumes = 0 dB.<br>No load connected.                       |

| V <sub>AOLS</sub>                    | 0dB (full scale) Output Level<br>Loudspeaker                                  | LSP, LSN                                                 |       | 4.08       |      | V <sub>pp</sub> | Gains, Volumes = 0 dB.<br>No load connected.                       |

| DR <sub>DA</sub><br>DR <sub>HP</sub> | Dynamic Range, Digital to Analog<br>Out                                       | HPL, HPR,<br>(HPCM) ,<br>EPP, EPN,                       |       | 98<br>94   |      | dBA<br>dB       | Digital to Headphone                                               |

| DR <sub>DA</sub><br>DR <sub>EP</sub> |                                                                               | LSP, LSN                                                 |       | 99<br>95   |      | dBA<br>dB       | Digital to Earpiece                                                |

| DR <sub>DA</sub><br>DR <sub>LS</sub> |                                                                               |                                                          |       | 99<br>95   |      | dBA<br>dB       | Digital to Loudspeaker                                             |

| DR <sub>AA</sub><br>DR <sub>HP</sub> | Dynamic Range, Analog to<br>Analog Out                                        | AIN, AUXL,<br>AUXR, HPL,<br>HPR, HPCM,<br>EPP, EPN, LSP, |       | 98<br>94   |      | dBA<br>dB       | Analog to Headphone, DAC off                                       |

| DR <sub>AA</sub><br>DR <sub>EP</sub> |                                                                               | LSN                                                      |       | 99<br>96   |      | dBA<br>dB       | Analog to Earpiece, DAC and headphone off                          |

| DR <sub>AA</sub><br>DR <sub>LS</sub> | 1                                                                             |                                                          |       | 98<br>96   |      | dBA<br>dB       | Analog to Loudspeaker, DAC and headphone off                       |

| Symbol             | Parameter  | Pin Name                                      | Min. | Тур.         | Max. | Unit | Test Conditions                                                                                                           |

|--------------------|------------|-----------------------------------------------|------|--------------|------|------|---------------------------------------------------------------------------------------------------------------------------|

| THD <sub>HP</sub>  | THD+N      | HPL, HPR,<br>(HPCM)                           |      | -76<br>(-68) |      | dB   | Headphone, $R_L = 32 \Omega$ , $P_{OUT} = 15 \text{ mW}$                                                                  |

| THD <sub>EP</sub>  |            | EPP, EPN                                      |      | -69          |      | dB   | Earpiece, $R_L = 32 \Omega$ , $P_{OUT} = 50 \text{ mW}$                                                                   |

| THD <sub>LS</sub>  |            | LSP, LSN                                      |      | -63          |      | dB   | Loudspeaker, $R_L = 8 \Omega$ , $P_{OUT} = 200 \text{ mW}$                                                                |

| LM                 | Mute Level | HPL, HPR,<br>(HPCM),<br>EPP, EPN, LSP,<br>LSN |      | -108         |      | dBV  | Headphone,<br>volumes muted,<br>Earpiece,<br>Loudspeaker                                                                  |

| PSRR <sub>HP</sub> | PSRR       | VBAT, HPL,<br>HPR, (HPCM)                     |      | 115          |      | dB   | Headphone, f = 1 kHz,<br>VBAT > 3 V, including<br>LDO-Isolation<br>V <sub>RIPPLE,peak</sub> = 0.25 V<br>Zero-Audio Signal |

| PSRR <sub>EP</sub> | PSRR       | VBAT, EPP, EPN                                |      | 105          |      | dB   | Earpiece, f = 1 kHz,<br>VBAT > 3 V, including<br>LDO-Isolation<br>V <sub>RIPPLE,peak</sub> = 0.25 V<br>Zero-Audio Signal  |

| PSRR <sub>LS</sub> | PSRR       | VBAT, LSP, LSN                                | tbd  | 93           |      | dB   | Loudspeaker,<br>f = 1 kHz, VBAT > 3 V<br>V <sub>RIPPLE,peak</sub> = 0.25 V<br>Zero-Audio Signal                           |

## 4.6.4. Characteristics (Non-LDO Mode)

Unless noted otherwise: LSVDD = VBAT = EPVDD = HPVDD = CPIN = VLDO = 2.2 V... 5.5 V (Non-LDO-mode),  $T_A = 0$  °C ...85 °C. Typical values are at  $T_A = 25$  °C.

| Symbol              | Parameter                                                                          | Pin Name                                     | Min.  | Тур.                          | Max. | Unit            | Test Conditions                                      |

|---------------------|------------------------------------------------------------------------------------|----------------------------------------------|-------|-------------------------------|------|-----------------|------------------------------------------------------|

| POWER MA            | ANAGEMENT, LDO                                                                     |                                              | •     | •                             |      | •               |                                                      |

| I <sub>SupTot</sub> | Supply Current at 2.2 V                                                            | VBAT, LSVDD,                                 |       |                               | 10   | μА              | Zero Power Mode                                      |

|                     |                                                                                    | VLDO, EPVDD,<br>HPVDD, CPIN,<br>PVDD, IOVDD, |       | 185                           |      | μА              | Standby Mode, HPCM-<br>Output enabled                |

|                     |                                                                                    | DVDD                                         |       | 355                           |      | μА              | Standby Mode, HPCM-<br>Output off                    |

|                     |                                                                                    |                                              |       |                               |      |                 |                                                      |

| I <sub>SupTot</sub> | Supply Current at 5 V                                                              | VBAT, LSVDD,<br>VLDO, EPVDD,                 |       |                               | 10   | μΑ              | Zero Power Mode                                      |

|                     |                                                                                    | HPVDD, CPIN, PVDD, IOVDD, DVDD               |       | 235                           |      | μА              | Standby Mode, HPCM-<br>Output enabled                |

|                     |                                                                                    | DVDD                                         |       | 420                           |      | μА              | Standby Mode, HPCM-<br>Output off                    |

|                     |                                                                                    |                                              |       |                               |      |                 |                                                      |

| ANALOG A            | UDIO INPUTS - AIN, AUXL, AUXR                                                      | T                                            | 1     | 1                             | 1    | 1               | T                                                    |

| V <sub>AI1</sub>    | 0 dB (Full Scale) Input Level                                                      | AIN, AUXL,<br>AUXR                           |       | 1.43 x<br>V <sub>LDO</sub> /2 |      | V <sub>pp</sub> | Gains set to 0 dB                                    |

| $V_{Al2}$           | Input Clipping Level                                                               | AIN, AUXL,<br>AUXR                           |       | V <sub>LDO</sub>              |      | V <sub>pp</sub> | Gains set to -20 dB                                  |

| ANALOG A            | UDIO OUTPUTS – HEADPHONE, EA                                                       | ARPIECE, LOUDSP                              | EAKER |                               | l    |                 |                                                      |

| P <sub>HP</sub>     | Headphone Output Power at 2.2 V                                                    | HPL, HPR,<br>(HPCM)                          |       | 12                            |      | mW              | THD < 0.1%, f=1 kHz,<br>R <sub>L</sub> = 32 $\Omega$ |

| P <sub>EP</sub>     | Earpiece Output Power at 2.2 V                                                     | EPP, EPN                                     |       | 50                            |      | mW              | THD < 0.2%, f=1 kHz, R <sub>L</sub> = $32 \Omega$    |

| P <sub>LS</sub>     | Loudspeaker Output Power at 2.2 V                                                  | LSP, LSN                                     |       | 170                           |      | mW              | THD < 1%, f=1 kHz, $R_L$ = 8 $\Omega$                |

| P <sub>HP</sub>     | Headphone Output Power at 5 V                                                      | HPL, HPR,<br>(HPCM)                          |       | 78                            |      | mW              | THD < 0.1%, f=1 kHz, R <sub>L</sub> = $32 \Omega$    |

| P <sub>EP</sub>     | Earpiece Output Power at 5 V                                                       | EPP, EPN                                     |       | 300                           |      | mW              | THD < 0.2%, f=1 kHz, R <sub>L</sub> = $32 \Omega$    |

| P <sub>LS</sub>     | Loudspeaker Output Power at 5 V                                                    | LSP, LSN                                     |       | 1.1                           |      | W               | THD < 1%, f=1 kHz, $R_L$ = 8 $\Omega$                |

| REFERENC            | CES                                                                                |                                              | •     |                               |      |                 | •                                                    |

| V <sub>OREF1</sub>  | Output Signal Reference Level                                                      | HPL, HPR,<br>HPCM, EPP,<br>EPN               |       | V <sub>LDO</sub> /2           |      | V               | SREF settled                                         |

| V <sub>OREF2</sub>  | Output Signal Reference Level                                                      | LSP, LSN                                     |       | V <sub>LDO</sub> /2           |      | V               | SREF settled                                         |

|                     | IAINS – DYNAMIC PERFORMANCE                                                        | 1                                            | 1     | 1                             | I .  | 1               |                                                      |

|                     | B kHz with 24-Bit data,<br>= 20 Hz20 kHz,<br>3 are unweighted, values in dBA are A | \-weighted.                                  |       |                               |      |                 |                                                      |

| V <sub>AOHP</sub>   | 0 dB (Full scale) Output Level<br>Headphone                                        | HPL, HPR                                     |       | 1.43 x<br>V <sub>LDO</sub> /2 |      | V <sub>pp</sub> | Gains, Volumes = 0 dB.<br>No load connected.         |

|                     | 1                                                                                  | 1                                            | 1     | 1                             | 1    | 1               | 1                                                    |

| Symbol                               | Parameter                                        | Pin Name                            | Min. | Тур.                          | Max.     | Unit            | Test Conditions                                                              |

|--------------------------------------|--------------------------------------------------|-------------------------------------|------|-------------------------------|----------|-----------------|------------------------------------------------------------------------------|

| V <sub>AOEP</sub>                    | 0 dB (Full scale) Output Level<br>Earpiece       | EPP, EPN,                           |      | 2.86 x<br>V <sub>LDO</sub> /2 |          | V <sub>pp</sub> | Gains, Volumes = 0 dB.<br>No load connected.                                 |

| V <sub>AOLS</sub>                    | 0 dB (Full scale) Output Level<br>Loudspeaker    | LSP, LSN                            |      | 2.86 x<br>V <sub>LDO</sub> /2 |          | V <sub>pp</sub> | Gains, Volumes = 0 dB.<br>No load connected.                                 |

| DR <sub>DA</sub><br>DR <sub>HP</sub> | Dynamic Range, Digital to Analog<br>Out at 2.2 V | HPL, HPR,<br>(HPCM),                |      | 96<br>93                      |          | dBA<br>dB       | Digital to Headphone                                                         |

| DR <sub>DA</sub><br>DR <sub>EP</sub> |                                                  | EPP, EPN,<br>LSP, LSN               |      | 98<br>94                      |          | dBA<br>dB       | Digital to Earpiece                                                          |

| DR <sub>DA</sub><br>DR <sub>LS</sub> |                                                  |                                     |      | 98<br>94                      |          | dBA<br>dB       | Digital to Loudspeaker                                                       |

| DR <sub>DA</sub><br>DR <sub>HP</sub> | Dynamic Range, Digital to Analog<br>Out at 5 V   | HPL, HPR,<br>(HPCM),                |      | 103<br>99                     |          | dBA<br>dB       | Digital to Headphone                                                         |

| DR <sub>DA</sub><br>DR <sub>EP</sub> |                                                  | EPP, EPN,<br>LSP, LSN               |      | 102<br>98                     |          | dBA<br>dB       | Digital to Earpiece                                                          |