# DAC1208, DAC1209, DAC1210, DAC1230, DAC1231, DAC1232

MICRO-DAC(TM) DAC1208 DAC1209 DAC1210 DAC1230 DAC1231 DAC1232 12-Bit, MuP Compatible, Double-Buffered D to A Converters

Literature Number: SNAS542A

# MICRO-DAC™ DAC1208/DAC1209/DAC1210/DAC1230/ DAC1231/DAC1232 12-Bit, μP Compatible, Double-Buffered D to A Converters

# **General Description**

The DAC1208 and the DAC1230 series are 12-bit multiplying D to A converters designed to interface directly with a wide variety of microprocessors (8080, 8048, 8085, Z-80, etc.). Double buffering input registers and associated control lines allow these DACs to appear as a two-byte "stack" in the system's memory or I/O space with no additional interfacing logic required.

The DAC1208 series provides all 12 input lines to allow single buffering for maximum throughput when used with 16-bit processors. These input lines can also be externally configured to permit an 8-bit data interface. The DAC1230 series can be used with an 8-bit data bus directly as it internally formulates the 12-bit DAC data from its 8 input lines. All of these DACs accept left-justified data from the processor.

The analog section is a precision silicon-chromium (Si-Cr) R-2R ladder network and twelve CMOS current switches. An inverted R-2R ladder structure is used with the binary weighted currents switched between the I<sub>OUT1</sub> and I<sub>OUT2</sub> maintaining a constant current in each ladder leg independent of the switch state. Special circuitry provides TTL logic input voltage level compatibility.

The DAC1208 series and DAC1230 series are the 12-bit members of a family of microprocessor compatible DACs (MICRO-DACsTM). For applications requiring other resolutions, the DAC1000 series for 10-bit and DAC0830 series for 8-bit are available alternatives.

#### **Features**

- Linearity specified with zero and full-scale adjust only

- Direct interface to all popular microprocessors

- Double-buffered, single-buffered or flow through digital data inputs

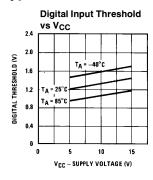

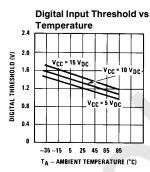

- Logic inputs which meet TTL voltage level specs (1.4V logic threshold)

- Works with ±10V reference—full 4-quadrant multiplication

- $\blacksquare$  Operates stand-alone (without  $\mu$ P) if desired

- All parts guaranteed 12-bit monotonic

- DAC1230 series is pin compatible with the DAC0830 series 8-bit MICRO-DACs

# **Key Specifications**

■ Current Settling Time

1 μs 12 Bits

Resolution

Linearity (Guaranteed over temperature)

10, 11, or 12 Bits of FS

■ Gain Tempco

1.3 ppm/°C 20 mW

Low Power DissipationSingle Power Supply

5  $V_{DC}$  to 15  $V_{DC}$

# **Typical Application**

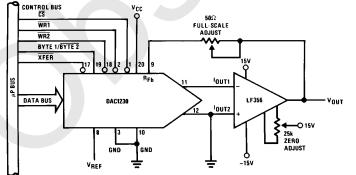

TL/H/5690-1

TRI-STATE® is a registered trademark of National Semiconductor Corp. MICRO-DAC™ is a trademark of National Semiconductor Corp.

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

(Notes 1 and 2)

Supply Voltage (V<sub>CC</sub>)

$17 \, V_{DC}$ Voltage at Any Digital Input  $\ensuremath{\text{V}_{\text{CC}}}$  to GND  $\pm\,25V$

Voltage at  $V_{\mbox{\scriptsize REF}}$  Input Storage Temperature Range -65°C to +150°C

Package Dissipation at T<sub>A</sub> = 25°C

(Note 3)

DC Voltage Applied to  $I_{\mbox{\scriptsize OUT1}}$  or  $I_{\mbox{\scriptsize OUT2}}$

$-\,100$  mV to  $V_{\hbox{\footnotesize CC}}$ (Note 4)

ESD Susceptability 800V

# **Operating Conditions**

Lead Temperature (Soldering, 10 sec.)

Temperature Range  $T_{MIN} \leq T_A \leq T_{MAX}$

DAC1208LCJ, DAC1209LCJ, DAC1210LCJ, DAC1230LCJ, DAC1231LCJ, DAC1232LCJ,

DAC1231LIN, DAC1232LIN  $-40^{\circ}C \leq T_{A} \leq \, +85^{\circ}C$

300°C

DAC1208LCJ-1, DAC1210LCJ-1, DAC1230LCJ-1, DAC1231LCJ-1, DAC1232LCJ-1, DAC1231LCN, DAC1232LCN, DAC1231LCWM,

$0^{\circ}C \leq T_{A} \leq \, \pm \, 70^{\circ}C$ DAC1232LCWM

Range of  $V_{CC}$ 4.75  $V_{DC}$  to 16  $V_{DC}$ Voltage at Any Digital Input V<sub>CC</sub> to GND

# **Electrical Characteristics**

$V_{REF}$  = 10.000  $V_{DC}$ ,  $V_{CC}$  = 11.4  $V_{DC}$  to 15.75  $V_{DC}$  unless otherwise noted. Boldface limits apply from  $T_{MIN}$  to  $T_{MAX}$  (see Note 13); all other limits  $T_A$  =  $T_J$  = 25°C.

500 mW

| Parameter                                                            | Conditions                                                                                                                       | Notes    | Typ<br>(Note 10) | Tested<br>Limit<br>(Note 5) | Design<br>Limit<br>(Note 6) | Units                                |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-----------------------------|-----------------------------|--------------------------------------|

| Resolution                                                           |                                                                                                                                  |          | 12               | 12                          | 12                          | Bits                                 |

| Linearity Error<br>(End Point Linearity)                             | Zero and Full-Scale<br>Adjusted<br>DAC1208, DAC1230<br>DAC1209, DAC1231<br>DAC1210, DAC1232                                      | 4, 7, 13 |                  | ±0.018<br>±0.024<br>±0.050  | ±0.018<br>±0.024<br>±0.05   | % of FSR<br>% of FSR<br>% of FSR     |

| Differential Non-Linearity                                           | Zero and Full-Scale<br>Adjusted<br>DAC1208, DAC1230<br>DAC1209, DAC1231<br>DAC1210, DAC1232                                      | 4, 7, 13 |                  | ±0.018<br>±0.024<br>±0.050  | ±0.018<br>±0.024<br>±0.05   | % of FSR<br>% of FSR<br>% of FSR     |

| Monotonicity                                                         |                                                                                                                                  | 4        | 12               | 12                          | 12                          | Bits                                 |

| Gain Error (Min)                                                     | Using Internal R <sub>Fb</sub>                                                                                                   | 7        | -0.1             | 0.0                         |                             | % of FSR                             |

| Gain Error (Max)                                                     | $V_{ref} = \pm 10V, \pm 1V$                                                                                                      | 7        | -0.1             | -0.2                        |                             | % of FSR                             |

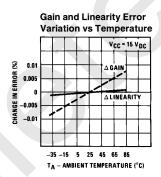

| Gain Error Tempco                                                    |                                                                                                                                  | 7        | ±1.3             |                             | ± 6.0                       | ppm of FS/°C                         |

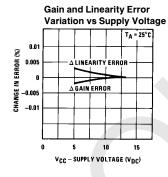

| Power Supply Rejection                                               | All Digital Inputs<br>Latched High                                                                                               | 7        | ±3.0             | ±30                         |                             | ppm of FSR/                          |

| Reference Input Resistance (Min)<br>Reference Input Resistance (Max) |                                                                                                                                  | 13       | 15<br>15         | 10<br>20                    | 10<br>20                    | kΩ                                   |

| Output Feedthrough Error                                             | V <sub>REF</sub> = 20 Vp-p, f = 100 kHz<br>All Data Inputs Latched<br>Low                                                        | 9        | 3.0              |                             |                             | mVp-p                                |

| Output Capacitance                                                   | All Data Inputs I <sub>OUT1</sub> Latched High I <sub>OUT2</sub> All Data Inputs I <sub>OUT1</sub> Latched Low I <sub>OUT2</sub> |          |                  |                             | 200<br>70<br>70<br>200      | pF<br>pF<br>pF<br>pF                 |

| Supply Current Drain                                                 |                                                                                                                                  | 13       |                  | 2.0                         | 2.5                         | mA                                   |

| Output Leakage Current IOUT1                                         | All Data Inputs Latched<br>Low                                                                                                   | 11, 13   | 0.1              | 15                          | 15                          | nA                                   |

| lout2                                                                | All Data Inputs Latched<br>High                                                                                                  | 11, 13   | 0.1              | 15                          | 15                          | nA                                   |

| Digital Input Threshold                                              | Low Threshold<br>High Threshold                                                                                                  | 13<br>13 |                  | 0.8<br>2.2                  | 0.8<br>2.2                  | V <sub>DC</sub><br>V <sub>DC</sub>   |

| Digital Input Currents                                               | Digital Inputs < 0.8V<br>Digital Inputs > 2.2V                                                                                   | 13<br>13 |                  | -200<br>10                  | -200<br>10                  | μΑ <sub>DC</sub><br>μΑ <sub>DC</sub> |

## **Electrical Characteristics** (Continued)

$V_{REF}=10.000~V_{DC},~V_{CC}=11.4~V_{DC}$  to 15.75  $V_{DC}$  unless otherwise noted. Boldface limits apply from  $T_{MIN}$  to  $T_{MAX}$  (see Note 13); all other limits  $T_A=T_J=25^{\circ}C$ .

| Symbol          | Parameter                       | Conditions                 | See<br>Note | Typ<br>(Note 10) | Tested<br>Limit<br>(Note 5) | Design<br>Limit<br>(Note 6) | Units |

|-----------------|---------------------------------|----------------------------|-------------|------------------|-----------------------------|-----------------------------|-------|

| AC CHARAC       | TERISTICS                       |                            |             |                  |                             |                             |       |

| t <sub>s</sub>  | Current Setting Time            | $V_{IL} = 0V, V_{IH} = 5V$ |             | 1.0              |                             |                             | μs    |

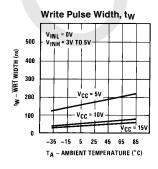

| t <sub>W</sub>  | Write and XFER Pulse Width Min. | $V_{IL} = 0V, V_{IH} = 5V$ | 8           | 50               |                             | 320<br><b>320</b>           |       |

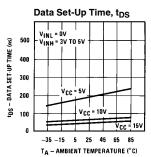

| t <sub>DS</sub> | Data Setup Time Min.            | $V_{IL} = 0V, V_{IH} = 5V$ |             | 70               |                             | 320<br><b>320</b>           |       |

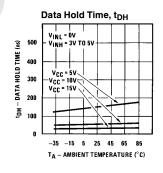

| t <sub>DH</sub> | Data Hold Time Min.             | $V_{IL} = 0V, V_{IH} = 5V$ |             | 30               |                             | 90<br><b>90</b>             | ns    |

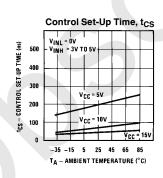

| t <sub>CS</sub> | Control Setup Time Min.         | $V_{IL} = 0V, V_{IH} = 5V$ |             | 60               |                             | 320<br><b>320</b>           |       |

| t <sub>CH</sub> | Control Hold Time Min.          | $V_{IL} = 0V, V_{IH} = 5V$ |             | 0                |                             | 10                          |       |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: This 500 mW specification applies for all packages. The low intrinsic power dissipation of this part (and the fact that there is no way to significantly modify the power dissipation) removes concern for heat sinking.

Note 4: Both  $I_{OUT1}$  and  $I_{OUT2}$  must go to ground or the virtual ground of an operational amplifier. The linearity error is degraded by approximately  $V_{OS} \div V_{REF}$ . For example, if  $V_{REF} = 10V$  then a 1 mV offset,  $V_{OS}$ , on  $I_{OUT1}$  or  $I_{OUT2}$  will introduce an additional 0.01% linearity error.

Note 5: Tested and guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 6: Design limits are guaranteed but not 100% tested. These limits are not used to calculate outgoing quality levels. Guaranteed for  $V_{CC} = 11.4V$  to 15.75V and  $V_{REF} = -10V$  to +10V.

Note 7: The unit FSR stands for full-scale range. Linearity Error and Power Supply Rejection specs are based on this unit to eliminate dependence on a particular  $V_{REF}$  value to indicate the true performance of the part. The Linearity Error specification of the DAC1208 is 0.012% of FSR(max). This guarantees that after performing a zero and full-scale adjustment, the plot of the 4096 analog voltage outputs will each be within 0.012%  $\times V_{REF}$  of a straight line which passes through zero and full-scale. The unit ppm of FSR(parts per million of full-scale) are used for convenience to define specs of very small percentage values, typical of higher accuracy converters. In this instance, 1 ppm of FSR =  $V_{REF}/10^6$  is the conversion factor to provide an actual output voltage quantity. For example, the gain error tempco spec of  $\pm 6$  ppm of FS/°C represents a worst-case full-scale gain error change with temperature from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  of  $\pm (6)(V_{REF}/10^6)(125^{\circ}\text{C})$  or  $\pm 0.75$  (10 $^{-3}$ )  $V_{REF}$  which is  $\pm 0.075\%$  of  $V_{REF}$ .

Note 8: This spec implies that all parts are guaranteed to operate with a write pulse or transfer pulse width (t<sub>W</sub>) of 320 ns. A typical part will operate with t<sub>W</sub> of only 100 ns. The entire write pulse must occur within the valid data interval for the specified t<sub>W</sub>, t<sub>DS</sub>, t<sub>DH</sub> and t<sub>S</sub> to apply.

Note 9: To achieve this low feedthrough in the D package, the user must ground the metal lid. If the lid is left floating the feedthrough is typically 6 mV.

Note 10: Typicals are at 25°C and represent the most likely parametric norm.

Note 11: A 10 nA leakage current with  $R_{Fb}$ = 20k and  $V_{REF}$ = 10V corresponds to a zero error of  $(10\times10^{-9}\times20\times10^{3})\times100\%$  10V or 0.002% of FS.

Note 12: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 13: Tested limit for −1 suffix parts applies only at 25°C.

#### **Connection Diagrams**

TL/H/5690-2

See Ordering Information

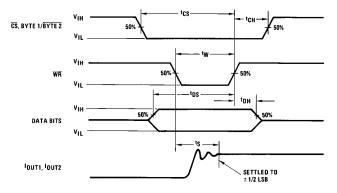

# **Switching Waveforms**

TL/H/5690-3

# **Typical Performance Characteristics**

# **Definition of Package Pinouts**

CONTROL SIGNALS (all control signals are level actuated)

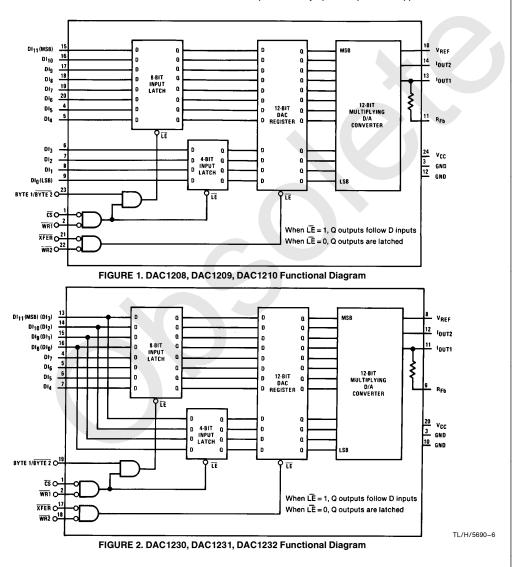

$\overline{\text{\textbf{CS}}}\text{:}$  Chip Select (active low). The  $\overline{\text{\textbf{CS}}}$  will enable  $\overline{\text{\textbf{WR1}}}.$

$\overline{\textbf{WR1}}$ : Write 1. The active low  $\overline{\textbf{WR1}}$  is used to load the digital data bits (DI) into the input latch. The data in the input latch is latched when  $\overline{\textbf{WR1}}$  is high. The 12-bit input latch is split into two latches. One holds the first 8 bits, while the other holds 4 bits. The Byte  $1/\overline{B}$  yte  $\overline{2}$  control pin is used to select both latches when Byte  $1/\overline{B}$  yte  $\overline{2}$  is high or to overwrite the 4-bit input latch when in the low state.

Byte 1/Byte 2: Byte Sequence Control. When this control is high, all 12 locations of the input latch are enabled. When low, only the four least significant locations of the input latch are enabled.

$\overline{\text{WR2}}$ : Write 2 (active low). The  $\overline{\text{WR2}}$  will enable  $\overline{\text{XFER}}$ .

**XFER:** Transfer Control Signal (active low). This signal, in combination with WR2, causes the 12-bit data which is available in the input latches to transfer to the DAC register.

$\mathrm{DI}_0$  to  $\mathrm{DI}_{11}$ : Digital Inputs.  $\mathrm{DI}_0$  is the least significant digital input (LSB) and  $\mathrm{DI}_{11}$  is the most significant digital input (MSB).

$I_{OUT1}$ : DAC Current Output 1.  $I_{OUT1}$  is a maximum for a digital code of all 1s in the DAC register, and is zero for all 0s in the DAC register.

$I_{OUT2}\!\!:$  DAC Current Output 2.  $I_{OUT2}$  is a constant minus  $I_{OUT1}\!\!:$  or  $I_{OUT1}\!\!+\!I_{OUT2}\!\!=\!\!$  constant (for a fixed reference voltage). This constant current is

$$V_{\mathsf{REF}} imes \left(1 - \frac{1}{4096}\right)$$

divided by the reference input resistance.

**R<sub>Fb</sub>:** Feedback Resistor. The feedback resistor is provided on the IC chip for use as the shunt feedback resistor for the external op amp which is used to provide an output voltage for the DAC. This on-chip resistor should always be used (not an external resistor) since it matches the resistors in the on-chip R-2R ladder and tracks these resistors over temperature.

$V_{REF}\colon$  Reference Voltage Input. This input connects an external precision voltage source to the internal R-2R ladder.  $V_{REF}$  can be selected over the range of 10V to -10V. This is also the analog voltage input for a 4-quadrant multiplying DAC application.

$V_{CC}\!:$  Digital Supply Voltage. This is the power supply pin for the part.  $V_{CC}$  can be from 5  $V_{DC}$  to 15  $V_{DC}\!.$  Operation is optimum for 15  $V_{DC}\!.$

**GND:** Pins 3 and 12 of the DAC1208, DAC1209, and DAC1210 must be connected to ground. Pins 3 and 10 of

a) End Point Test After Zero and FS Adjust

the DAC1230, DAC1231, and DAC1232 must be connected to ground. It is important that  $I_{OUT_1}$  and  $I_{OUT_2}$  are at ground potential for current switching applications. Any difference of potential ( $V_{OS}$  on these pins) will result in a linearity change of

$$\frac{V_{OS}}{3\,V_{REF}}$$

For example, if  $V_{REF}=10V$  and these ground pins are 9 mV offset from  $I_{OUT_1}$  and  $I_{OUT_2}$ , the linearity change will be 0.03%.

#### **Definition of Terms**

**Resolution:** Resolution is defined as the reciprocal of the number of discrete steps in the DAC output. It is directly related to the number of switches or bits within the DAC. For example, the DAC1208 has 2<sup>12</sup> or 4096 steps and therefore has 12-bit resolution.

**Linearity Error:** Linearity error is the maximum deviation from a *straight line passing through the endpoints of the DAC transfer characteristic.* It is measured after adjusting for zero and full-scale. Linearity error is a parameter intrinsic to the device and cannot be externally adjusted.

National's linearity test (a) and the best straight line test (b) used by other suppliers are illustrated below. The best straight line (b) requires a special zero and FS adjustment for each part, which is almost impossible for the user to determine. The end point test uses a standard zero FS adjustment procedure and is a much more stringent test for DAC linearity.

**Power Supply Sensitivity:** Power supply sensitivity is a measure of the effect of power supply changes on the DAC full-scale output.

Settling Time: Full-scale current settling time requires zero to full-scale or full-scale to zero output change. Settling time is the time required from a code transition until the DAC output reaches within  $\pm 1/\!\!/_2$  LSB of the final output value.

**Full-Scale Error:** Full-scale error is a measure of the output error between an ideal DAC and the actual device output. Ideally, for the DAC1208 or DAC1230 series, full-scale is  $V_{REF}=1$  LSB. For  $V_{REF}=10V$  and unipolar operation,  $V_{FULL-SCALE}=10.0000V-2.44$  mV=9.9976V. Full-scale error is adjustable to zero.

**Differential Non-Linearity:** The difference between any two consecutive codes in the transfer curve from the theoretical 1 LSB is differential non-linearity.

**Monotonic:** If the output of a DAC increases for increasing digital input code, then the DAC is monotonic. A 12-bit DAC which is monotonic to 12 bits simply means that input increasing digital input codes will produce an increasing analog output.

b) Shifting FS Adjust to Pass Best Straight Line Test

# **Application Hints**

#### 1.0 DIGITAL INTERFACE

These DACs are designed to provide all of the necessary digital input circuitry to permit a direct interface to a wide variety of microprocessor systems. The timing and logic level convention of the input control signals allow the DACs to be treated as a typical memory device or I/O peripheral with no external logic required in most systems. Essentially these DACs can be mapped as a two-byte stack in memory (or I/O space) to receive their 12 bits of input data in two successive 8-bit data writing sequences. The DAC1230 series is intended for use in systems with an 8-bit data bus. The DAC1208 series provides all 12 digital input lines which can be externally configured to be controlled from an 8-bit bus or can be driven directly from a 16-bit data bus.

All of the digital inputs to these DACs contain a unique threshold regulator circuit to maintain TTL voltage level compatibility independent of the applied  $V_{\rm CC}$  to the DAC. Any input can also be driven from higher voltage CMOS logic levels in non-microprocessor based systems. To prevent damage to the chip from static discharge, all unused digital inputs should be tied to  $V_{\rm CC}$  or ground. As a trouble-shooting aid, if any digital input is inadvertently left floating, the DAC will interpret the pin as a logic "1".

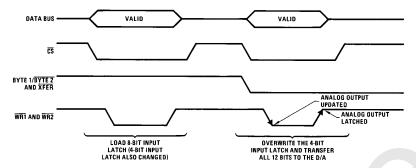

Double buffered digital inputs allow the DAC to internally format the 12-bit word used to set the current switching R-2R ladder network (see section 2.0) from two 8-bit data write cycles. *Figures 1* and *2* show the internal data registers and their controlling logic circuitry. The timing diagrams for updating the DAC output are shown in sections 1.1, 1.2 and 1.3 for three possible control modes. The method used depends strictly upon the particular application.

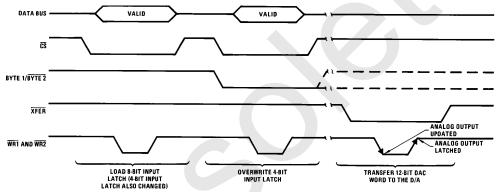

## 1.1 Automatic Transfer

The 12-bit DAC word is automatically transferred to the DAC register and the R-2R ladder when the second write (the 4 LSBs of the data) occurs.

TL/H/5690-7

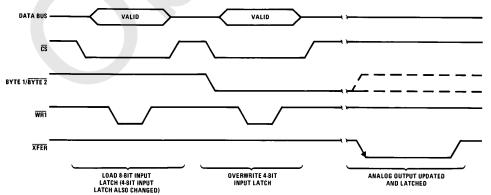

#### 1.2 Independent Processor Transfer Control

In this case a separate address is decoded to provide the  $\overline{\text{XFER}}$  signal. This allows the processor to load the next required DAC word but not change the analog output until some time later, most useful for the simultaneous updating of several DACs in a system where their  $\overline{\text{XFER}}$  lines would be tied together.

TL/H/5690-8

#### 1.3 Transfer via an External Strobe

This method is basically the same as the previous operation except the  $\overline{\text{XFER}}$  signal is provided by a device other than the processor. This allows the DAC to hold the code for a conditional analog output signal which will be required on demand from an external monitoring device (an analog voltage comparator for instance).

WR2 tied to a logic low (0V)

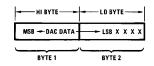

#### 1.4 Left-Justified Data Format

It is important to realize that the input registers of these DACs are arranged to accept a left-justified data word from the microprocessor with the most significant 8 bits coming first (Byte 1) and the lower 4 bits second. Left justification simply means that the binary point is assumed to be located to the left of the most significant bit. *Figure 3* shows how the 12 bits of DAC data should be arranged in 2 8-bit registers of an 8-bit processor before being written to the DAC.

X = don't care FIGURE 3. Left-Justified Data Format

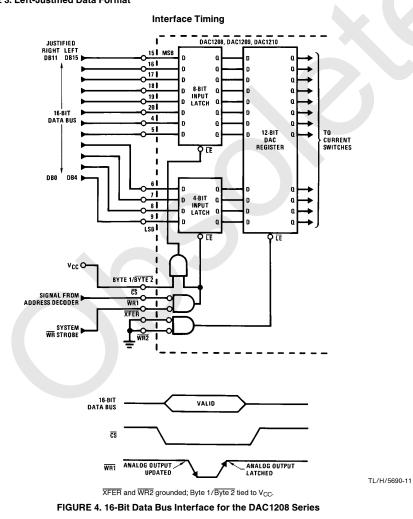

#### 1.5 16-Bit Data Bus Interface

The DAC1208 series provides all 12 digital input lines to permit a direct parallel interface to a 16-bit data bus. In this instance, double buffering is not always necessary (unless a simultaneous updating of several DACs or a data transfer via an external strobe is desired) so the 12-bit DAC register can be wired to flow-through whereby its Q outputs always reflect the state of its D inputs. The external connections required and the timing diagram for this single buffered application are shown in *Figure 4*. Note that either left or rightjustified data from the processor can be accommodated with a 16-bit data bus.

#### 1.6 Flow-Through Operation

Through primarily designed to provide microprocessor interface compatibility, the MICRO-DACs can easily be configured to allow the analog output to continuously reflect the state of an applied digital input. This is most useful in appli-

8

cations where the DAC is used in a continuous feedback control loop and is driven by a binary up/down counter, or in function generation circuits where a ROM is continuously providing DAC data.

Only the DAC1208, DAC1209, DAC1210 devices can have all 12 inputs flow-through. Simply grounding  $\overline{\text{CS}}$ ,  $\overline{\text{WR1}}$ ,  $\overline{\text{WR2}}$  and  $\overline{\text{XFER}}$  and tying Byte 1/Byte 2 high allows both internal registers to follow the applied digital inputs (flow-through) and directly affect the DAC analog output.

#### 1.7 Address Decoding Tips

It is possible to map the MICRO-DACs into system ROM space to allow more efficient use of existing address decoding hardware. The DAC in effect can share the same addresses of any number of ROM locations. The ROM outputs will only be enabled by a READ of its address (gated by the system READ strobe) and the DAC will only accept data that is written to the same address (gated by the system WRITE strobe).

The Byte  $1/\overline{Byte~2}$  control function can easily be generated by the processor's least significant address bit (A0) by placing the DAC at two consecutive address locations and utilizing double-byte WRITE instructions which automatically increment or decrement the address. The  $\overline{CS}$  and  $\overline{XFER}$  signals can then be decoded from the remaining address bits. Care must be taken in selecting the actual address used for Byte 1 of the DAC to prevent a carry (as a result of

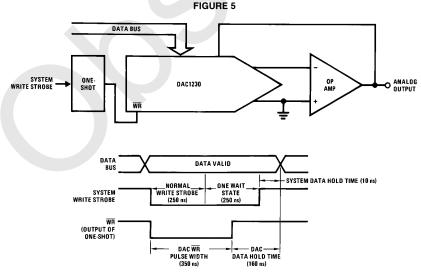

incrementing the address for Byte 2) from propagating through the address word and changing any of the bits decoded for  $\overline{\text{CS}}$  or  $\overline{\text{XFER}}$ . Figure 5 shows how to prevent this effect.

The same problem can occur from a borrow when an autodecremented address is used; but only if the processor's address outputs are inverted before being decoded.

#### 1.8 Control Signal Timing

When interfacing these MICRO-DACs to any microprocessor, there are two important time relationships that must be considered to insure proper operation. The first is the minimum  $\overline{WR}$  strobe pulse width which is specified as 320 ns for  $V_{CC}=11.4V$  to 15.75V and operation over temperature, but typically a pulse width of only 250 ns is adequate. A second consideration is that the guaranteed minimum data hold time of 90 ns should be met or erroneous data can be latched. This hold time is defined as the length of time data must be held valid on the digital inputs  $\it after$  a qualified (via  $\overline{\rm CS})$   $\overline{\rm WR}$  strobe makes a low to high transition to latch the applied data.

If the controlling device or system does not inherently meet these timing specs the DAC can be treated as a slow memory or peripheral and utilize a technique to extend the write strobe. A simple extension of the write time, by adding a wait state, can simultaneously hold the write strobe active and data valid on the bus to satisfy the minimum  $\overline{\rm WR}$  pulse

| Write              | Address Bits |        |    |     |  |  |

|--------------------|--------------|--------|----|-----|--|--|

| Cycle              | 15           | 2      | 1* | 0** |  |  |

| First<br>(Byte 1)  | Deco         | ded to | 0  | 1   |  |  |

| Second<br>(Byte 2) | Addre        | ss DAC | 1  | 0   |  |  |

\*Starting with a 0 prevents a carry on address incrementing.

<sup>\*\*</sup>Used as Byte 1/Byte2 Control

FIGURE 6. Accommodating a High Speed System

width. If this does not provide a sufficient data hold time at the end of the write cycle, a negative edge triggered one-shot can be included between the system write strobe and the  $\overline{\rm WR}$  pin of the DAC. This is illustrated in Figure 6 for an exemplary system which provides a 250 ns  $\overline{\rm WR}$  strobe time with a data hold time of only 10 ns.

The proper data set-up time prior to the latching edge (low to high transition) of the  $\overline{\text{WR}}$  strobe, is insured if the  $\overline{\text{WR}}$  pulse width is within spec and the data is valid on the bus for the duration of the DAC  $\overline{\text{WR}}$  strobe.

#### 1.9 Digital Signal Feedthrough

A typical microprocessor is a tremendous potential source of high frequency noise which can be coupled to sensitive analog circuitry. The fast edges of the data and address bus signals generate frequency components of 10's of meganertz and may cause fast transients to appear at the DAC output, even when data is latched internally.

In low frequency or DC applications, low pass filtering can reduce the magnitude of any fast transients. This is most

easily accomplished by over-compensating the DAC output amplifier by increasing the value of its feedback capacitor.

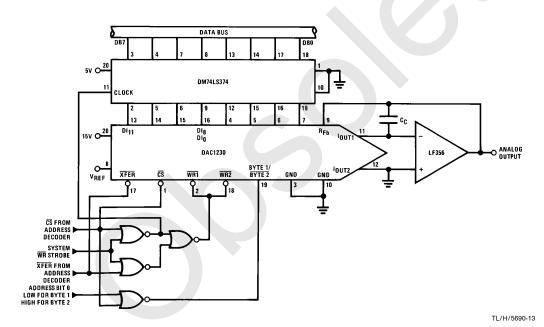

In applications requiring a fast output response from the DAC and op amp, filtering may not be feasible. In this event, digital signals can be completely isolated from the DAC circuitry, by the use of a DM74LS374 latch, until a valid  $\overline{\text{CS}}$  signal is applied to update the DAC. This is shown in Figure 7.

A single TRI-STATE® data buffer such as the DM81LS95 can be used to isolate any number of DACs in a system. Figure 8 shows this isolating circuitry and decoding hardware for a multiple DAC analog output card. Pull-up resistors are used on the buffer outputs to limit the impedance at the DAC digital inputs when the card is not selected. A unique feature of this card is that the DAC XFER strobes are controlled by the data bus. This allows a very flexible update of any combination of analog outputs via a transfer word which would contain a zero in the bit position assigned to any of the DACs required to change to a new output value.

FIGURE 7. Isolating Data Bus from DAC Circuitry to Eliminate Digital Noise Coupling

# **Application Hints** (Continued) 8080 BUS DM8131 BUS COMP A14 CS0 A12 XFR0 A11 DAC1230 WR2 WR1 B1/B2 DM81LS95 Buffer Y8 Y7 CS1 Y6 Y5 XFR1 WR2 DAC1230 102 D3 Y4 Y3 Y2 Y1 WR1 DO 0.1 μF 1/3 DM70L97 BUFFER G2 Y6 Y5 A6 A5 B1/B2 DM74LS42 DECODER CSO CS1 CS2 CS3 A2 A1 TRANSFER SELECT CS3 2/3 DM7097 BUFFER XFR3 WR2 DAC1230 WR1 D2 D1 Y4 O XFR2 Y3 O XFR1 Y2 O XFR0 **A3** TL/H/5690-14

FIGURE 8. TRI-STATE® Buffers Isolate the Data and Control Lines from the DACs.

A Transfer Word Provides a Flexible Update.

#### 2.0 ANALOG APPLICATIONS

The analog output signal for these DACs is derived from a conventional R-2R current switching ladder network. A detailed description of this network can be found on the DAC1000 series data sheet. Basically, output I<sub>OUT1</sub> provides a current directly proportional to the product of the applied reference voltage and the digital input word. A second output, I<sub>OUT2</sub> will be a current proportional to the complement of the digital input. Specifically:

$$I_{OUT1} = \frac{V_{REF}}{R} \times \frac{D}{4096};$$

$$I_{OUT2} = \frac{V_{REF}}{R} \times \frac{4095 - D}{4096}$$

where D is the decimal equivalent of the applied 12-bit binary word (ranging from 0 to 4095),  $V_{REF}$  is the voltage applied to the  $V_{REF}$  terminal and R is the internal resistance of the R-2R ladder. R is nominally 15 k $\Omega$ .

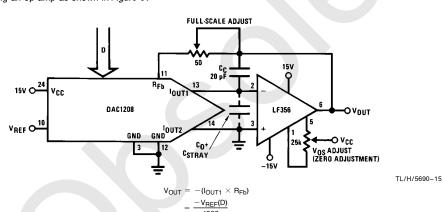

#### 2.1 Obtaining a Unipolar Output Voltage

To maintain linearity of output current with changes in the applied digital code, it is important that the voltages at both of the current output pins be as near ground potential (0  $V_{DC}$ ) as possible. With  $V_{REF} = +\,10V$  every millivolt appearing at either  $I_{OUT1}$  or  $I_{OUT2}$  will cause a 0.01% linearity error. In most applications this output current is converted to a voltage by using an op amp as shown in Figure 9.

The inverting input of the op amp is a virtual ground created by the feedback from its output through the internal  $15~\mathrm{k}\Omega$  resistor,  $R_{Fb}$ . All of the output current (determined by the digital input and the reference voltage) will flow through  $R_{Fb}$  to the output of the amplifier. Two-quadrant operation can be obtained by reversing the polarity of  $V_{REF}$  thus causing  $I_{OUT1}$  to flow into the DAC and be sourced from the output of the amplifier. The output voltage, in either case, is always equal to  $I_{OUT1} \times R_{Fb}$  and is the opposite polarity of the reference voltage.

The reference can be either a stable DC voltage source or an AC signal anywhere in the range from -10V to +10V. The DAC can be thought of as a digitally controlled attenuator: the output voltage is always less than the applied reference voltage. The V $_{\text{REF}}$  terminal of the device presents a nominal impedance of 15 k $\Omega$  to ground to external circuitry. Always use the internal  $R_{\text{Fb}}$  resistor to create an output voltage since this resistor matches (and tracks with temper-

voltage since this resistor matches (and tracks with temperature) the value of the resistors used to generate the output current (I<sub>OUT1</sub>).

The selected op amp should have as low a value of input

The selected op amp should have as low a value of input bias current as possible. The product of the bias current times the feedback resistance creates an output voltage error which can be significant in low reference voltage applications. BI-FETTM op amps are highly recommended for use with these DACs because of their very low input current.

FIGURE 9. Unipolar Output Configuration

for  $0 \le D \le 4095$

Transient response and settling time of the op amp are important in fast data throughput applications. The largest stability problem is the feedback pole created by the feedback resistance,  $\mathsf{R}_\mathsf{Fb}$ , and the output capacitance of the DAC. This appears from the op amp output to the (—) input and includes the stray capacitance at this node. Addition of a lead capacitance,  $\mathsf{C}_\mathsf{C}$  in Figure 9, greatly reduces overshoot and ringing at the output for a step change in DAC output current.

#### 2.1.1 Zero and Full-Scale Adjustments

For accurate conversions, the input offset voltage of the output amplifier must always be nulled. Amplifier offset errors create an overall degradation of DAC linearity.

The fundamental purpose of zeroing is to make the voltage appearing at the DAC outputs as near 0  $V_{DC}$  as possible. This is accomplished by shorting out  $R_{Fb}$ , the amplifier feedback resistor, and adjusting the  $v_{OS}$  nulling potentiometer of the op amp until the output reads zero volts. This is done, of course, with an applied digital code of all zeros if  $l_{OUT1}$  is driving the op amp (all ones for  $l_{OUT2}$ ). The short around  $R_{Fb}$  is then removed and the converter is zero adjusted.

A unique feature of this series of DACs is that the full-scale or gain error is guaranteed to be negative. The gain error specification is a measure of how close the value of the

internal feedback resistor,  $R_{Fb}$ , matches the R-2R ladder resistors. A negative gain error indicates that  $R_{Fb}$  is a smaller resistance value than it should be. To adjust this gain error, some resistance must always be added in series with  $R_{Fb}$ . The  $50\Omega$  potentiometer shown is sufficient to adjust the worst-case gain error for these devices.

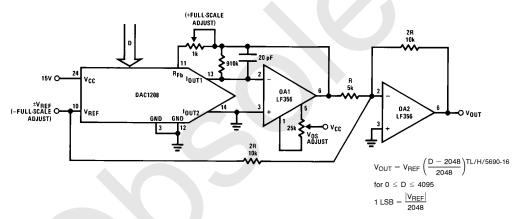

#### 2.2 Bipolar Output Voltage from a Fixed Reference

The addition of a second op amp to the unipolar circuit can generate a bipolar output voltage from a fixed reference voltage. This, in effect, gives sign significance to the MSB of the digital input word to allow two quadrant multiplication of the reference voltage. The polarity of the reference can also be reversed to realize full 4-quadrant multiplication. This circuit is shown in *Figure 10*.

This configuration features several improvements over existing circuits for a bipolar output shown with other multiplying DACs. Only the offset voltage of amplifier 1 affects the linearity of the DAC. The offset voltage error of the second op amp (although a constant output error) has no effect on linearity. In addition, this configuration offers a non-interactive positive and negative full-scale calibration procedure.

| Input Code    | Ideal                      | V <sub>OUT</sub>              |

|---------------|----------------------------|-------------------------------|

| MSBLSB        | + V <sub>REF</sub>         | $-V_{REF}$                    |

| 111111111111  | V <sub>REF</sub> -1 LSB    | - V <sub>REF</sub>   +1 LSB   |

| 1100000000000 | V <sub>REF</sub> /2        | - V <sub>REF</sub>  /2        |

| 1000000000000 | 0                          | 0                             |

| 011111111111  | _1 LSB                     | +1 LSB                        |

| 001111111111  | - V <sub>REF</sub> - 1 LSB | $\frac{ V_{REF} }{2}$ + 1 LSB |

| 000000000000  | -V <sub>REF</sub>          | +  V <sub>REF</sub>           |

FIGURE 10. Bipolar Output Voltage Configuration

# 2.2.1 Zero and Full-Scale Adjustments

To calibrate the bipolar output circuit, three adjustments are required. The first step is to set all of the digital inputs LOW (to force  $I_{OUT1}$  to 0) then null the  $V_{OS}$  of amplifier 1 by setting the voltage at its inverting input (pin 2) to zero volts. Next, with a code of all zeros still applied, adjust "-full-scale adjust", the reference voltage, for  $V_{OUT}=\pm |V_{REF}$  ideal|. The polarity of the output voltage at this time will be opposite that of the applied reference. Finally, set all of the digital inputs HIGH and adjust "+full-scale adjust" for

$$V_{OUT} = V_{REF} \frac{2047}{2048}$$

The polarity of the output will be the same as that of the reference voltage.

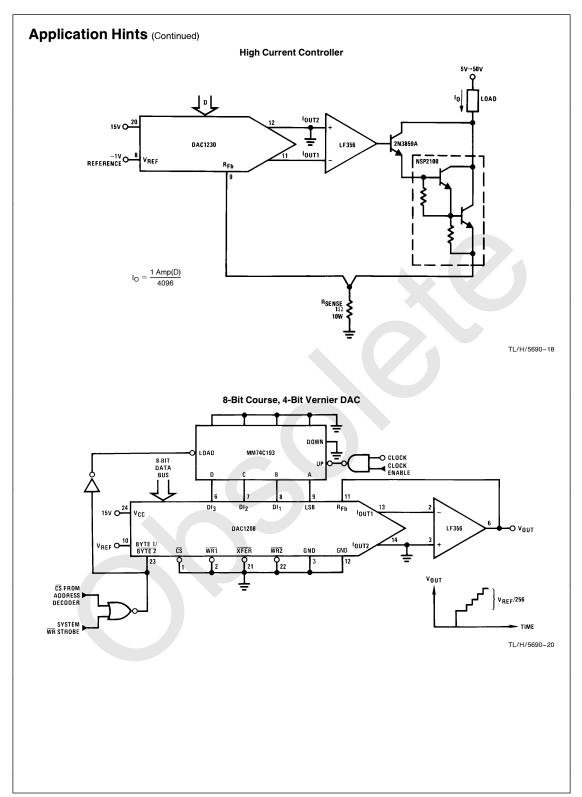

#### 3.0 APPLICATION IDEAS

In this section the digital input word is represented by the letter D and is equal to the decimal equivalent of the 12-bit binary input. Hence D can be any integer value between 0 and 4095.

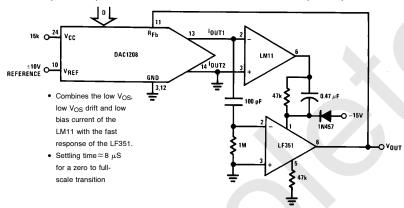

#### Composite Amplifier for Good DC Characteristics and Fast Output Response

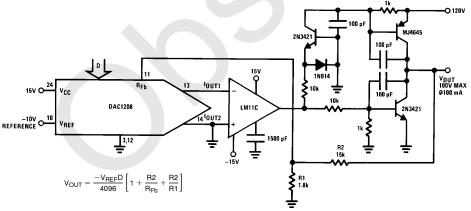

### High Voltage, Power DAC

| Part Number  | Non-Linearity | Package      | Temperature<br>Range |  |

|--------------|---------------|--------------|----------------------|--|

| DAC1208LCJ   | 0.018%        | J24A Cerdip  | -40°C to +85°C       |  |

| DAC1208LCJ-1 | 0.018%        | J24A Cerdip  | 0°C to +70°C         |  |

| DAC1209LCJ   | 0.024%        | J24A Cerdip  | -40°C to +85°C       |  |

| DAC1210LCJ   | 0.050%        | J24A Cerdip  | -40°C to +85°C       |  |

| DAC1210LCJ-1 | 0.050%        | J24A Cerdip  | 0°C to +70°C         |  |

| DAC1230LCJ   | 0.018%        | J20A Cerdip  | -40°C to +85°C       |  |

| DAC1230LCJ-1 | 0.018%        | J20A Cerdip  | 0°C to +70°C         |  |

| DAC1231LCJ   | 0.024%        | J20A Cerdip  | -40°C to +85°C       |  |

| DAC1231LCJ-1 | 0.024%        | J20A Cerdip  | 0°C to +70°C         |  |

| DAC1231LCN   | 0.024%        | N20A Plastic | 0°C to +70°C         |  |

| DAC1231LCWM  | 0.024%        | M20B SO      | 0°C to +70°C         |  |

| DAC1231LIN   | 0.024%        | N20A Plastic | -40°C to +85°C       |  |

| DAC1232LCJ   | 0.050%        | J20A Cerdip  | -40°C to +85°C       |  |

| DAC1232LCJ-1 | 0.050%        | J20A Cerdip  | 0°C to +70°C         |  |

| DAC1232LCN   | 0.050%        | N20A Plastic | 0°C to +70°C         |  |

| DAC1232LCWM  | 0.050%        | M20B SO      | 0°C to +70°C         |  |

| DAC1232LIN   | 0.050%        | N20A Plastic | -40°C to +85°C       |  |

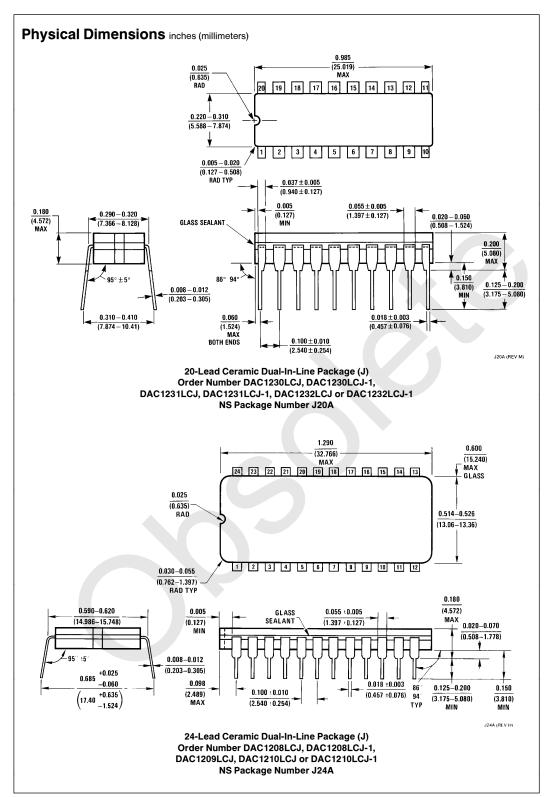

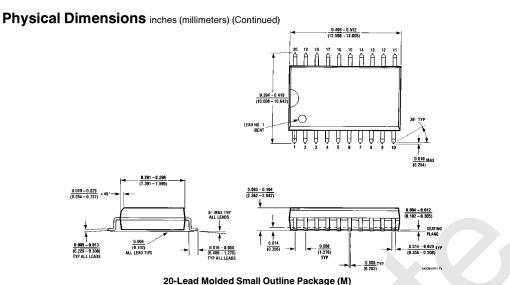

# Order Number DAC1231LCWM or DAC1232LCWM NS Package Number M20B

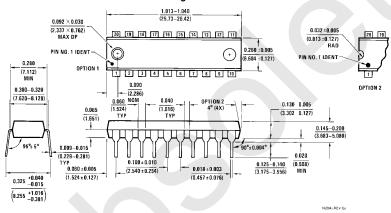

20-Lead Molded Dual-In-Line Package (N) Order Number DAC1231LCN, DAC1231LIN, DAC1232LCN or DAC1232LIN NS Package Number N20A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

#### **National Semiconductor**

Europe Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-30U os os os email: onjwage etwom2.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85

English Tel: (+49) 0-180-532 78 32

Français Tel: (+49) 0-180-534 16 80

Tel: (+49) 0-180-534 16 80 Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

# Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

TI E2E Community Home Page <u>e2e.ti.com</u>

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated