#### **DESIGN FEATURES**

- Intelligent bidirectional bus repeater with self-generating or external control

- Eight independent channels

- Open-collector outputs (meets DEC UNIBUS\* specifications)

- TTL compatible

- High speed (30-nanoseconds max)

- · Expandable to any number of bits

- High input impedance for every operating value of V<sub>CC</sub>

- Low input current (less than 100-microamperes); high output current (up to 70-milliamperes)

- 0.6 in. 24 pin DIP

- + 5V supply

#### USE AND APPLICATION

- Minicomputers

- Microcomputers MOS/Bipolar

- Communications

- Signal buffer

- · Bus fan-out extensions

- Distributed processing

- Bidirectional bus connector/isolator

### **PRODUCT DESCRIPTION**

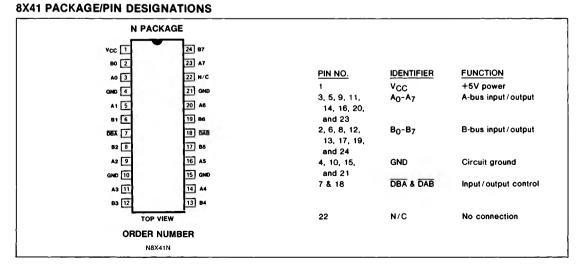

The Signetics 8X41 Autodirectional Bus Transceiver is a general purpose asynchronous device ideal for system bus expansion applications. The 8X41 consists of eight data channels, each with one pair of terminals (A<sub>1</sub> and B<sub>2</sub>); each data channel can be operated independently.

The device requires no external controls since all intelligence is internally generated; thus, operation of the device is completely autonomous. The first logic low signal that occurs on one channel terminal  $(A_i \text{ or } B_i)$  will be repeated on the corresponding terminal  $(B_i \text{ or } A_i)$  of the same channel.

The 8X41 is designed for use in open-collector bus systems where high speed and low-current inputs/high-current outputs are required. In system configurations, the discrete capabilities of the bus transceiver can be expanded by parallel connection to service any number of bits. To provide reliable operation and integrity of data transfers, all channels are disabled by an on-chip power monitor whenever  $V_{CC}$  falls below approximately 4V.

#### **FUNCTIONAL OPERATION**

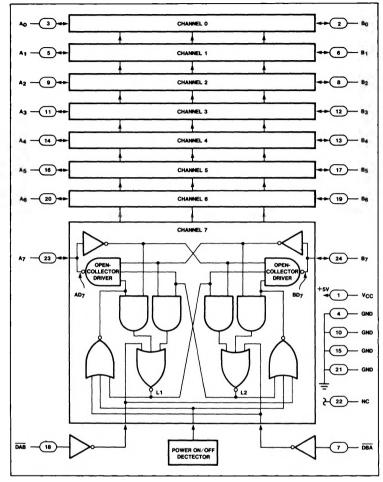

The 8X41 (Figure 1) consists of eight functionally independent yet logically identical channels. Each channel consists of two bus terminals (A, and B); each terminal is internally connected to an open-collector driver and a high-impedance receiver. The monitoring state of each channel is defined when both terminals (A, and B) are "high"; in this state, the internal logic of the 8X41 continually examines the A and B bus signals to determine signal direction—A, to B, or B, to A,. A low signal occurring at either of the two terminals causes the open-collector driver on the opposite terminal to follow suit; hence, the signal is repeated by the 8X41. For each channel, latches L1 and L2 determine signal direction. As shown in the truth table for these latches, there is no transmission of data when both signals are low, however, this condition should never occur during normal system operation.

The internal automatic direction control can be overridden by either or both of the common disable inputs— $\overline{DBA}$  and  $\overline{DAB}$ . When  $\overline{DBA}$  is driven low ( $\overline{DAB} = high$ ), the B<sub>1</sub> to A<sub>1</sub> path is interrupted and the device becomes a unidirectional repeater in the A<sub>1</sub> to B<sub>1</sub> direction only. With these conditions reversed ( $\overline{DAB} = low$  and  $\overline{DBA} = high$ ), the A<sub>1</sub> to B<sub>1</sub> path is interrupted and the chip functions as a unidirectional repeater in the B<sub>1</sub> to A<sub>1</sub> direction. When both control signals are low, data passage is inhibited in both directions. Refer to the I/O truth table for all possible input/output conditions.

\*Trademark of the Digital Equipment Corporation

**Signetics**

| DBA | DAB | FUNCTION                                              |

|-----|-----|-------------------------------------------------------|

| 0   | 0   | Data transmission<br>inhibited                        |

| 0   | 1   | A <sub>i</sub> → B <sub>i</sub>                       |

| 1   | 0   | A <sub>i</sub> ← B <sub>i</sub>                       |

| 1   | 1   | $\begin{array}{c} A_i - B_i \\ A_i - B_i \end{array}$ |

i = Channel 0, 1, 2, 3, 4, 5, 6, or 7  $A_i \rightarrow B_i$  = Data transmission from  $A_i$  to  $B_i$  $A_i \rightarrow B_i$  = Data transmission from  $B_i$  to  $A_i$

# TRUTH TABLE FOR INTERNAL LATCHES

| LATCHES |    | DIRECTION OF DATA                |  |  |  |

|---------|----|----------------------------------|--|--|--|

| L1      | L2 |                                  |  |  |  |

| 1       | 1  | Monitoring state                 |  |  |  |

| 1       | 0  | A <sub>i</sub> to B <sub>i</sub> |  |  |  |

| 0       | 1  | B <sub>i</sub> to A <sub>i</sub> |  |  |  |

| 0       | 0  | No transmission                  |  |  |  |

#### Figure 1. Logic Diagram of 8X41

#### **INPUT/OUTPUT TRUTH TABLE**

| EXTERNAL CONTROLS |        | INPUT SIGNALS |        | OUTPUT DRI |        |                                                                                        |

|-------------------|--------|---------------|--------|------------|--------|----------------------------------------------------------------------------------------|

| DAB               | DBA    | Aj            | Bj     | ADi        | BDi    |                                                                                        |

| н                 | н      | L             | L      | н          | н      |                                                                                        |

| н<br>Н            | Н      | н<br>Н        | L      | L          | L<br>H |                                                                                        |

| н                 | Н      | н             | н      | н          | н      |                                                                                        |

| н                 | L      | Ĺ             | Ĥ      | н          | Ĺ      |                                                                                        |

| н<br>Н            |        | н             | L<br>H | н          | н<br>Н |                                                                                        |

| L                 | н      | L             |        | L          | н      | Notes                                                                                  |

| L                 | н      | н<br>Н        | Ľ      |            | ) H    | A <sub>I</sub> = External signal<br>AD <sub>I</sub> = Output A drive                   |

| L                 | H<br>L | H<br>X        | H<br>X | H<br>H     | H<br>H | B <sub>1</sub> = External signal<br>BD <sub>1</sub> = Output B drive<br>X = Don't care |

8X41

Signetics

| PARAMETER              | DESCRIPTION                                   | TEST CONDITIONS                                                                                                          | LIMITS |     |      | UNITS      |                                            |

|------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------|-----|------|------------|--------------------------------------------|

|                        |                                               |                                                                                                                          | Min    | Тур | Max  |            |                                            |

| VOL                    | Bus output low<br>voltage (driver ON)         | I <sub>OL</sub> = 70 mA;<br>V <sub>CC</sub> = Min                                                                        |        |     | 0.5  | v          |                                            |

| *۷ <sub>B</sub>        | Bus input threshold<br>voltage (driver OFF)   |                                                                                                                          | 1.3    |     | 1.7  | v          | FROM OU<br>UNDER T                         |

| VIH (DBA,<br>DAB only) | High level input<br>voltage                   |                                                                                                                          | 2.0    |     |      | v          |                                            |

| VIL (DBA,<br>DAB only) | Low level input<br>voltage                    |                                                                                                                          |        |     | 0.8  | v          |                                            |

| VIC                    | Input clamp voltage                           | $V_{CC} = Min;$<br>$I_{IL} = -18mA$                                                                                      |        |     | -1.5 | v          | Note <sup>.</sup><br>C <sub>L</sub> includ |

| VPD                    | Power ON/OFF<br>detector threshold<br>voltage |                                                                                                                          | 3.7    |     | 4.35 | v          |                                            |

| IIH (DBA,<br>DAB only) | High level input<br>current                   | $V_{CC} = Max;$<br>$V_{IN} = 2.7V$                                                                                       |        |     | 20   | μA         |                                            |

| IIL (DBA,<br>DAB only) | Low level input<br>current                    | $V_{CC} = Max;$<br>$V_{IN} = 0.4V$                                                                                       |        |     | -0.4 | mA         |                                            |

| μ                      | Bus input current                             | V <sub>CC</sub> = Max;<br>V <sub>B</sub> = 2.5V*                                                                         |        |     | 100  |            |                                            |

|                        | (driver OFF)                                  | V <sub>CC</sub> = Max;<br>V <sub>B</sub> = 0V*                                                                           |        |     | -20  | <b>μ</b> Α |                                            |

| IOFF                   | Bus leakage current<br>(power OFF)            | V <sub>CC</sub> = 0V;<br>V <sub>B</sub> = 2.5V*                                                                          |        |     | 100  | μΑ         |                                            |

| lcc                    | Supply current                                | $V_{CC} = Max;$<br>$A_0-A_7 = Low \text{ or}$<br>$B_0-B_7 = Low \text{ and}$<br>$\overline{DBA} = \overline{DAB} = High$ |        | 145 | 180  | mA         | *V <sub>B</sub> = V <sub>BUS</sub>         |

### **DC CHARACTERISTICS** $V_{CC} = 5V (\pm 5\%); T_A = 0^{\circ}C \text{ to } 70^{\circ}C$

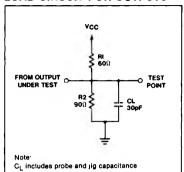

# LOAD CIRCUIT FOR OUTPUTS

### AC CHARACTERISTICS $V_{CC} = 5V (\pm 5\%); T_A = 0^{\circ}C \text{ to } 70^{\circ}C$

| PARAMETER        | DESCRIPTION                           | FROM                                       | то                                           | TEST CONDITIONS                   | LIMITS |     |     | UNITS |

|------------------|---------------------------------------|--------------------------------------------|----------------------------------------------|-----------------------------------|--------|-----|-----|-------|

|                  |                                       |                                            |                                              |                                   | Min    | Тур | Max | 1     |

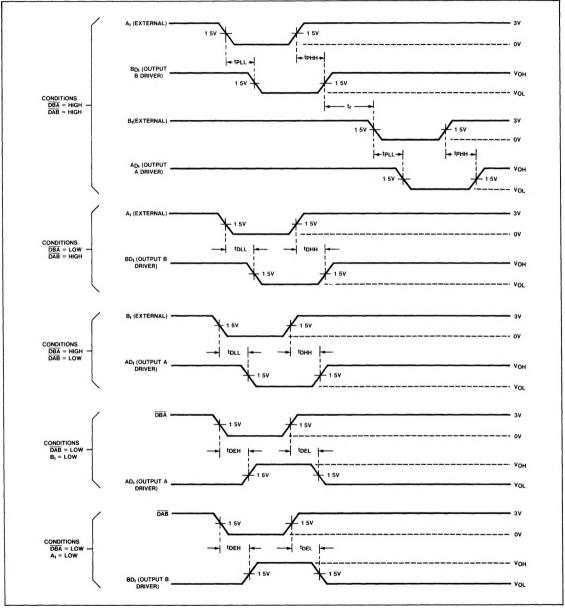

| <sup>t</sup> PLL | Propagation delay                     | Low A <sub>i</sub><br>Low B <sub>i</sub>   | Low BD <sub>i</sub><br>Low AD <sub>i</sub>   | DBA = DAB = High                  |        |     | 30  | ns    |

| <sup>†</sup> РНН | Propagation delay                     | High A <sub>i</sub><br>High B <sub>i</sub> | High BD <sub>i</sub><br>High AD <sub>i</sub> | DBA = DAB = High                  |        |     | 30  | ns    |

| Propagation data | Propagation delay                     | High A <sub>i</sub>                        | High BD <sub>i</sub>                         | DBA = Low; DAB = High             |        |     | 25  | ns    |

| Unn              | tDHH Propagation delay                | High B <sub>i</sub>                        | High AD <sub>i</sub>                         | DAB = Low; DBA = High             |        |     | 25  | ns    |

| tDLL             | Propagation delay                     | Low Ai                                     | Low BDi                                      | DBA = Low; DAB = High             |        |     | 25  | ns    |

|                  | Low Bi                                | Low ADi                                    | DAB = Low; DBA = High                        |                                   |        | 25  | ns  |       |

| †DEH             | Propagation delay                     | Low DBA                                    | High AD;                                     | DAB = Low; Bi = Low               |        |     | 30  | ns    |

| †DEL             | Propagation delay                     | High DBA                                   | Low ADi                                      | $\overline{DAB} = Low; B_1 = Low$ |        |     | 30  | ns    |

| <b>tDEH</b>      | Propagation delay                     | Low DAB                                    | High BD <sub>i</sub>                         | DBA = Low; A <sub>1</sub> = Low   |        |     | 30  | ns    |

| TDEL             | Propagation delay                     | High DAB                                   | Low BDi                                      | DBA = Low; A <sub>i</sub> = Low   |        |     | 30  | ns    |

| tr               | Recovery time (see<br>timing diagram) | -                                          | -                                            | DBA = DAB = High                  |        | 20  |     | ns    |

Notes A<sub>1</sub> = External signal AD<sub>1</sub> = Output A driver B<sub>1</sub> = External signal BD<sub>1</sub> = Output B driver

#### **8X41 TIMING DIAGRAM**

Signetics

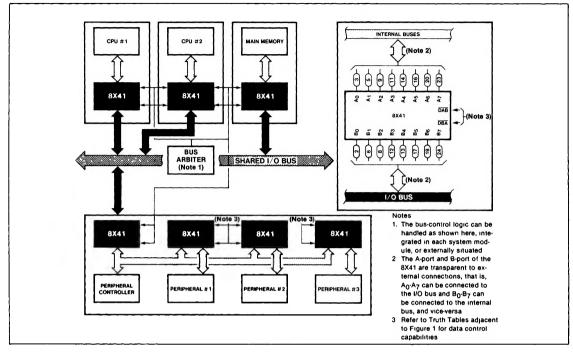

### **USING THE 8X41 IN A BUS-SHARED CONFIGURATION**

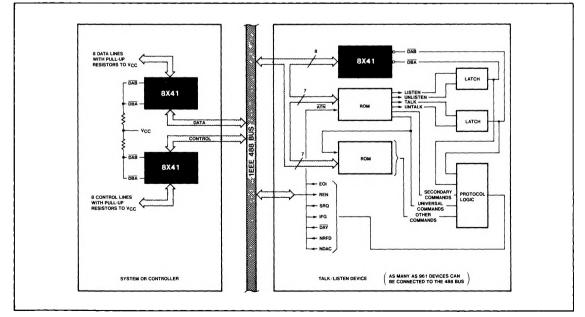

### INTERFACING 8X41 TO IEEE 488 BUS