#### **FEATURES**

- Two bidirectional 8-bit busses

- Independent bus operation (user-bus priority for data entry)

- User data input synchronous (8X372) or asynchronous (8X376) with respect to MCLK

- Programmed MicroController port address

- Three-state TTL outputs with high-drive capabilities

- Power-up to predetermined logic state

- Directly compatible with 8X305 or 8X300 MicroControllers

- Single +5V supply

- 0.4 inch 24-pin DIP

#### PRODUCT IDENTITY

8X372—Synchronous, three-state, bidirectional I/O port with programmed address.

8X376—Asynchronous, three-state, bidirectional I/O port with programmed address.

#### PRODUCT DESCRIPTION

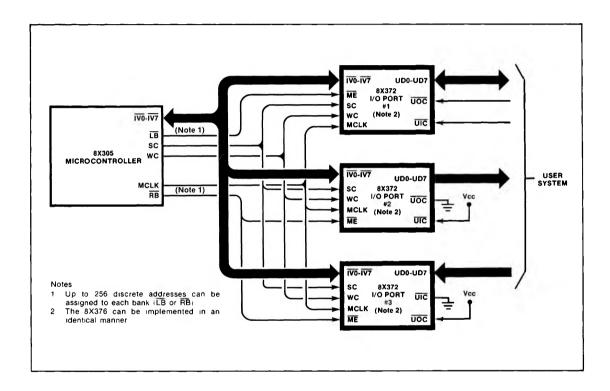

Each of these I/O ports is an addressable device designed for use as a bidirectional interface element in systems that use TTL-compatible busses. Typically, these I/O ports are used with the 8X305 MicroController and its associated Interface Vector ( $\overline{\text{IV}}$ ) bus; however, either port can also be used with the 8X300 MicroController or an equivalent

microprocessor. The 8X372 and 8X376 are funtionally the same and pin-for-pin compatible with their respective counterparts, the 8T32/8X32 and 8T36/8X36, however, the new parts feature better performance, increased drive current, and improved programming procedures.

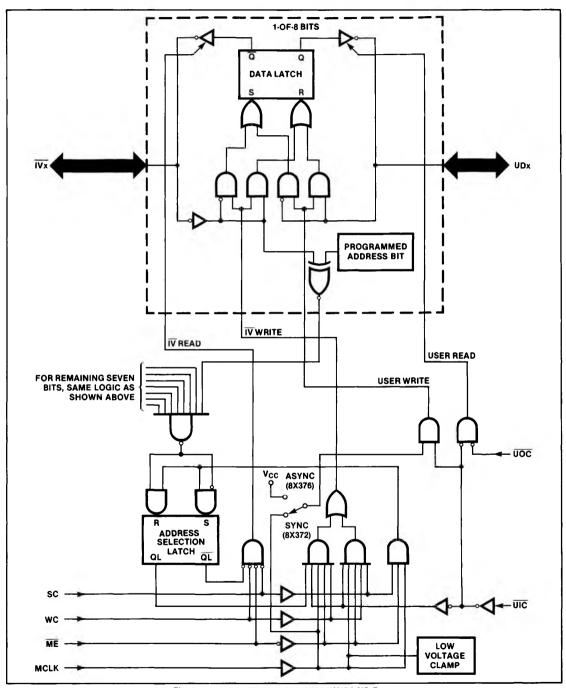

As shown in the logic diagram of Figure 1, each I/O port consists of eight identical data latches—bits 0 through 7. These latches are accessed through either of two 8-bit busses—one connecting to the MicroController (IV bus) and the other to the user system (UD bus). Separate controls are provided for each bus and both busses operate independently, except when both attempt to input data at the same time. In such situations, the user bus always has priority. The data latches are transparent, in that, while either bus is enabled for input, all transitions in input data are propagated to the other bus, if enabled for output.

Both the 8X372 and 8X376 are available with preprogrammed addresses ( $0_{10}$  through 255 $_{10}$ ), either device can be field-programmed over the same address range. Input/output operations can begin once the I/O port is selected and appropriate control signals are generated. Port selection is implemented by putting the I/O port address ( $0_{10}$ -255 $_{10}$ ) on the  $\overline{\text{IV}}$  bus; once selected, the I/O port remains selected until a different "port address" is put on the bus. Thus, software overhead is minimized. Data is accessible on the UD bus at all times. A Master Enable ( $\overline{\text{ME}}$ ) input, which is typically connected to the Left Bank ( $\overline{\text{LB}}$ ) or Right Bank ( $\overline{\text{RB}}$ ) output of the MicroController, provides the capability of organizing the  $\overline{\text{IV}}$  bus into two separate and independent banks of I/O devices.

|                    |                                                         | _                 | PIN. NO. | IDENTIFIER | FUNCTION                                                                                                                                              |                                                                                                                |

|--------------------|---------------------------------------------------------|-------------------|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| UD7 1              |                                                         | 24 Vcc            | 1-8      | UD7-UD0    | Three-state, bid <u>irectional</u> User Data (UD) bus, UD0 corresponds to V0                                                                          |                                                                                                                |

| UD6 2              | (372 OR 8X376<br>CHED, ADDRESSABLE<br>CTIONAL, I/O PORT | 23 IV7<br>22 IV6  | 9        | UOC        | User Output Control—active low input to enable data outp to UD0-UD7                                                                                   |                                                                                                                |

| UD4 4              |                                                         | POF               | 21 iV5   | 10         | UIC                                                                                                                                                   | User Input Control—active low input to enable data input from UD0-UD7                                          |

| UD3 5              | ADDRE<br>AL, 1/0                                        | 20) IV4<br>19 IV3 | 11       | ME         | Master Enable—active low input to enable the IV bus for data input, data output, or IV address selection/deselection UD-bus operations are unaffected |                                                                                                                |

|                    | 200                                                     | 18) iV2           | 12       | GND        | Ground                                                                                                                                                |                                                                                                                |

| UDO B              | BEST LATCHED, ADDRE                                     | ATCHE             | 17 IV1   | 13         | MCLK                                                                                                                                                  | Master Clock—active high input from MicroController used to strobe data into data latches from the IV bus and. |

| 000                |                                                         |                   | 16 IVO   |            |                                                                                                                                                       | for the synchronous 8X372, from the UD bus, MCLK also synchronizes IV address selection                        |

| UIC 10             | E 8                                                     | 15 WC             | 14       | sc         | Select Command—active high input from MicroController                                                                                                 |                                                                                                                |

| ME 11              | 80                                                      | 14 SC             | 14       | 30         | to enable IV address input from the IV bus for device selection                                                                                       |                                                                                                                |

| GND 12             | 13 MCLK                                                 |                   | 15       | wc         | Write Command—active high input from MicroController                                                                                                  |                                                                                                                |

| T                  | OP VIEW                                                 |                   |          |            | to enable the writing of data into the data latches from the IV bus, provided UIC is not low                                                          |                                                                                                                |

| ORDE               | R NUMB                                                  | ERS               | 16-23    | IVO-IV7    | Interface Vector Input/Output Busthree-state,                                                                                                         |                                                                                                                |

| N8X372N or N8X376N |                                                         |                   |          |            | bidirectional MicroController data bus, IVO corresponds to UD0                                                                                        |                                                                                                                |

|                    | N8X372I or N8X376I<br>72I/883B or S8X372I/883C          |                   | 24       | Vcc        | +5V power supply                                                                                                                                      |                                                                                                                |

Figure 1. Logic Diagram for 8X372/8X376 I/O Ports

#### **FUNCTIONAL OPERATION**

#### **UD Bus Control**

As shown in Table 1, the User Data (UD) bus interface is controlled by the  $\overline{UIC}$  and  $\overline{UOC}$  inputs. For the 8X372, data input from the UD bus is written synchronously with MCLK, that is, with  $\overline{UIC}$  low, information is written into the data latches only when MCLK is high. In the case of the 8X376, data input is asynchronous, in that, with  $\overline{UIC}$  low, data is latched in without regard to the level of MCLK (Note To avoid the possibility of processor error when using the saynchronous 8X376, the  $\overline{IV}$  bus should not be read during the time the data latches are changing due to user input.) Output drivers on the UD bus are enabled when UOC is low and  $\overline{UIC}$  is high

Table 1. INPUT/OUTPUT CONTROL OF UD BUS

| UIC | UOC  | MCLK | FUNCTION OF UD BUS |             |  |  |  |  |

|-----|------|------|--------------------|-------------|--|--|--|--|

| DIC | 1000 | MCLK | 8X372              | 8X376       |  |  |  |  |

| Н   | L    | X    | Output data        | Output data |  |  |  |  |

|     | X    | I H  | Input data         | Input data  |  |  |  |  |

|     | X    | L L  | Inactive           | Input data  |  |  |  |  |

| H   | Н    | X    | Inactive           | Inactive    |  |  |  |  |

X = don't care

#### **IV** Bus Control

Input/output control of the IV bus is shown in Table 2; this bus is controlled by SC, WC, ME, MCLK and the current state of the internal address selection latch. AS shown in Table 2, UIC is required to indicate priority of the UD bus for data input operations. The selection latch in the I/O port stores the result of the most recent IV address selection. The latch is set when the internally preprogrammed address of the port matches the address on the IV bus during an address-selection operation (SC = MCLK = High/WC = Low). The latch is cleared when the two 8-bit address patterns are in disagreement. The IV bus can transfer data only when the selection latch is set. As shown in the APPLICATION DIAGRAM, the MicroController Left Bank (LB) and Right Bank (RB) outputs can control the ME inputs for two banks of I/O devices, thus, acting as a ninth address bit.

Table 2. INPUT/OUTPUT CONTROL OF IV BUS

| ME | sc | wc | MCLK | UIC | SELECTION<br>LATCH | FUNCTION OF IV BUS         |

|----|----|----|------|-----|--------------------|----------------------------|

| L  | L  | L  | X    | Х   | Set                | Output Data                |

| L  | L  | Н  | Н    | Н   | Set                | Input Data                 |

| L  | Н  | L  | н    | Х   | х                  | Input Address*             |

| L  | Н  | н  | н    | н   | x                  | Input data<br>and address* |

| L  | Н  | Н  | Н    | L   | Х                  | Input Address*             |

| L  | Х  | Н  | L    | Х   | х                  | Inactive                   |

| L  | Н  | Х  | L    | Х   | х                  | Inactive                   |

| L  | L  | Н  | Н    | L   | X                  | Inactive                   |

| L  | L  | Х  | X    | Х   | Not Set            | Inactive                   |

| Н  | X  | ×  | X    | ×   | Х                  | Inactive                   |

X = don't care

Data is written into the data latches of a selected device from the  $\overline{\text{IV}}$  bus when WC, MCLK, and  $\overline{\text{UIC}}$  are all high and

$\overline{\text{ME}}$  is low. To prevent data-input conflicts, inputs from the  $\overline{\text{IV}}$  bus are inhibited when  $\overline{\text{UIC}}$  is low; under all other conditions, the  $\overline{\text{IV}}$  and UD busses operate independently Output drivers on the  $\overline{\text{IV}}$  bus of a selected device are enabled when  $\overline{\text{ME}}$ , WC, and SC are all low and the address selection latch is set. With SC and WC both high (shaded entry of Table 2), the bit pattern present on  $\overline{\text{IV0-IV7}}$  is interpreted as both input data and  $\overline{\text{IV}}$  address. Provided  $\overline{\text{UIC}}$  is high, the data is latched into the data latches whether or not the I/O port has been previously selected. If the preprogrammed address of the I/O port matches the bit pattern on  $\overline{\text{IV0-IV7}}$  when SC and WC are both high, the selection latch is set; otherwise, it is reset. (Note *The MicroController never drives both SC and WC high at the same time.*)

#### **Bus Logic Levels**

Data written into the I/O port from either bus will appear inverted when read from the other bus. Data written into either bus will not be inverted when read from the same bus. (Note. A logic "1" in MicroController software corresponds to a high level on the UD bus even though the IV bus is inverted.) Both the 8X372 and 8X376 wakeup with the address selection latch in the unselected state and all data bits latched at the "logic 1" level (UD bus outputs high if enabled).

#### ADDRESS PROGRAMMING AND ADDRESS PROTECT

#### **Programming Procedures**

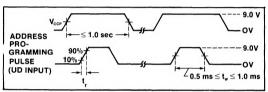

Both 8X372 and 8X376 can be programmed to respond to any address within a range of  $0_{10}$  through  $255_{10}$ . In an unprogrammed state, low level ( $\leq 0.8V$ ) inputs on all  $\overline{IV}$  bus lines (address  $255_{10}$ ) will select the device. To program a given address bit to match a high level ( $\geq 2.0V$ ) input on the corresponding  $\overline{IV}$  pin (a logical "0" to the MicroController), the counterpart UD-bus pin must be pulsed according to Table 3 and the following procedures:

- Step 1: Set all control inputs to the inactive state—  $\overline{UIC} = \overline{UOC} = \overline{ME} = V_{CC} \text{ and } SC = WC = MCLK = GND; leave the UD and <math>\overline{IV}$  bus pins open.

- Step 2: Increase V<sub>CC</sub> to V<sub>CCP</sub>.

- Step 3: After V<sub>CC</sub> has stabilized, apply a single programming pulse (Figure 2) to the user-bus bit that corresponds to the desired high-level  $\overline{\text{IV}}$  address bit. The I/O port is programmed from the user bus (UD0-UD7) for addressing from the MicroController bus ( $\overline{\text{IV0-IV7}}$ ).

- Step 4: Return V<sub>cc</sub> to 0-volts. (Note. If the programming of all address bits is completed in less than 1-second, V<sub>cc</sub> can remain at 9.0-volts for the required interval of time.)

- Step 5: Step 1 through 3 are applicable to the programming of each address bit that requires a high-level  $\overline{\mathsf{IV}}$  match.

<sup>\*</sup> Selection latch is updated

Table 3. PROGRAMMING SPECIFICATIONS

| PARAMETERS                           |      | LIMIT | S    | UNITS |

|--------------------------------------|------|-------|------|-------|

| PARAMETERS                           | Min  | Тур   | Max  | UNITS |

| VCCP — Programming supply voltage    |      |       |      |       |

| Address                              | 8.75 | 9.0   | 9.25 | l v   |

| Protect                              |      | 0     |      | ٧     |

| Maximum time V <sub>CCP</sub> >5 25V |      |       | 10   | Sec   |

| Programming voltage<br>Address       | 8 75 | 90    | 9 25 | v     |

| Protect                              | 8.75 |       | 9.25 | V     |

| Programming current<br>Address       |      |       | 5    | mA    |

| Protect                              |      |       | 50   | mA    |

| tr — Programming pulseirise time     |      |       |      |       |

| Address                              | 10   | Ĺ     | 100  | μS    |

| Protect                              | 10   |       | 100  | μS    |

| tω-Programming pulse width           | 0.5  |       | 10   | mS    |

Figure 2. Address Programming Pulse

Step 6: To verify that the address is properly programmed, return V<sub>CC</sub> to +5V, set IVO-IV7 to the desired (inverted) binary address pattern, set ME = WC = Low and SC = MCLK = High. If

there are no programming errors, subsequent data written from  $\overline{\text{IV0-IV7}}$  (WC = High) will appear inverted on UD0-UD7.

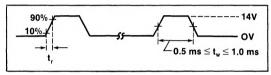

#### **Address Protect**

Step 2:

After programming the I/O Port, steps should be taken to isolate the address circuits and make these circuits permaently immune to further change.

Step 1: Set  $V_{CC}$  and all control inputs to 0-volts ( $V_{CC}$ =  $\overline{UIC}$  =  $\overline{UOC}$  =  $\overline{ME}$  = SC = WC = MCLK = 0V);  $\overline{IVO}$ - $\overline{IV7}$  = open circuit.

Taking one pin at a time, apply a protect programming pulse (Figure 3) to each userbus bit (UD0-UD7)—refer to Table 3 for min/max specifications pertaining to voltage and current.

Figure 3. Protect Programming Pulse

Step 3: Verify that the address circuits for each bit is isolated by applying 9-volts, in turn, to each user-bus pin (UD0-UD7) and measuring less than 200 microamperes of input current. (Note. Setup conditions are the same as those in Step 1.)

#### DC ELECTRICAL CHARACTERISTICS

COMMERCIAL 475V  $\leq$  V<sub>CC</sub>  $\leq$  5.25V, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C MILITARY 4.5V  $\leq$  V<sub>CC</sub>  $\leq$  55V, -55°C  $\leq$  T<sub>C</sub>  $\leq$  125°C

#### ABSOLUTE MAXIMUM RATINGS

|      | PARAMETER                  | RATING      | UNIT |

|------|----------------------------|-------------|------|

| Vcc  | Power supply voltage3      | +7          | Vdc  |

| VIN  | Input voltage <sup>3</sup> | +55         | Vdc  |

| TSTG | Storage temperature range  | -65 to +150 | °C   |

|                 |                                                            | TEGT 001/0/17/01/0                                       | LIMIT | S (COMN | IERCIAL) | LIMITS (MILITARY) |      |      |      |  |

|-----------------|------------------------------------------------------------|----------------------------------------------------------|-------|---------|----------|-------------------|------|------|------|--|

|                 | PARAMETER                                                  | TEST CONDITIONS                                          | Min   | Тур     | Max      | Min               | Тур  | Max  | UNIT |  |

| Vcc             | Supply Voltage                                             |                                                          | 4.75  | 5       | 5 25     | 4.5               | 5    | 5.5  | ٧    |  |

| ViH             | High Level Input Voltage                                   |                                                          | 20    |         |          | 20                |      |      | ٧    |  |

| VIL             | Low Level Input Voltage                                    |                                                          |       |         | 0.8      |                   |      | 0.8  | ٧    |  |

| VcL             | Input Clamp Voltage                                        | V <sub>CC</sub> =M <sub>I</sub> n; I <sub>I</sub> =-10mA |       |         | -1.5     |                   |      | -1.5 | ٧    |  |

| lін             | High Level Input Current1                                  | V <sub>CC</sub> =Max; V <sub>IH</sub> = 2.7V             |       | 5.0     | 100      |                   | 5.0  | 100  | μА   |  |

| 1 <sub>IL</sub> | Low Level Input Current <sup>1</sup>                       | V <sub>CC</sub> = Max, V <sub>IL</sub> = 0.5V            |       | -350    | -550     |                   | -350 | -550 | μА   |  |

| VoL             | Low Level Output Voltage                                   | V <sub>CC</sub> =Min, I <sub>OL</sub> =16mA              |       |         | 0 55     |                   | 0.55 | ٧    |      |  |

|                 | User Bus (UD0-UD7)                                         | V <sub>CC</sub> =Min, I <sub>OL</sub> =24mA              |       |         | 0 55     |                   |      | 0.55 | ٧    |  |

| Vон             | High Level Output Voltage                                  | V <sub>CC</sub> = Min; I <sub>OH</sub> = -3.2mA          | 24    |         |          | 2.4               |      |      | >    |  |

| los             | Short Circuit Output Current <sup>2</sup> IV Bus (IVO-IV7) | V <sub>CC</sub> = Max                                    | -20   |         |          | -20               |      |      | mA   |  |

|                 | UD Bus (UD0-UD7)                                           | V <sub>CC</sub> = Max                                    | -10   |         |          | -10               |      |      | mA   |  |

| Icc             | Supply Current                                             | V <sub>CC</sub> =Max, ME=UOC=V <sub>CC</sub>             |       | 90      | 150      |                   | 90   | 150  | mA   |  |

NOTES

- 1. The input current includes the Three-state leakage current of the output driver on the data lines.

- 3 These limits do not apply during address programming.

2. Only one output may be shorted at a time.

8X372/8X376

### **AC ELECTRICAL CHARACTERISTICS**

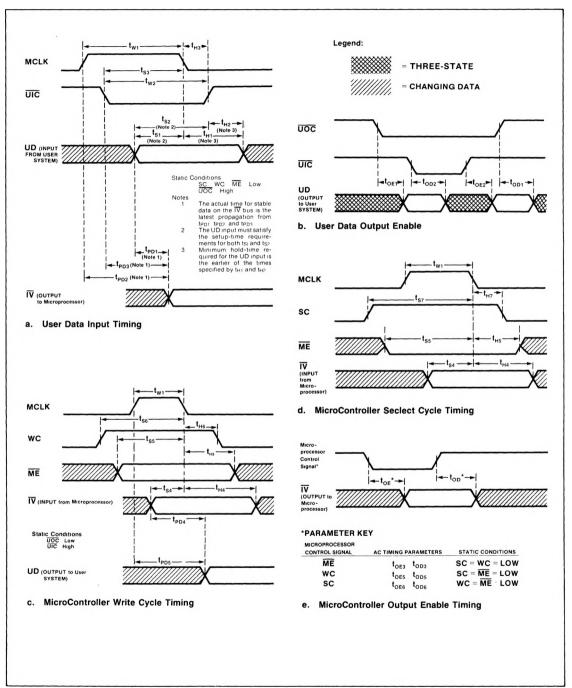

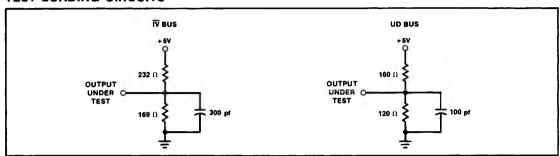

COMMERCIAL 475V  $\leq$  V<sub>CC</sub>  $\leq$  525V, 0° C  $\leq$  T<sub>A</sub>  $\leq$  70° C MILITARY 4.5V  $\leq$  V<sub>CC</sub>  $\leq$  55V, -55° C = T<sub>C</sub>  $\leq$  125° C LOADING See TEST LOADING CIRCUITS

|                    | PARAMETER                                     | REFER        | ENCES'        | TEST CONDITIONS                                      | LIMITS (COMMERCIAL) |          |     | L) LIMITS (MILITARY) |          |          | UNIT |

|--------------------|-----------------------------------------------|--------------|---------------|------------------------------------------------------|---------------------|----------|-----|----------------------|----------|----------|------|

|                    | PARAMETER                                     | FROM         | то            | IEST CONDITIONS                                      | Min                 | Тур      | Max | Min                  | Тур      | Max      | UNIT |

| Pulse V            | Vidths:<br>Clock High                         | †MCLK        | <b>∮</b> MCLK |                                                      | 35                  |          |     | 35                   |          |          | ns   |

| tw2                | User Input Control                            | ∳ŪĪĈ         | tuic          | MCLK = High                                          | 35                  |          |     | 35                   |          |          | ns   |

| Propag<br>tPD1     | ation Delays:<br>UD Propagation<br>Delay      | UD           | i⊽            | MCLK=High<br>SC=WC=ME=UIC=Low                        |                     |          | 30  |                      |          | 30       | ns   |

| tpD2               | UD Clock Delay<br>(8X732 only)                | †MCLK        | īV            | UD = Stable,<br>SC = WC = ME = UIC = Low             |                     |          | 50  |                      |          | 50       | ns   |

| t <sub>PD3</sub>   | UD Input Delay                                | <u>†⊓ic</u>  | īv            | UD = Stable, MCLK = High;<br>SC = WC = ME = Low      |                     |          | 50  |                      |          | 50       | ns   |

| tPD4               | IV Data<br>Propagation Delay                  | īV           | UD            | MCLK=WC=UIC=High,<br>ME=UOC=SC=Low                   |                     |          | 45  |                      |          | 45       | ns   |

| tPD5               | IV Data<br>Clock Delay                        | †MCLK        | UD            | WC = UIC = High; IV = Stable,<br>ME = UOC = SC = Low |                     |          | 55  |                      |          | 55       | ns   |

| -                  | Enable Timing:                                |              |               |                                                      |                     |          |     |                      |          |          |      |

| tOE1               | UD Output Enable                              | fnoc         | UD            | UIC = High                                           | -                   |          | 30  |                      |          | 30       | ns   |

| toE2               | UD Input Recovery                             | tuic         | UD            | UOC=Low                                              |                     | <u> </u> | 30  |                      |          | 30       | ns   |

| toe3               | IV Data<br>Master Enable                      | ₩Ē           | īv            | WC = SC = Low                                        |                     |          | 22  |                      |          | 25       | ns   |

| toes               | IV Data<br>Write Recovery                     | ∳wc          | īv            | SC = ME = Low                                        |                     |          | 25  |                      |          | 25       | ns   |

| toe6               | IV Data<br>Select Recovery                    | <b>∤</b> sc  | īV            | SC = ME = Low                                        |                     |          | 25  |                      |          | 25       | ns   |

| Output             | Disable Timing:                               |              |               |                                                      |                     |          |     |                      |          |          |      |

| toD1               | UD Output<br>Disable                          | fuoc         | UD            | UIC = High                                           |                     |          | 25  |                      |          | 25       | ns   |

| tod2               | UD Input<br>Override                          | ₩ŪÏC         | UD            | UOC=Low                                              |                     |          | 30  |                      |          | 30       | ns   |

| top32              | IV Data<br>Master Disable                     | †ME          | īv            | WC = SC = Low                                        |                     |          | 20  |                      |          | 20       | ns   |

| toD42              | IV Data<br>Write Override                     | twc          | īv            | SC = ME = Low                                        |                     |          | 20  |                      |          | 20       | ns   |

| t <sub>OD5</sub> 2 | IV Data<br>Select Override                    | tsc          | īv            | WC=ME=Low                                            |                     |          | 20  |                      |          | 20       | ns   |

| Setup '            | Times:                                        |              | -             |                                                      |                     | l –      |     | <b></b> -            | <b>-</b> | <u> </u> |      |

| ts1                | UD Clock Setup<br>Time (8X372 only)           | UD           | <b>∮</b> MCLK | ŨIC = Low                                            | 15                  |          |     | 15                   |          |          | ns   |

| ts2                | UD Control Setup<br>Time                      | UD           | fuic          | MCLK = High                                          | 15                  |          |     | 15                   |          |          | ns   |

| ts3                | User Input Control<br>Setup Time (8X372 only) | ∳ <u>uic</u> | <b>∳</b> MCLK |                                                      | 25                  |          |     | 25                   |          |          | ns   |

| ts4                | IV Data<br>Setup Time                         | īV           | ₽MCLK         | WC=High or SC=High,<br>ME=Low, UIC=High              | 35                  |          |     | 35                   |          |          | ns   |

| ts53               | IV Master Enable<br>Setup Time                | ∳ME          | <b>∮</b> MCLK | WC=High or SC=High,<br>UIC=High                      | 30                  |          |     | 30                   |          |          | ns   |

| ts6                | IV Write Control<br>Setup Time                | twc          | <b>∮</b> MCLK | SC=ME=Low, UIC=High                                  | 30                  |          |     | 30                   |          |          | ns   |

8X372/8X376

### AC ELECTRICAL CHARACTERISTICS (Cont'd)

|                   | DARAMETER                                    | REFERENCES    |             | TEST CONDITIONS                         | LIMIT | S (COMM | IERCIAL) | LIMITS (MILITARY) |     |     |      |

|-------------------|----------------------------------------------|---------------|-------------|-----------------------------------------|-------|---------|----------|-------------------|-----|-----|------|

|                   | PARAMETER                                    | FROM          | то          | TEST CONDITIONS                         | Min   | Тур     | Max      | Min               | Тур | Max | UNIT |

| ts7               | IV Select Control<br>Setup Time              | tsc           | †MCLK       | WC = ME = Low                           | 30    |         |          | 30                |     |     | ns   |

| Hold T            | imes:                                        |               |             |                                         |       |         |          |                   |     |     |      |

| tH1               | UD Clock Hold<br>Time (8X372 only)           | <b>∮</b> MCLK | DD          | UIC = Low                               | 15    |         |          | 15                |     |     | ns   |

| t <sub>H2</sub>   | UD Control<br>Hold Time                      | tuic          | UD          | MCLK = High                             | 15    |         |          | 15                | }   |     | ns   |

| tнз               | User Input Control<br>Hold Time (8X372 only) | <b>∮</b> MCLK | tuic        |                                         | 0     |         |          | 0                 |     |     | ns   |

| t <sub>H4</sub>   | IV Data<br>Hold Time                         | ∳MCLK         | īv          | WC=High or SC=High;<br>ME=Low, UIC=High | 5     |         |          | 5                 |     |     | ns   |

| t <sub>H5</sub> 3 | IV Master Enable<br>Hold Time                | <b>∮</b> MCLK | †ME         | WC=High or SC=High,<br>UIC=High         | 0     |         |          | 0                 |     |     | ns   |

| t <sub>H6</sub>   | IV Write Control<br>Hold Time                | †MCLK         | ∳wc         | SC = ME = Low, UIC = High               | 0     |         |          | 0                 |     |     | ns   |

| t <sub>H7</sub>   | IV Select Control<br>Hold Time               | ₽MCLK         | <b>∔</b> sc | WC = ME = Low                           | 0     |         |          | 0                 |     |     | ns   |

#### Notes

- 1 All measurements to the  $\overline{\text{IV}}$  bus assumes the address selection latch is set

- 2 These parameters are measured with a capacitive loading of 50pf and represent the output driver turn-off time

- 3 If ME is to be high (inactive), it must be setup before the rising edge and held after the falling edge of MCLK to avoid unintended writing into or selection of the I/O port.

Figure 2. Timing Diagram

### **TEST LOADING CIRCUITS**

#### **APPLICATIONS**

One way of using I/O Ports in a microprocessor-based system is shown in the following application diagram; there are many other ways of implementing I/O functions with these parts, both singly and in combination. By proper control of the UIC and UOC lines, the user can implement

bidirectional data transfers, exercise system control, and/or read system status. In the concept shown here, I/O Port #1 is setup for bidirectional data transfers and I/O Ports #2 and #3, respectively, serve as dedicated output and input devices.