Host System (primary port); the host can be almost any bus-

oriented device-another processor, a minicomputer, or a main-

frame computer. The host has 8-bit (byte) or 16-bit (word) access

to the primary port; data can be read-from or written-into any

memory location as determined by the primary-port address and

control lines. The secondary port (8X305 bus) consists of eight

input/output lines and four bus control lines. To implement the

secondary-port interface, an 8-bit memory location is addressed

during one machine cycle and, during another cycle, data is read

or written under control of the secondary (8X305) processor. Both primary and secondary ports feature three-state outputs

Besides the convenience and economy of a two-port memory,

the array also provides simple handshake control via two 8-bit

flag registers, logic to facilitate DMA transfers, and a write-

protect feature for the primary port in both byte and word modes

and both ports are bidirectional.

of operation.

#### **FEATURES**

- 16-byte/2-port interface

- · 8- or 16-bit primary port (Host) interface (User selectable)

- · 8-bit secondary port interface

- Two 8-bit flag registers (handshake control)

- DMA or programmed I/O operation

- Two three-state bidirectional ports

- Secondary port is bus compatible with 8X305

- Single 5V supply

- 40-pin package

#### ARCHITECTURAL OVERVIEW

The SignetIcs 8X320 Bus Interface Register Array (Figure 1) is a dual-port RAM memory designed for use between a host processor and a peripheral processor. Specifically, the register array provides a convenient and economical interface between the 8X305 (or 8X300) Microcontroller (secondary port) and User's

#### BLOCK DIAGRAM

SECONDARY PORT PRIMARY PORT 16 X 8 MEMORY FLAG REGISTER FLAG REGISTER UCED DOPT RIMARY ADDRESS PRIMARY ADDRESS ADDRESS DECODE BYTE - 08 BYTE + 18 WORD - Note WORD - Not SECONDARY ADDRESS 608 SECONDARY ADDRESS 618 GEN PURPOSE REGISTER GEN PURPOSE REGISTER PROTECT BIT PRIMARY ADDRESS RIMARY ADDRESS BYTE + 28 WORD + Note BYTE + 38 WORD + Not STATUS ME (19 SECONDARY ADDRESS 628 SECONDARY ADDRESS 638 (21) DMAR MCIK 2 8X305 PORT LOGIC (32) GEN PURPOSE REGISTER GEN PURPOSE REGISTER ws 22 SC RIMARY ADDRESS RIMARY ADDRESS 33 R/W WC. 23 BYTE + 48 WORD + Note BYTE - 58 WORD -+ Note SECONDARY ADDRESS 658 (34) PIOF USER-PORT SECONDARY ADDRESS 648 LOGIC 35 A3 (36) GEN PURPOSE REGISTER GEN PURPOSE REGISTER A2 PRIMARY ADDRESS PRIMARY ADDRESS 37 Δ 1 BYTE - 68 (38) WORD -+ Note 40 SECONDARY ADDRESS 668 SECONDARY ADDRESS 678 (39) B/W ADDRESS LATCHES GEN PURPOSE REGISTER GEN PURPOSE REGISTER AND DECODE LOGIC PRIMARY ADDRESS BYTE + 118 WORD + Note PRIMARY ADDRESS BYTE - 108 3 D7# WORD - Note SECONDARY ADDRESS 708 SECONDARY ADDRESS 718 4 D6A 5 D5A GEN PURPOSE REGISTER GEN PURPOSE REGISTER 10 - 24 PRIMARY ADDRESS RIMARY ADDRESS 6 D4A BYTE - 138 7 IV1 - 25 D3A WORD - Not WORD - Note SECONDARY ADDRESS 728 SECONDARY ADDRESS 738 8 D2A 8 11/2 -- 26) 8X305 RIVERS/RECEIVER 16 (9) D1A GEN PURPOSE REGISTER GEN PURPOSE REGISTER USER-PORT 113-(27) PRIMARY ADDRESS PRIMARY ADDRESS VERS/RECEIVER (10) D0A BYTE - 158 114-28 (11) D7B WORD - Note WORD - Note SECONDARY ADDRESS 748 SECONDARY ADDRESS 758 (12) D6B 115-(29) (13) D5B GEN PURPOSE REGISTER GEN PURPOSE REGISTER IV6 --(30) PRIMARY ADDRESS PRIMARY ADDRESS (14) D4B BYTE - 178 BYTE - 168 IV7 - 31 (15) D3R WORD - Note WORD - Note SECONDARY ADDRESS 768 SECONDARY ADDRESS 778 (16) D2B Note (17) D1R In The Word Mode, The Registers Are Addressed in Specific Pairs Byte 0/Byte 1, Byte 2/Byte 3, Byte 4/Byte 5 Byte 14/Byte 15, And 18 DOB Byte 16/Byte 17

Figure 1. Block Diagram of 8X320 Bus Interface Register Array

Signetics

|         |                                                                        |                                | N 1 DAGWAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                        |                                | N, I PACKAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |                                                                        |                                | ORDER NUMBERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |                                                                        |                                | N8X320N, N8X320I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PIN NO. |                                                                        | ARAMETER                       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1, 20   | GND                                                                    | Ground                         | Circuit ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2       | DMAE                                                                   | Direct Memory<br>Access Enable | Enables primary port to facilitate DMA transfers; does not affect secondary port.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3-18    | D0 <sub>A</sub> -D7 <sub>A</sub> /<br>D0 <sub>B</sub> -D7 <sub>B</sub> | Primary Data Port              | Sixteen 3-state lines used for data transfers to-and-from the primary data port; most significant bit is $D0_B$ and least significant bit is $D7_A$ .                                                                                                                                                                                                                                                                                                                                                                  |

| 19      | ME                                                                     | Master Enable                  | Enables secondary port when active low (ME).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21      | MCLK                                                                   | Master Clock                   | When MCLK is high, and 8X320 is enabled (ME = Low), a register location may be either<br>selected or written-into under control of SC and WC.                                                                                                                                                                                                                                                                                                                                                                          |

| 22      | SC                                                                     | Select Command                 | With SC high, WC low, MCLK high and $\overline{ME}$ low, data on $\overline{IV0}$ through $\overline{IV7}$ is interpreted as<br>an address. If any one of the 16 register addresses (60 <sub>8</sub> -77 <sub>8</sub> ) matches that on the I/O<br>(IV) bus, that particular register is selected and remains selected until another address<br>on the same bank (i.e. $\overline{ME}$ = low) is output on the I/O bus—at which time, the old<br>register is deselected and a new register may or may not be selected. |

| 23      | wc                                                                     | Write Command                  | With WC high, SC low, MCLK high, and $\overline{\text{ME}}$ low, the selected register stores contents of $\overline{\text{IVO}}-\overline{\text{IV7}}$ as data.                                                                                                                                                                                                                                                                                                                                                       |

| 24-31   | 100-107                                                                | Secondary Data Port            | Eight 3-state lines used to transfer data or I/O address to-and-from the secondary data port; most significant bit is $\overline{IVO}$ and least significant bit is $\overline{IV7}$ .                                                                                                                                                                                                                                                                                                                                 |

| 32      | ws                                                                     | Write Strobe                   | When active high, data appearing at the primary port (D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> ) is stored in the register array if the primary port is in the <i>write</i> mode.                                                                                                                                                                                                                                                                                                            |

| 33      | R/W                                                                    | Read/Write Control             | When this signal is high, primary port is in <i>read</i> mode; when signal is low, primary port is<br>in <i>write</i> mode.                                                                                                                                                                                                                                                                                                                                                                                            |

| 34      | PIOE                                                                   | Programmed I/O En-<br>able     | When active low, primary port operates in programmed input/output mode with register to be read-from or written-into selected by AO-A3.                                                                                                                                                                                                                                                                                                                                                                                |

| 35-38   | A0-A3                                                                  | Primary Port<br>Address Select | Selects register or register-pair that primary port is to read-from or write-into. Most significant bit is A3; least significant bit is A0.                                                                                                                                                                                                                                                                                                                                                                            |

| 39      | B/₩                                                                    | Byte / Word                    | When signal is high, the primary port operates in the byte (8-bit) mode; when signal is low, the primary port operates in the word (16-bit) mode.                                                                                                                                                                                                                                                                                                                                                                      |

| 40      | Vcc                                                                    | Power                          | +5 volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | <u> </u>                                                               |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

All barred symbols (DMAE, etc.) denote signals that are asserted (or active) when low (logical O), signals that are not barred are asserted in the high state (logical 1)

#### OPERATING CHARACTERISTICS Memory Organization

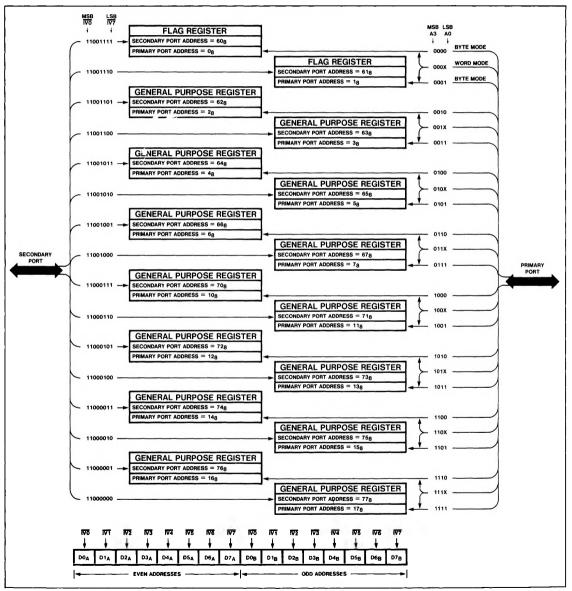

Memory and address correlation for the 16-register array is shown in Figure 2. From the primary port, the sixteen 8-bit registers can be addressed in either (8-bit) or word (16-bit) format; in the word mode, the registers are addressed in pairs —  $0g/1g, 2g/3g, 4g/5g, \ldots 14g/15g$ , and 16g/17g. From the secondary port, all registers are addressed in byte format—608 through 778. The memory consists of two 8-bit flag registers and fourteen 8-bit general-purpose registers. The flag registers facilitate information transfers between the two ports and, in addition, they protect certain registers from being written into from the primary port.

Figure 2. Memory and Address Organization for the 8X320

In either byte or word mode, the write-protect logic, implemented by bits F0 and F1 of register 60g, inhibits the primary port from writing into addresses 16g and 17g, respectively. Both write-protect bits (F0 and F1) can be read or written from the secondary port; the bits are read-only from the primary port.

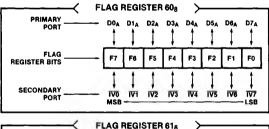

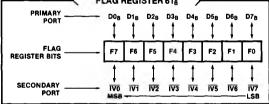

As shown in Table 1, flag bits F2 through F7 of 60g and F0 through F7 of 61g are controlled by the fourteen general-purpose registers. When any one of these registers is written into by either port, the corresponding flag bit for that register is automatically set by Internal logic of the 8x320. When information is read from any register, the corresponding flag bit must be reset by user software. Except for the write-protect bits, all other flag bits can be read or reset from the primary or the secondary port. Table 2 shows the relationship between bits of the flag registers and bits of the primary and secondary ports.

#### Table 1. CONTROL OF THE TWO FLAG REGISTERS

| Flag                                       | 60 <sub>8</sub> (0 <sub>8</sub> ) | F2 | F3 | F4 | F5 | F6 | F7 |    |            |    |    |    |    |    |    |

|--------------------------------------------|-----------------------------------|----|----|----|----|----|----|----|------------|----|----|----|----|----|----|

| Registers                                  | 61 <sub>8</sub> (1 <sub>8</sub> ) |    |    |    |    |    |    | FO | <b>F</b> 1 | F2 | F3 | F4 | F5 | F6 | F7 |

| Octal<br>Address of<br>Controlling<br>Byte | Primary                           | 2  | 3  | 4  | 5  | 6  | 7  | 10 | 11         | 12 | 13 | 14 | 15 | 16 | 17 |

|                                            | Secondary                         | 62 | 63 | 64 | 65 | 66 | 67 | 70 | 71         | 72 | 73 | 74 | 75 | 76 | 77 |

#### Table 2. RELATIONSHIP BETWEEN FLAG REGISTER BITS AND THOSE OF PRIMARY AND SECONDARY PORTS

#### FUNCTION AND CONTROL OF PRIMARY PORT

The primary port provides an 8-bit (byte) or 16-bit (word) interface between the 16-byte memory and the user's host system. If the host is an 8-bit system (or 16-bit system operating in Byte mode), the sixteen bidirectional I/O lines must be tied together (DO<sub>A</sub> to DO<sub>B</sub>, D1<sub>A</sub> to D1<sub>B</sub>,... and D7<sub>A</sub> to D7<sub>B</sub>); when data is input or output on DO<sub>A</sub> through D7<sub>A</sub>, the remaining eight lines (DO<sub>B</sub> through D7<sub>B</sub>) are high-Z and vice-versa.

Other than the Byte/Word control line, specific operating characteristics of the primary port are controlled by two signals-PIOE (Programmed I/O Enable) and DMAE (Direct Memory Access Enable). When PIOE is active (low) and DMAE is inactive (high), the primary port operates in the programmed I/O mode - refer to Table 3; in this mode of operation, the register to be read-from or written-into is determined by four address lines (A0 through A3) and the Byte/Word control line-see Figure 2 and Table 4. In the DMA mode of operation, A1, A2, and A3 are not used; data is read-from or written-into preassigned registers: bytes 168 (768) and 178 (778) for the byte mode of operation and bytes 148 (748)/158 (758) and 168 (768)/178 (778) for the word mode of operation. In both cases, switching between bytes 16g and 17g in the byte mode and 14g/15g and 16g/17g in the word mode is controlled by A0 (the least significant address bit), Refer to Table 5.

#### Table 3. MODE CONTROL OF PRIMARY PORT

| MODE              | PIOE | DMAE |

|-------------------|------|------|

| Disabled (output) | 1    | 1    |

| Programmed I/O    | 0    | 1    |

| DMA               | ×    | 0    |

X = Don't Care

Table 4 defines programmed I/O operation of the primary port in terms of read/write functions and Byte/Word control. In the byte mode, data is read-from or written-into the even addresses (08, 28, 48, 68, 108, 128, 148, and 169) via data lines D0A through D7A; data is read-from or written-into odd addresses (18, 38, 58, 78, 118, 138, 158, and 179) via data lines D0B through D7B. When A0 is low (logical 0), even addresses are selected and when A0 is high (logical 1), odd addresses are selected; thus, A0 is the LSB of a 4-bit address. In the word mode, the state of A0 is irrelevant, since both the odd and even bytes are, simultaneously, read-from or written-into; thus, a register pair is selected by a 3-bit address, A1 being the LSB.

In the DMA mode of operation with DMAE set to 0 and other conditions satisfied, data is directly transferred to-or-from specified memory locations under control of Byte/Word, R/W, and A0. The state of the Byte/Word control line determines whether the data word is 8 bits or 16 bits. The A0 address line correlates eight of

#### Table 4. PRIMARY PORT OPERATING IN PROGRAMMED I/O MODE

|       |          | AO | DO <sub>A</sub> -D7 <sub>A</sub><br>(Even Addresses) | D0 <sub>B</sub> -D7 <sub>B</sub><br>(Odd Addresses) |

|-------|----------|----|------------------------------------------------------|-----------------------------------------------------|

| Read  | 0 (Word) | X  | Stored Data                                          | Stored Data                                         |

| Read  | 1 (Byte) | 0  | Stored Data                                          | HI-Z                                                |

| Read  | 1 (Byte) | 1  | HI-Z                                                 | Stored Data                                         |

| Write | 0 (Word) | х  | Write                                                | Write                                               |

| Write | 1 (Byte) | 0  | Write                                                | No Change                                           |

| Write | 1 (Byte) | 1  | No Change                                            | Write                                               |

X = Don't Care

the sixteen data lines (D0A-D7A or D0B-D7B) with the proper byte/word location. Thus, in the word mode, the exchange of data between the memory and the primary port occurs via D0A-D7A for bytes 14g and 16g and via D0B-D7B for bytes 15g and 178. The byte mode of operation is similar, except that the unused eight lines are three-stated.

#### FUNCTION AND CONTROL OF SECONDARY PORT

The secondary port provides an 8-bit interface between the sixteen memory registers and the 8X305 (or other processor). As shown in Table 6, the secondary-port interface is controlled by five input signals and a status latch. The status latch is set when SC is high (MCLK high/ME low) and a valid memory address (608-778) is presented to the 8X320 via the secondary data port (IVO-IV7). The latch is cleared by internal logic when an invalid memory address is presented at the secondary port. In all read/write operations from the secondary port, the status latch acts like a master enable; data can be transferred only if the status latch is set.

| MODE  | BYTE/WORD | AO | DOA-D7A                                | DOB-D7B                                |

|-------|-----------|----|----------------------------------------|----------------------------------------|

| Read  | 0 (Word)  | 0  | Data stored in<br>byte 14 <sub>8</sub> | Data stored in<br>byte 15 <sub>8</sub> |

| Read  | 0 (Word)  | 1  | Data stored in<br>byte 16 <sub>8</sub> | Data stored in<br>byte 17 <sub>8</sub> |

| Read  | 1 (Byte)  | 0  | Data stored in<br>byte 16 <sub>8</sub> | HI-Z                                   |

| Read  | 1 (Byte)  | 1  | HI-Z                                   | Data stored in byte 17 <sub>8</sub>    |

| Write | 0 (Word)  | 0  | Write to byte<br>148                   | Write to byte<br>158                   |

| Write | 0 (Word)  | 1  | Write to byte<br>168                   | Write to byte<br>178                   |

| Write | 1 (Byte)  | 0  | Write to byte<br>16 <sub>8</sub>       | HI-Z                                   |

| Write | 1 (Byte)  | 1  | HI-Z                                   | Write to byte<br>17 <sub>8</sub>       |

#### Table 5. DMA OPERATION OF THE PRIMARY PORT

| Table 6. | FUNCTIONAL | CONTROL OF | SECONDARY PORT |

|----------|------------|------------|----------------|

|          |            |            |                |

| ME | SC1 | WC1 | MCLK | R/W | STATUS<br>LATCH | FUNCTION OF SECONDARY BUS                                                                                                                                                                                                                                                                                                        |

|----|-----|-----|------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L  | L   | L   | X    | x   | Set             | Output data from 8X320 memory to 8X305                                                                                                                                                                                                                                                                                           |

| L  | L   | н   | н    | н   | Set             | Data from 8X305 is input and written-into a previously-selected memory loca-<br>tion of the 8X320 (Note 2).                                                                                                                                                                                                                      |

| L  | L   | н   | н    | L   | Set             | With the primary port in the write mode $(R/\overline{W} = 0)$ , the secondary port is overridden and cannot write to the same register addressed by the primary port, however, the register addressed by the primary port can be read and any other register can be read-from or written-into from the secondary port (Note 2). |

| L  | н   | L   | н    | ×   | x               | Data transmitted to the secondary port via the $\overline{V}$ bus is interpreted as an address; if address is within range of 60 <sub>8</sub> -77 <sub>8</sub> the memory status latch is subsequently set.                                                                                                                      |

| L  | L   | н   | L    | x   | X               | Inactive                                                                                                                                                                                                                                                                                                                         |

| L  | н   | L   | L    | x   | X               | Inactive                                                                                                                                                                                                                                                                                                                         |

| L  | L   | ×   | x    | ×   | Not Set         | Inactive                                                                                                                                                                                                                                                                                                                         |

| н  | ×   | X   | x    | x   | X               | Inactive                                                                                                                                                                                                                                                                                                                         |

Notes:

1 The SC and WC lines should never both be high at the same time, the 8X305 processor never generates this condition

2 During read or write operations, the same register can be simultaneously addressed from either port. For any write operation by both ports on the same register, the primary port has priority, other than this, the 8X320 does not indicate error conditions or resolve conflicts ÷ . -----

3. X = Don't Care.

### DC CHARACTERISTICS 0°C $\leq$ T\_A $\leq$ 70°C; 4.75V $\leq$ V\_{CC} $\leq$ 5.25V

| PARAMETER           |                                                                    | TEST CONDITIONS <sup>1, 2</sup>                  | Min Typ |   | Max               | UNIT |

|---------------------|--------------------------------------------------------------------|--------------------------------------------------|---------|---|-------------------|------|

| Vcc                 | Supply voltage                                                     |                                                  | 4.75    | 5 | 5.25              | V    |

| VIN (L)             | Low level input voltage                                            |                                                  |         |   | 0.80              | v    |

| VIN (H)             | High level input voltage                                           |                                                  | 2.0     |   |                   | v    |

| VOL                 | Low level output voltage                                           | $V_{CC} = 4.75V; I_{OL} = 16mA$                  |         |   | 0.55              | v    |

| VOH                 | High level output voltage                                          | $V_{CC} = 4.75V; I_{OH} = -3mA$                  | 2.40    |   |                   | v    |

| VCL                 | Input clamp voltage                                                | l₁ = −5mA                                        |         |   | -1.00             | v    |

| lcc                 | Supply current                                                     | V <sub>CC</sub> = 5.25V (Both ports high-Z)      |         |   | 270               | mA   |

| los                 | Short circuit output current <sup>3</sup>                          | V <sub>CC</sub> = 4.75V                          | -20     |   | -100              | mA   |

| IN (L)              | WC, MCLK, SC, & ME                                                 | $V_{CC} = 5.25V; V_{IL} = 0.50V$                 |         |   | -1.0              | mA   |

| 4N (L)              | B/₩                                                                | V <sub>CC</sub> = 5.25V; V <sub>IL</sub> = 0.50V |         |   | -1.6              | mA   |

| IN (L)              | A0-A3                                                              | V <sub>CC</sub> = 5.25V; V <sub>IL</sub> = 0.50V |         | [ | -1.0              | mA   |

| IN (L)              | DMAE                                                               | $V_{CC} = 5.25V; V_{IL} = 0.5V$                  |         |   | -800              | μA   |

| IN (L)              | WS, PIOE, & R/W                                                    | $V_{CC} = 5.25V; V_{IL} = 0.5V$                  | T       | 1 | -400              | μA   |

| <sup>I</sup> IN (L) | IVO-IV7                                                            | $V_{CC} = 5.25V; V_{IL} = 0.5V$                  |         |   | -400<br>each line | μA   |

| <sup>I</sup> iN (L) | D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> | $V_{CC} = 5.25V; V_{IL} = 0.5V$                  |         |   | -400<br>each line | μA   |

| IN (H)              | WC, SC, MCLK, & ME                                                 | V <sub>CC</sub> = 5.25V; V <sub>IH</sub> = 5.25V |         |   | 100               | μA   |

| IN (H)              | B/W                                                                | V <sub>CC</sub> = 5.25V; V <sub>IH</sub> = 5.25V |         |   | 240               | μA   |

| IN (H)              | AO                                                                 | V <sub>CC</sub> = 5.25V; V <sub>IH</sub> = 5.25V |         |   | 120               | μA   |

| IN (H)              | A1-A3                                                              | V <sub>CC</sub> = 5.25V; V <sub>IH</sub> = 5.25V |         |   | 60                | μA   |

| IN (H)              | DMAE                                                               | V <sub>CC</sub> = 5.25V; V <sub>IH</sub> = 5.25V |         |   | 120               | μA   |

| IN (H)              | WS, PIOE, & R/W                                                    | V <sub>CC</sub> = 5.25V; V <sub>IH</sub> = 5.25V |         |   | 60                | μA   |

| lin (H)             | IVO-IV7 and DOA-D7A/DOB-D7B                                        | V <sub>CC</sub> = 5.25V; V <sub>IH</sub> = 5.25V |         |   | 100               | μA   |

Notes

1 Operating temperature ranges are guaranteed after terminal equilibrium has been

reached

2 All voltages are measured with respect to ground terminal

3 Short only one output at a time

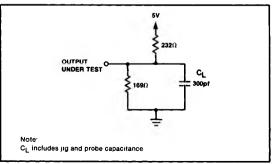

### **TEST CIRCUIT**

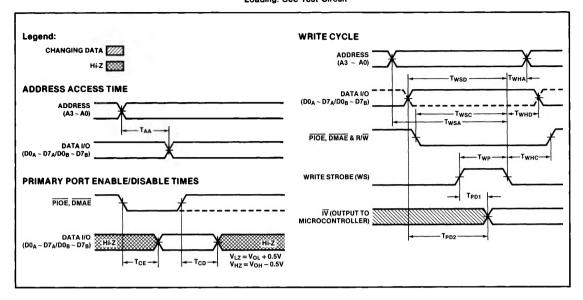

#### AC CHARACTERISTICS OF PRIMARY PORT $0^{\circ}C \le T_A \le 70^{\circ}C$ ; 4.75V $\le V_{CC} \le 5.25V$ Loading: See Test Circuit

|                               |                                 | IETER FROM                                                         |                                                                    |                |     |     |                |

|-------------------------------|---------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|----------------|-----|-----|----------------|

|                               | PARAMETER                       | FROM                                                               | то                                                                 | Min            | Тур | Max | UNIT           |

| T <sub>AA</sub>               | Address Access Time             | A3-A0                                                              | D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> |                |     | 45  | ns             |

| T <sub>CE</sub>               | Primary port enable time        | ↓PIOE<br>↓DMAE                                                     | D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> |                |     | 30  | ns             |

| T <sub>CD</sub>               | Primary port disable time       | †PIOE<br>†DMAE                                                     | D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> |                |     | 35  | ns             |

| TWSA                          | Address setup time              | A3-A0                                                              | łws                                                                | 40             |     |     | ns             |

| T <sub>WHA</sub>              | Address hold time               | tws                                                                | A3-A0                                                              | 0              |     |     | ns             |

| T <sub>WSD</sub>              | Primary port data setup time    | D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> | łws                                                                | 30             |     |     | ns             |

| TWHD                          | Primary port data hold time     | łws                                                                | D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> | 0              |     |     | ns             |

| T <sub>wsc</sub>              | Write mode control setup time   | PIOE<br>DMAE<br>R/W                                                | ∔ws<br>↓ws<br>↓ws                                                  | 30<br>40<br>30 |     |     | ns<br>ns<br>ns |

| т <sub>wнc</sub>              | Write mode control hold time    | ŧws                                                                | PIOE<br>DMAE<br>R/W                                                | 10<br>10<br>10 |     |     | ns<br>ns<br>ns |

| T <sub>WP</sub>               | Write strobe pulse width        |                                                                    |                                                                    | 25             |     |     | ns             |

| T <sub>PD1</sub> <sup>1</sup> | Primary port data delay         | D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> | IVO-IV7                                                            |                |     | 75  | ns             |

| T <sub>PD2</sub> <sup>2</sup> | Primary port data delay from WS | tws                                                                | 100-107                                                            |                | 1   | 75  | ns             |

Notes<sup>.</sup>

1 Measurement with Write Strobe set High and the control signals of the secondary port set for output data from the same register

2 Measurement with primary port data stable and control signals of secondary port

set for output data from the same register.

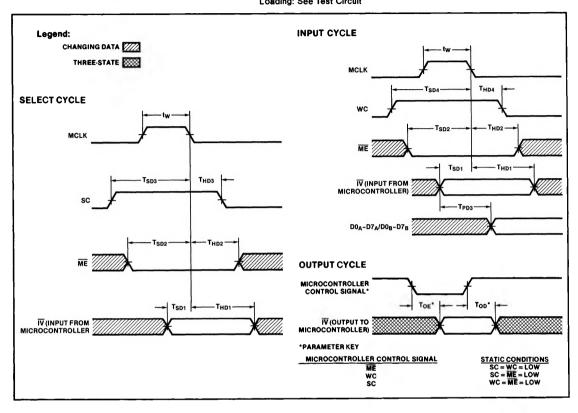

#### AC CHARACTERISTICS OF SECONDARY PORT $0^{\circ}C \le T_A \le 70^{\circ}C$ , 4.75V $\le V_{CC} \le 5.25V$ Loading: See Test Circult

|                         | PARAMETER            | FROM          | <b>T</b> 0                                                         |     |         |    |      |  |

|-------------------------|----------------------|---------------|--------------------------------------------------------------------|-----|---------|----|------|--|

|                         | PARAMETER            | FROM          | то                                                                 | Min | Typ Max |    | UNIT |  |

| tw                      | MCLK pulse width     | 1. 5. 5       |                                                                    | 30  |         |    | ns   |  |

| T <sub>SD1</sub>        | Data setup time      | 100-107       | ↓MCLK                                                              | 35  |         |    | ns   |  |

| T <sub>SD2</sub>        | ME setup time        | ME            | <b>↓</b> MCLK                                                      | 30  |         |    | ns   |  |

| T <sub>SD3</sub>        | SC setup time        | SC            | +MCLK                                                              | 30  |         |    | ns   |  |

| T <sub>SD4</sub>        | WC setup time        | WC            | <b>†</b> MCLK                                                      | 30  |         |    | ns   |  |

| T <sub>HD1</sub>        | Data hold time       | +MCLK         | 100-107                                                            | 0   |         |    | ns   |  |

| T <sub>HD2</sub>        | ME hold time         | <b>↓</b> MCLK | ME                                                                 | 0   |         |    | ns   |  |

| T <sub>HD3</sub>        | SC hold time         | +MCLK         | SC                                                                 | 0   |         |    | ns   |  |

| T <sub>HD4</sub>        | WC hold time         | <b>↓</b> MCLK | wc                                                                 | 0   |         |    | ns   |  |

| T <sub>PD3</sub> (Note) | IV propagation delay | īV            | D0 <sub>A</sub> -D7 <sub>A</sub> /D0 <sub>B</sub> -D7 <sub>B</sub> |     |         | 45 | ns   |  |

| T <sub>OE</sub>         | Output enable        | ME, SC, or WC | ĪVO-ĪV7                                                            |     |         | 30 | ns   |  |

| Top                     | Output disable       | ME, SC, or WC | ĪVO-ĪV7                                                            |     |         | 20 | ns   |  |

Note:

Measured with MCLK= High and control signals of the primary port set for output data from the same register

8X320