8X08-F.XA

#### DESCRIPTION

This LSI integrated circuit performs the digital control functions required for generating AM/FM radio frequency local oscillator signals using digital phase locked loop techniques. By the use of low power Schottky and ECL technologies on the same substrate it is possible to operate at 80MHz input frequencies with an average system power of 1.6mW per gate typical.

#### **FEATURES**

- 80MHz Input frequency

- ECL prescaler

- LS process

- Single 5V supply

- Power dissipation—600mW (max)

- External components—

- 1 crystal

- 2 capacitors

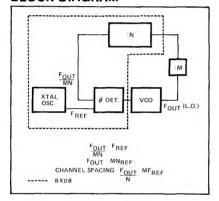

## PHASE LOCKED LOOP BLOCK DIAGRAM

# PHASE LOCKED LOOP PRINCIPLES

Digital phase locked loops are comprised of 4 basic building blocks: A fixed reference frequency generator (crystal oscillator and divider), a phase comparator, a voltage controlled oscillator (VCO) and a programable counter (+N).

In cases where very high frequencies must be generated, a fixed prescaler (÷M) is employed to divide the local oscillator frequency down to a frequency compatible with the programmable counter. Fout from the VCO is divided down by the prescaler and programmable counters and compared to the reference frequency by the phase detector. If Fout is not equal to Fref in phase and

frequency, the phase detector generates a signal which causes the VCO frequency to

increase or decrease until F ref = Fout. When MN

this occurs, the local oscillator is essentially as stable as the crystal reference oscillator.

The local oscillator frequency (Fout) is changed by programming a different number into the programmable counter. The distance between discrete frequencies or the channel spacing is determined by the reference frequency.

For the AM/FM circuit, up to 200 channels are possible with selectable channel spacing of 10kHz for AM operation and 2000 channels at 100kHz for FM operation.

# AM/FM Frequency Synthesizer Circuit Description

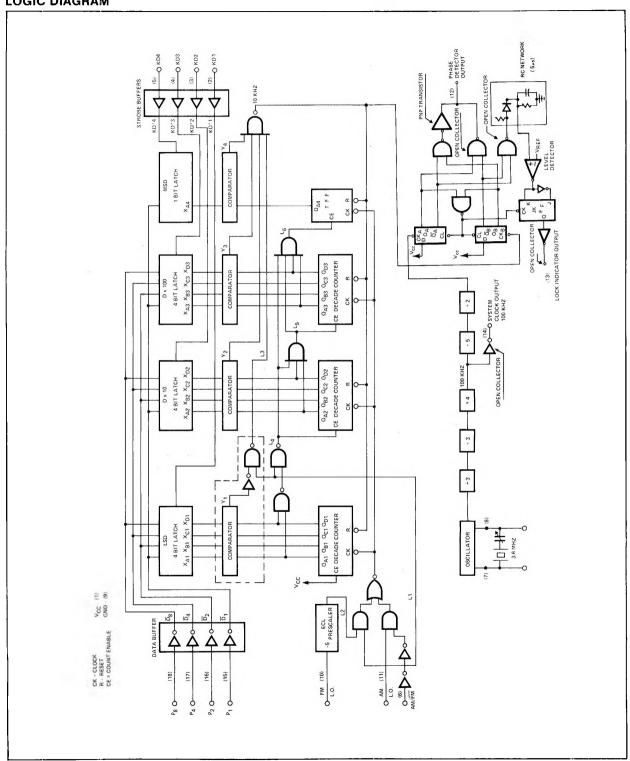

The frequency synthesizer circuit logic diagram is shown below. Following is a description of each of the major blocks.

## **Programmable Counter**

The programmable counter consists of 3 stages of decade counter plus a divide by 1 or 0 counter to divide by numbers up to 1999. BCD programming data is presented to the dividers in parallel form, one digit at a time. Parallel data is strobed into internal latches via strobe signals; one strobe for each digit. A ÷ 5 80MHz ECL prescaler precedes the programmable counter for FM operation. This prescaler plus an external 160MHz ÷ 2 flip-flop provide a ÷ 10 160MHz prescaler (+M) function to scale the programmable counter input frequency down to 16MHz maximum. A logic control circuit bypasses the +M prescaler and the first decade counter for AM operation. By this technique, the channel spacing is programmable to 10kHz for AM operation and 100kHz for FM operation.

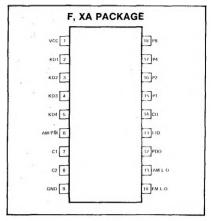

### **PIN CONFIGURATION**

#### VCO

An externally provided integrator and voltage controlled oscillator must be provided to perform the complete frequency synthesizer function. The integrator converts the pulses that come from the phase detector into a dc signal that controls the output frequency of the voltage controlled oscillator. It is in the integrator part of the circuit that the critical loop constants are determined. The voltage controlled oscillator is normally a LC tuned oscillator with varactor diode tuning that is controlled by the dc signals from the integrator. In this case, two are required, one for the AM band and one for the FM band. The FM oscillator output must be +5V ECL compatible while the AM oscillator must be TTL compatible.

### RECOMMENDED OPERATING CONDITIONS

|                  | PARAMETER                                                  | Min  | Тур | Max  | UNIT |  |

|------------------|------------------------------------------------------------|------|-----|------|------|--|

| Τ <sub>Δ</sub>   | Operating free air temperature                             | -40  |     | +85  | °C   |  |

| V <sub>C</sub> C | Supply voltage                                             | 4.75 | 5.0 | 5.25 | V    |  |

|                  | Max input voltage data, strobe                             |      |     | 16   | v    |  |

|                  | Max AM local oscillator input operating frequency (Pin 11) | Į    | 20  |      | MHz  |  |

|                  | Max FM local oscillator input operating frequency (Pin 10) |      | 100 | 80   | MHz  |  |

|                  | Maximum reference frequency oscillator operating frequency |      | 6   |      | MHz  |  |

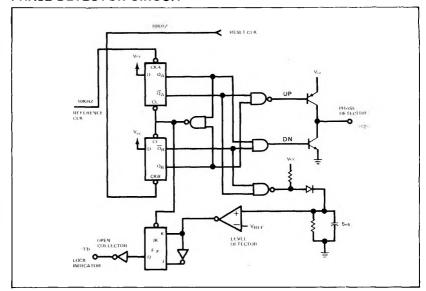

#### **Phase Detector Circuit**

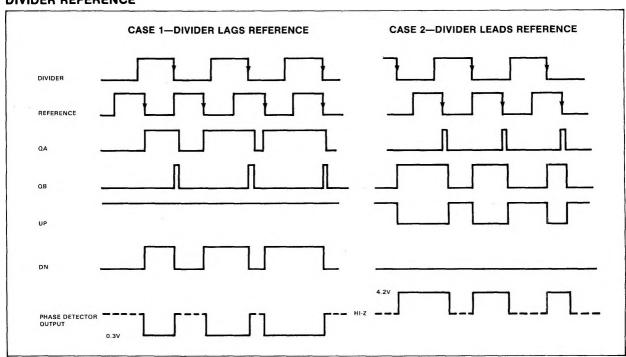

The phase detector is a digital edge-detecting device that provides an output three-state signal that is in a high impedance state when the 2 input signals are equal in phase and/or frequency. The output of the phase detector is a series of pulses that swing from the high impedance state to .3V typical or from the high impedance state to 4.2V typical. If the positive edge of the divider input leads the reference, the pulses will go to 4.2V. If it lags they will go to .3V.

The width of the output pulses is a function of the time between the positive edges (phase) of the 2 signals. An example of the operation of the device is shown where the reference signal is twice the frequency of the divider signal and has a phase lead of 270°. The output pulses are converted to a dc signal by integrating amplifiers causing the output frequency of the voltage controlled oscillator to increase or decrease (increase in this case) until the divider output and the reference output are equal in phase and frequency.

#### PHASE DETECTOR CIRCUIT

#### **DIVIDER REFERENCE**

# LOGIC DIAGRAM

# DC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

|                 |                                        |                                               | LIMI      |         |      | LIMITO  |

|-----------------|----------------------------------------|-----------------------------------------------|-----------|---------|------|---------|

| PARAMETER       |                                        | TEST CONDITIONS                               | Min       | Тур Мах |      | UNITS   |

| V <sub>IH</sub> | High level input voltage               |                                               |           |         |      |         |

|                 | P, KD, AM/FM inputs                    | 1                                             | 5.25      |         |      | V       |

|                 | AM L.O. input                          |                                               | 2         |         |      | V       |

|                 | FM L.O. input                          |                                               | 4.1       |         | 5.25 | V       |

| √ıL             | Low level input voltage                |                                               |           |         |      |         |

| ,_              | P, KD, AM/FM inputs                    |                                               |           |         | 3.75 | ٧       |

|                 | AM L.O. input                          |                                               |           |         | 8.0  | V       |

|                 | FM L.O. input                          |                                               |           |         | 3.3  | V       |

| IH              | High level input current               |                                               |           |         |      |         |

|                 | P, KD, AM/FM inputs                    | VCC = max, V <sub>I</sub> = 16V               |           |         | 200  | $\mu$ A |

|                 |                                        | V <sub>CC</sub> = max, V <sub>I</sub> = 5.25V |           |         | 40   | $\mu A$ |

|                 | AM L.O. input                          |                                               |           |         |      |         |

|                 | (with 5k Ω pullup to V <sub>CC</sub> ) | VCC = max, V <sub>I</sub> = 5.25V             |           |         | 200  | $\mu$ A |

|                 | FM L.O. input                          | VCC = max, V <sub>I</sub> = 5.25V             |           |         | 400  | $\mu$ A |

| п               | Low level inputs current               |                                               |           |         |      |         |

| 12              | P, KD, AM/FM inputs                    | V <sub>CC</sub> = max, V <sub>I</sub> = 3.75V |           | 1       | -40  | $\mu$ A |

|                 | AM L.O. input                          |                                               |           |         |      |         |

|                 | (with 5k Ω pullup to VCC)              | $V_{CC} = max, V_1 = 0.4V$                    | 7         |         | -1.6 | mΑ      |

|                 | FM L.O. input                          | V <sub>CC</sub> = max, V <sub>I</sub> = 0.4V  |           |         | -40  | $\mu$ A |

| √OL             | Low level output voltage               |                                               |           |         |      |         |

|                 | System clock output                    | VCC = min, IOL = 16mA                         |           |         | 8.0  | V       |

|                 | Lock indicator output                  | V <sub>CC</sub> = min, l <sub>OL</sub> = 16mA | -         |         | 0.8  | V       |

|                 | Phase detector output                  | V <sub>CC</sub> = min, I <sub>OL</sub> = 40μA |           |         | 0.5  | V       |

| √он             | High level output voltage              |                                               |           |         |      |         |

|                 | Phase detector output                  | $V_{CC} = min, I_{OH} = -40\mu A$             | VCC -0.5V |         |      |         |

| loL             | High level output current              |                                               |           |         |      |         |

|                 | System clock output                    | V <sub>CC</sub> = min, V <sub>OH</sub> = 16V  |           |         | 250  | $\mu$ A |

|                 | Lock indicator output                  | VCC = min, VOH = 16V                          |           |         | 250  | $\mu$ A |

| ICC             | Supply current                         | V <sub>CC</sub> = max                         |           |         | 150  | mA      |

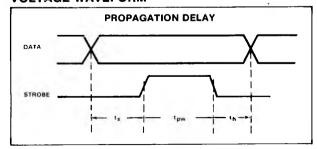

## **AC ELECTRICAL CHARACTERISTICS**

| PARAMETER                                                                                                        | то               | FROM         | LIMITS                      |             |  | UNIT     |

|------------------------------------------------------------------------------------------------------------------|------------------|--------------|-----------------------------|-------------|--|----------|

| PARAMETER                                                                                                        |                  |              | Min                         | Min Typ Max |  | 1 UNII   |

| Strobe pulse width Setup and hold time  t <sub>S</sub> Logic high Logic low  t <sub>h</sub> Logic high Logic low | Strobe<br>Strobe | Data<br>Data | 200<br>150<br>50<br>40<br>0 | 100         |  | ns<br>ns |

# **VOLTAGE WAVEFORM**

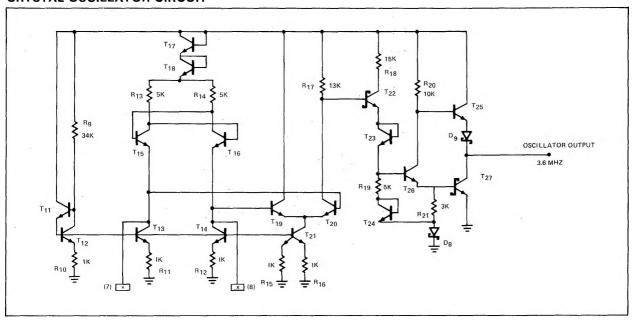

## **Crystal Oscillator Circuit**

In this circuit, the cross-coupled transistor pair form a bistable circuit. The crystal provides positive feedback between the emitters of  $T_{15}$  and  $T_{16}$  which causes the circuit to oscillate at the crystal frequency.

# Recommended Crystal Characteristics

| Туре              | Fundamental Mode<br>Series Resonant |  |  |  |  |

|-------------------|-------------------------------------|--|--|--|--|

| Series resistance | < 100 Ω                             |  |  |  |  |

### **CRYSTAL OSCILLATOR CIRCUIT**