REFER TO PAGE 18 FOR B, E AND R PACKAGE PIN CONFIGURATIONS.

# DIGITAL 8000 SERIES TTL/MSI

## **DESCRIPTION**

The 8T04 consists of the necessary logic to decode a 4-bit BCD code to seven segment (0 through 9) readout, as well as some selected signs and letters.

Incorporated in this device is a blanking circuit which turns all segments off when activated. The blanking circuit allows suppression of all numerically insignificant zeros, thereby presenting an easily read display.

Also included is the necessary circuitry to implement suppression of leading and/or trailing zeros. A Lamp Test control is provided to turn all segments on. The Lamp Test allows the viewer to check the validity of the display lamps.

High performance bare collector output transistors are used in the 8T04 for directly driving incandescent lamps or common anode LED displays.

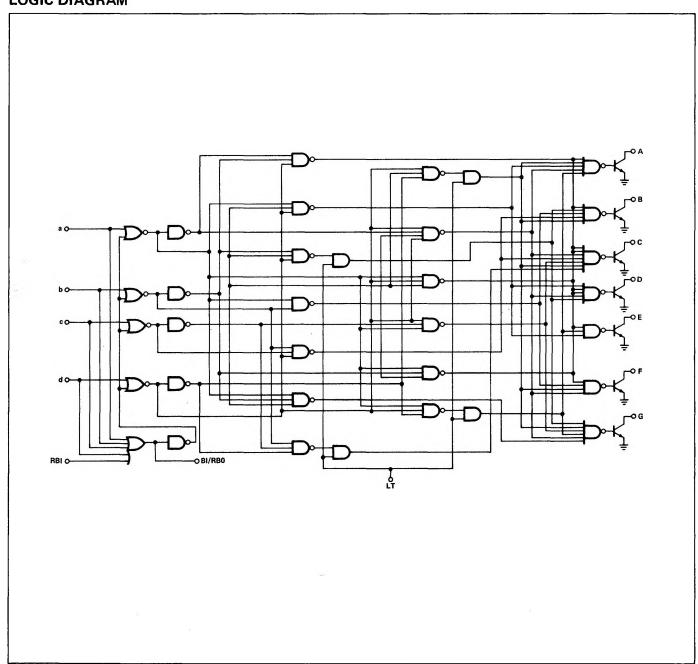

### **LOGIC DIAGRAM**

## **ELECTRICAL CHARACTERISTICS** (Over Recommended Operating Temperature And Voltage)

|                                                            | LIMITS |      |                  |                       | TEST CONDITIONS |              |               |                  |         |              |  |

|------------------------------------------------------------|--------|------|------------------|-----------------------|-----------------|--------------|---------------|------------------|---------|--------------|--|

| CHARACTERISTICS                                            | MIN.   | TYP, | MAX.             | UNITS                 | LT              | RB1          | RB0<br>B1     | DRIVEN<br>INPUTS | OUTPUTS | NOTES        |  |

| "1" Output Voltage                                         | 3.1    |      |                  | <b>V</b> <sub>i</sub> |                 |              | -160µA        |                  |         | 7, 9         |  |

| "0" Output Voltage<br>RBO<br>A-G                           |        |      | 0.4<br>0.50      | V                     | 0.4V            | 0.8V<br>0,4V | 4.8mA<br>0.4V | 0.8∨             | 40mA    | 8, 9<br>8, 9 |  |

| '1'' Output Leakage<br>Current (A-G)<br>'1'' Input Current |        |      | 100              | μΑ                    |                 | 0.8V         |               |                  | 6.0V    | 9, 10        |  |

| RBI<br>LT                                                  |        |      | 40<br>160        | μΑ<br>μΑ              | 4.5V            | 4.5V         |               |                  |         | 1            |  |

| All Other Inputs 'O" Input Current                         |        |      | 80               | μА                    |                 | 4.5V         | 4.5V          | 4.5V             |         |              |  |

| RBI<br>BI                                                  | 1<br>1 |      | -1.2<br>-2.2     | mA<br>mA              | 0.414           | 0.4V         | 0.4V          |                  |         |              |  |

| LT<br>All Other Inputs                                     | 1<br>1 |      | -10<br>-1.6      | mA<br>mA              | 0.4V<br>0.4V    |              |               | 0.4V             |         |              |  |

| Input Latch Voltage Power/Current Consumption:             | 5.5    |      | -1.0             | '''v                  | 0.44            |              | 10mA          | -0.4 <b>V</b>    |         | 11           |  |

| "S" Temperature Range "N" Temperature Range                |        |      | 394/75<br>446/85 | mW/mA<br>mW/mA        |                 |              |               |                  |         | 13<br>13     |  |

#### NOTES:

- All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- All measurements are taken with ground pin tied to zero volts.

- Positive current is defined as into the terminal referenced.

- 4. Positive NAND Logic Definition: "UP" Level = "1", "DOWN" = "0".

- Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased.

- 6. Measurements apply to each gate element independently.

- 7. Output source current is supplied through a resistor to ground.

- Output sink current is supplied through a resistor to V<sub>CC</sub>.

- See truth table: "1" Threshold = 2.0V for a,b,c,d.

"0" Threshold = 0.8V for a,b,c,d.

- 10. Connect an external 1k  $\pm 1\%$  resistor to the output for this test.

- This test guarantees operation free of input latch-up over the specified operating supply voltage range.

- Manufacturer reserves the right to make design and process changes and improvements, V<sub>CC</sub> = 5.25V.

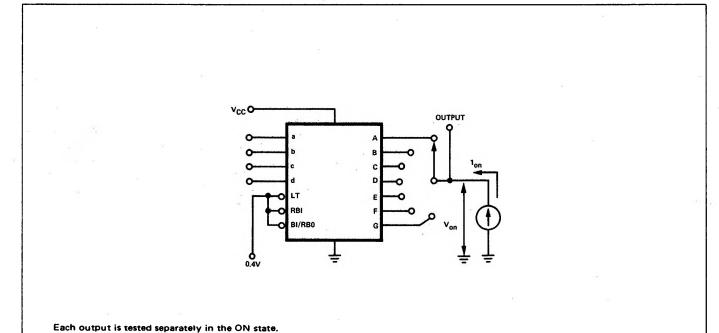

# TEST FIGURE FOR "0" OUTPUT VOLTAGE

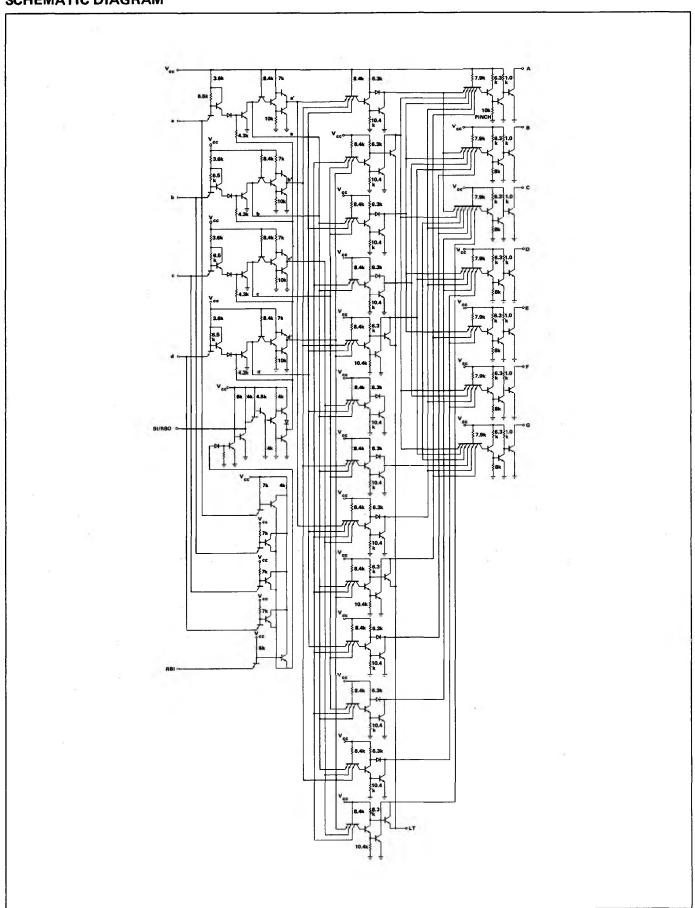

# SCHEMATIC DIAGRAM

# **TRUTH TABLE**

|                          | INPUTS |   |        |              | BI/RBO | OUTPUTS           |   |   |   |                      |   |   |   |          |  |

|--------------------------|--------|---|--------|--------------|--------|-------------------|---|---|---|----------------------|---|---|---|----------|--|

| INPUT CODE LAMP TEST RBI |        |   | Ві/КВО | OUTPUT STATE |        |                   |   |   |   | DISPLAY<br>CHARACTER |   |   |   |          |  |

| d                        | С      | b | а      | LT           |        | NOTE              | Α | В | С | D                    | E | F | G |          |  |

| ×                        | Х      | Х | х      | 0            | ×      | ×                 | 0 | 0 | 0 | 0                    | 0 | 0 | 0 | 8        |  |

| X                        | Χ      | X | X      | 1            | ×      | 0 0               | 1 | 1 | 1 | 1                    | 1 | 1 | 1 | BLK      |  |

| 0                        | 0      | 0 | 0      | 1            | 0      | (Note 1 & 2)<br>0 | 1 | 1 | 1 | 1                    | 1 | 1 | 1 | BLK      |  |

| 0                        | 0      | 0 | 0      | 1            | 1      | (Note 2)<br>1     | 0 | 0 | 0 | 0                    | 0 | 0 | 1 | 8        |  |

| 0                        | 0      | 0 | 1      | 1            | ×      | 1                 | 1 | 0 | 0 | 1                    | 1 | 1 | 1 |          |  |

| 0                        | 0      | 1 | 0      | 1            | ×      | 1                 | 0 | 0 | 1 | 0                    | 0 | 1 | 0 | 2        |  |

| 0                        | 0      | 1 | 1      | 1            | ×      | 1                 | 0 | 0 | 0 | 0                    | 1 | 1 | 0 | 3        |  |

| 0                        | 1      | 0 | 0      | 1            | ×      | 1                 | 1 | 0 | 0 | 1                    | 1 | 0 | 0 | Ÿ        |  |

| 0                        | 1      | 0 | 1      | 1            | X      | 1                 | 0 | 1 | 0 | 0                    | 1 | 0 | 0 | 5        |  |

| 0                        | 1      | 1 | 0      | 1            | x      | 1                 | 1 | 1 | 0 | 0                    | 0 | 0 | 0 | Ь        |  |

| 0                        | 1      | 1 | 1      | 1            | ×      | 1                 | 0 | 0 | 0 | 1                    | 1 | 1 | 1 | , ר<br>ר |  |

| 1                        | 0      | 0 | 0      | 1            | x      | 1                 | 0 | 0 | 0 | 0                    | 0 | 0 | 0 | 8        |  |

| 1                        | 0      | 0 | 1      | 1            | ×      | 1                 | 0 | 0 | 0 | 1                    | 1 | 0 | 0 | q        |  |

| 1                        | 0      | 1 | 0      | 1            | ×      | 1                 | 1 | 1 | 1 | 1                    | 1 | 1 | 0 | CD -     |  |

| 1                        | 0      | 1 | 1      | 1            | ×      | 1                 | 1 | 1 | 1 | 1                    | 1 | 1 | 1 | BLK      |  |

| 1                        | 1      | 0 | 0      | 1            | ×      | 1                 | 0 | 0 | 0 | 1                    | 0 | 0 | 0 | 8        |  |

| 1                        | 1      | 0 | 1      | 1            | x      | 1                 | 1 | 1 | 0 | 1                    | 1 | 1 | 1 |          |  |

| 1                        | 1      | 1 | 0      | 1            | ×      | 1                 | 1 | 1 | 1 | 0                    | 0 | 0 | 1 | L        |  |

| 1                        | 1      | 1 | 1      | 1            | ×      | 1                 | 1 | 1 | 1 | 1                    | 1 | 1 | 1 | BLK      |  |

<sup>\*</sup>COMMA

X = Don't care, either "1" or "0".

BI/RBO is an internally wired OR output.

# NOTE:

- 1. BI/RBO used as input.

- 2. BI/RBO should not be forced high when a,b,c,d, RBI terminals are low, or damage may occur to the unit.