82S09-I.N

### **DESCRIPTION**

The organization of this device allows byte manipulation of data, including parity. Where parity is not monitored, the ninth bit can be used as a flag or status indicator for each word stored. With a typical access time of 30ns, it is ideal for scratch-pad, pushdown stacks, buffer memories, and other internal memory applications in which cost and performance requirements dictate a wide data path in favor of word depth.

The 82S09 features open collector outputs, chip enable input, and a very low current pnp input structure to enhance memory expansion.

During Write operation, the logic state of the device output follows the complement of the data input being written. This feature allows faster execution of Write-Read cycles, enhancing the performance of systems utilizing indirect addressing modes, and/or requiring immediate verification following a Write cycle.

The 82S09 is available in the commercial and military temperature ranges. For the commercial temperature ranges. (0°C to +75°C) specify N82S09, and for the military temperature range (-55°C to +125°C) specify S82S09.

### **FEATURES**

- Address access time: N82S09: 45ns max S82S09: 80ns max

- Write cycle time: N82S09: 45ns max S82S09: 75ns max

- Power dissipation: 1.3mW/bit typ

- Input loading:

N82S09: -100μA max S82S09: -150μA max

- Output follows complement of data input during Write

- On-chip address decoding

- Schottky clamped

- Fully TTL compatible

### **APPLICATIONS**

- Buffer memory

- Control register

- FIFO memory

- Push down stackScratch pad

### PIN CONFIGURATION

### **TRUTH TABLE**

| MODE      | CE  | WE | I <sub>N</sub> | ON                        |

|-----------|-----|----|----------------|---------------------------|

| Read      | 0   | 1  | х              | Complement of data stored |

| Write "0" | o   | 0  | 0              | 1                         |

| Write "1" | 0   | 0  | 1              | 0                         |

| Disabled  | - 1 | ×  | х              | 1                         |

X = Don't care

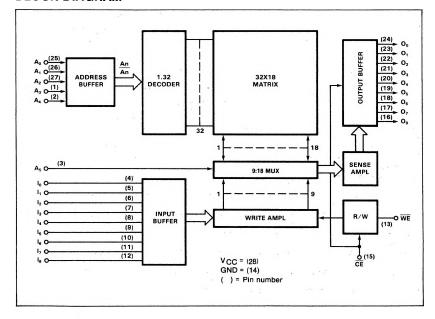

### **BLOCK DIAGRAM**

82S09-I,N

### **ABSOLUTE MAXIMUM RATINGS**

|           | PARAMETER                                                        | RATING                                 | UNIT      |

|-----------|------------------------------------------------------------------|----------------------------------------|-----------|

| Vcc       | Supply voltage                                                   | +7                                     | Vdc       |

| Vin       | Input voltage                                                    | +5.5                                   | Vdc       |

| Voh<br>Ta | Output voltage<br>High (82S10)<br>Temperature range<br>Operating | +5.5                                   | Vdc<br>°C |

| Tstg      | N82S09<br>S82S09<br>Storage                                      | 0 to +75<br>-55 to +125<br>-65 to +150 |           |

## $\begin{array}{ll} \textbf{DC ELECTRICAL CHARACTERISTICS} \\ \textbf{N82S09: 0°C} \leq \textbf{T}_{A} \leq +75^{\circ}\textbf{C}, \ 4.75\textbf{V} \leq \textbf{V}_{CC} \leq 5.25\textbf{V} \\ \textbf{S82S09: } -55^{\circ}\textbf{C} \leq \textbf{T}_{A} \leq +125^{\circ}\textbf{C}, \ 4.5\textbf{V} \leq \textbf{V}_{CC} \leq 5.5\textbf{V} \\ \end{array}$

| PARAMETER <sup>1</sup>                                |                                                    |                                                                                                  | N82S09 |                  |             | S82S09 |                  |             |      |

|-------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|------------------|-------------|--------|------------------|-------------|------|

|                                                       |                                                    | TEST CONDITONS                                                                                   | Min    | Typ <sup>2</sup> | Max         | Min    | Typ <sup>2</sup> | Max         | UNIT |

| V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>IC</sub> | Input voltage<br>Low<br>High<br>Clamp <sup>3</sup> | V <sub>CC</sub> = Min<br>V <sub>CC</sub> = Max<br>V <sub>CC</sub> = Min, I <sub>IN</sub> = -12mA | 2.0    | -1.0             | .85<br>-1.5 | 2.2    | -1.0             | .80<br>-1.5 | . V  |

| Vol                                                   | Output voltage<br>Low <sup>4</sup>                 | V <sub>CC</sub> = Min, I <sub>OL</sub> = 6.4mA                                                   |        | 0.35             | 0.5         | -      | 0.35             | 0.5         | ٧    |

| lıL<br>lın                                            | Input current<br>Low<br>High                       | V <sub>IN</sub> = 0.45V<br>V <sub>IN</sub> = 5.5V                                                |        | -10<br>1         | -100<br>25  |        | -10<br>1         | -150<br>40  | μА   |

| lolk                                                  | Output current<br>Leakage <sup>5</sup>             | V <sub>CC</sub> = Max, V <sub>OUT</sub> = 5.5V                                                   |        | 1                | 40          |        | 1                | 60          | μА   |

| Icc                                                   | V <sub>CC</sub> supply current <sup>6</sup>        | V <sub>CC</sub> = Max                                                                            |        | 150              | 190         |        | 150              | 200         | mA   |

| Cin<br>Cout                                           | Capacitance<br>Input<br>Output                     | V <sub>CC</sub> =5.0V<br>V <sub>IN</sub> = 2.0V<br>V <sub>OUT</sub> = 2.0V                       | -      | 5<br>8           |             |        | 5<br>8           |             | pF   |

82S09-I,N

AC ELECTRICAL CHARACTERISTICS  $R_1=600\Omega,\ R_2=900\Omega,\ C_L=30 pF,\ See$  ac test load N82S09:  $0^{\circ} \le T_A \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$ S82S09:  $-55^{\circ}$ C  $\leq T_{A} \leq +125^{\circ}$ C, 4.5V  $\leq V_{CC} \leq 5.5$ V

| PARAMETER                          |                                                |                  | FROM                        | N82S09  |                  |          | \$82\$09 |                  |          |          |

|------------------------------------|------------------------------------------------|------------------|-----------------------------|---------|------------------|----------|----------|------------------|----------|----------|

|                                    |                                                | ТО               |                             | Min     | Typ <sup>2</sup> | Max      | Min      | Typ <sup>2</sup> | Max      | UNIT     |

| TAA<br>TCE                         | Access time<br>Address<br>Chip enable          |                  |                             |         | 30<br>15         | 45<br>30 |          | 30<br>15         | 80<br>50 | ns       |

| T <sub>CD</sub><br>T <sub>WD</sub> | Disable time<br>Valid time                     | Output<br>Output | Chip enable<br>Write enable | -       | 15<br>25         | 30<br>50 |          | 15<br>25         | 50<br>80 | ns<br>ns |

| Twsa<br>Twha                       | Setup and hold time<br>Setup time<br>Hold time | Write enable     | Address                     | 5       | 0                |          | 10       | 0                |          | ns       |

| Twsd<br>Twhd                       | Setup time<br>Hold time                        | Write enable     | Data in                     | 35<br>5 | 25<br>0          |          | 50<br>5  | 25<br>0          |          |          |

| Twsc<br>Twhc                       | Setup time<br>Hold time                        | Write enable     | CE                          | 5       | 0                |          | 10       | 0                |          |          |

| Twp                                | Pulse width<br>Write enable                    |                  |                             | 35      | 25               |          | 50       | 25               |          | ns       |

### NOTES

- 1. All voltage values are with respect to network ground terminal.

- 2. All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

- 3. Test each input one at a time.

- 4. Measured with the logic low stored. Output sink current is supplied through a resistor to Vcc. 5. Measured with  $V_{IH}$  applied to  $\overline{CE}$ .

- $6. \quad \text{lcc} \ \text{is measured with the write enable and memory enable input grounded, all other inputs at 4.5V, and} \\$ the outputs open.

- 7. Minimum required to guarantee a Write into the slowest bit.

- 8. The operating ambient temperature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a 2-minute warm-up.

### **TEST LOAD CIRCUIT**

# **LOADING CONDITION** γν<sub>сс</sub> **ξ**1κ PULSE GENERATOR vcc PULSE GENERATOR DUT WE (CAPACITANCE INCLUDING SCOPE AND JIG) PULSE GENERATOR All resistors values are typical and in ohms

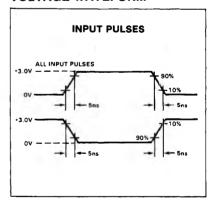

### **VOLTAGE WAVEFORM**

82S09-I,N

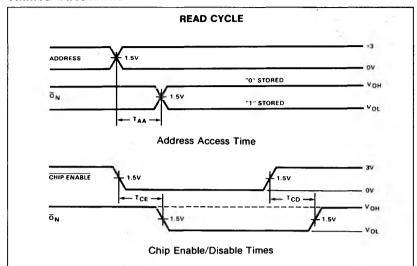

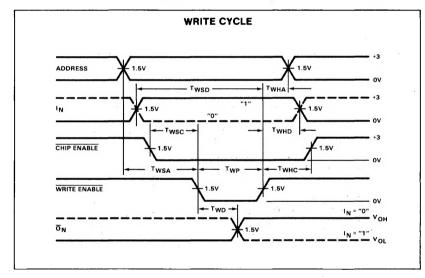

### **TIMING DIAGRAMS**

### **MEMORY TIMING DEFINITIONS**

Tce Delay between beginning of Chip Enable low (with Address valid) and when Data Output becomes valid.

Tcb Delay between when Chip Enable becomes high and Data Output is in off state.

Taa Delay between beginning of valid Address (with Chip Enable low) and when Data Output becomes

Twsc Required delay between beginning of valid Chip Enable and beginning of Write Enable pulse.

TWHD Required delay between end of Write Enable pulse and end of valid Input Data.

Twp Width of Write Enable pulse.

Twsa Required delay between beginning of valid Address and begin-

Twsp

ning of Write Enable pulse.

Required delay between beginning of valid Data Input and end of Write Enable pulse.

Two Delay between beginning of Write Enable pulse and when Data Output reflects complement of Data

TWHC Required delay between end of Write Enable pulse and end of Chip Enable.

Twha Required delay between end of Write Enable pulse and end of valid Address.

55