8263 8264

REFER TO PAGE 15 FOR P, N AND Y PACKAGE PIN CONFIGURATIONS.

# DIGITAL 8000 SERIES TTL/MSI

### **DESCRIPTION**

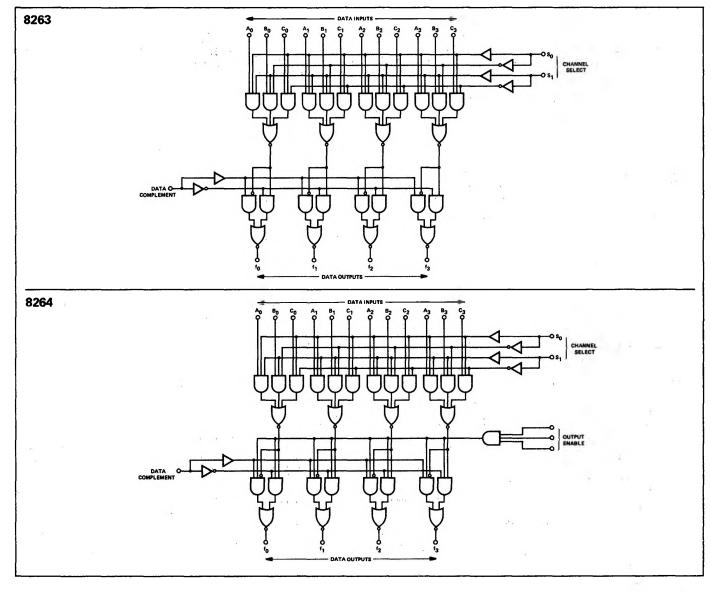

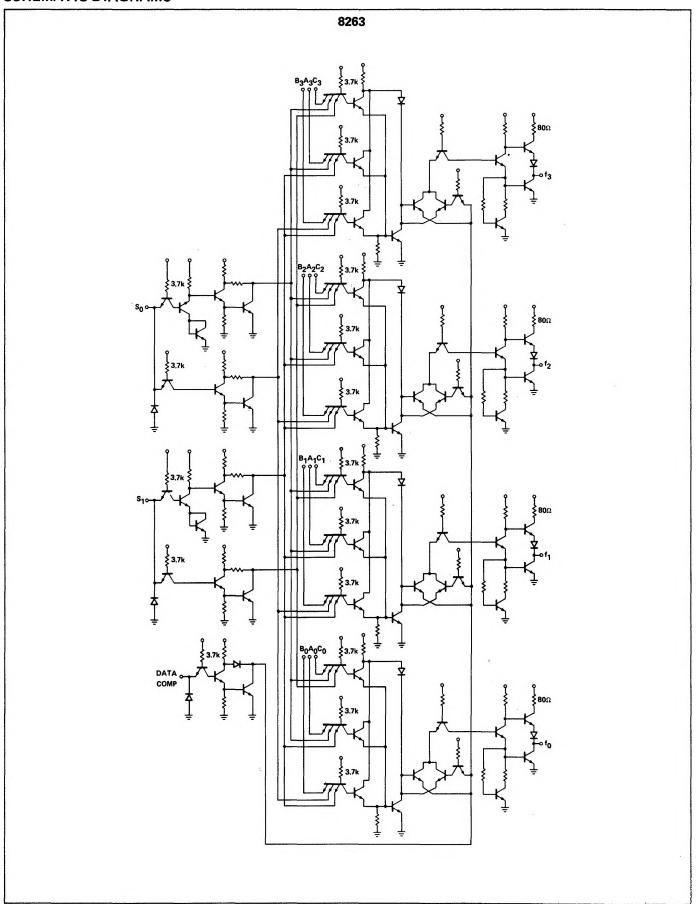

The 8263/8264 3-Input, 4-Bit Multiplexer is a gating array whose function is analogous to that of a 4-pole, 3-position switch. Four bits of digital data are selected from one of three inputs. A 2-bit channel-selection code determines which input is to be active.

The Data Complement input controls the conditional complement circuit at the Multiplexer output to effect either inverting or non-inverting data flow.

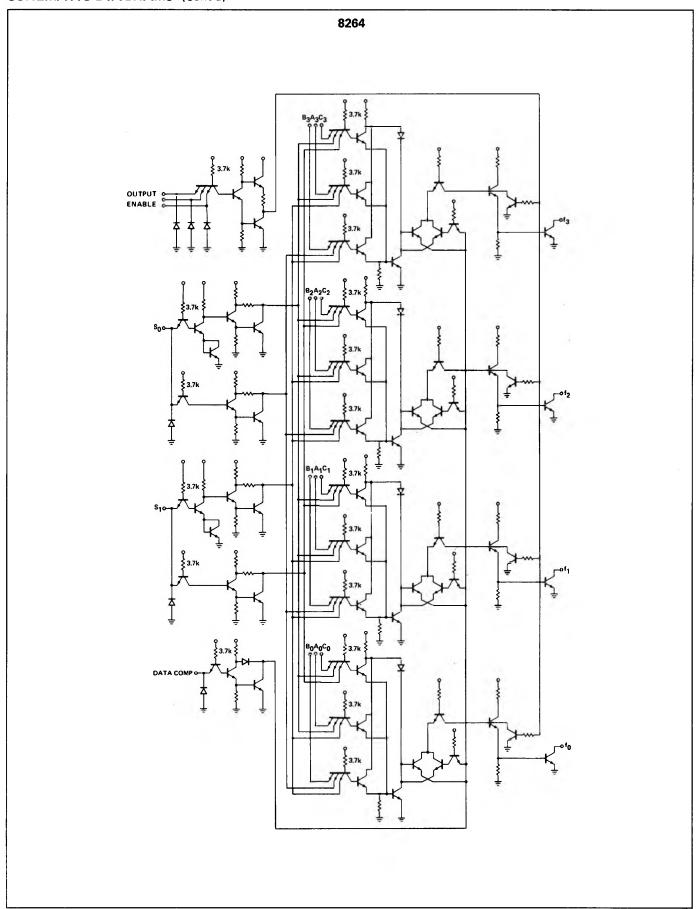

The 8263 employs active output structures to effect minimum delays: the 8264 utilizes bare collector outputs for expansion of input terms.

The 8264 may be expanded by connecting its outputs to the outputs of another 8264. Provision is made for use of a 3-bit code to determine which Multiplexer is selected; thus, eight Multiplexers may be commoned to effect a 4-pole, 24-position switch.

#### TRUTH TABLE

| Data<br>Input<br>A <sub>n</sub> B <sub>n</sub> C <sub>n</sub> | Channel<br>Select<br>S <sub>0</sub> S <sub>1</sub> | Data<br>Complement | Output Enable<br>(8264) | Data<br>Outputs                  |  |  |  |

|---------------------------------------------------------------|----------------------------------------------------|--------------------|-------------------------|----------------------------------|--|--|--|

| A <sub>n</sub> x x                                            | 1 1                                                | 0                  | 1                       | An                               |  |  |  |

| x B <sub>n</sub> x                                            | 0 1                                                | 0                  | 1                       | B <sub>n</sub>                   |  |  |  |

| x x Cn                                                        | 1 0                                                | 0                  | 1                       | Cn                               |  |  |  |

| xxx                                                           | 0 0                                                | 0                  | 1                       | 0                                |  |  |  |

| A <sub>n</sub> x x                                            | 1 1                                                | 1                  | 1                       | Αn                               |  |  |  |

| x B <sub>n</sub> x                                            | 0 1                                                | 1                  | 1                       | Bn                               |  |  |  |

| x x Cn                                                        | 1 0                                                | 1                  | 1                       | B <sub>n</sub><br>C <sub>n</sub> |  |  |  |

| xxx                                                           | 0 0                                                | 1                  | 1                       | 1                                |  |  |  |

| $\mathbf{x} \mathbf{x} \mathbf{x}$                            | x x                                                | x                  | 0                       | 1                                |  |  |  |

X = Either State

#### LOGIC DIAGRAMS

### **ELECTRICAL CHARACTERISTICS** (Over Recommended Operating Temperature And Voltage)

| λ -                                                   |      | LIM  | IITS |       | TEST CONDITIONS |      |                |                |                |              |                  |         |       |  |  |  |  |

|-------------------------------------------------------|------|------|------|-------|-----------------|------|----------------|----------------|----------------|--------------|------------------|---------|-------|--|--|--|--|

| CHARACTERISTICS                                       | MIN. | TYP. | MAX. | UNITS | An              | Bn   | c <sub>n</sub> | s <sub>o</sub> | s <sub>1</sub> | DATA<br>COMP | OUTPUT<br>ENABLE | OUTPUTS | NOTES |  |  |  |  |

| "1" Output Voltage (8263) "1" Output Leakage Current  | 2.6  | 3.5  |      | ٧     | 2.0V            | 2.0V | 2.0V           | 2.0V           | 2.0V           | 0.8∨         |                  | 800μΑ   | 8     |  |  |  |  |

| (8264)                                                |      |      | 200  | μΑ    | 2.0\            | 2.0V | 2.0V           | 2.0V           | 2.0∨           | 0.8V         | 2.0V             |         | 11    |  |  |  |  |

| "0" Output Voltage (8263)                             |      |      | 0.4  | v     | 0.8V            | 0.8∨ | 0.8V           | 2.0V           | 2.0∨           | 0.8V         |                  | 9.6mA   | 9     |  |  |  |  |

| "0" Output Voltage (8264) "0" Input Current           |      |      | 0.4  |       | 0.8V            |      |                |                |                |              |                  | 16.0mA  | 11    |  |  |  |  |

| An                                                    | -0.1 |      | -1.6 | mA    | 0.4V            |      |                | }              |                |              |                  | l       |       |  |  |  |  |

| B <sub>n</sub>                                        | -0.1 |      | -1.6 | mA    |                 | 0.4V |                | 0.4∨           |                |              |                  |         |       |  |  |  |  |

| C <sub>n</sub>                                        | -0.1 |      | -1.6 | mA    |                 |      | 0.4∨           |                | 0.4∨           |              |                  | 1       |       |  |  |  |  |

| OE, DC                                                | -0.1 |      | -1.6 | mA    |                 |      |                |                |                | 0.4V         | 0.4V             |         | 6     |  |  |  |  |

| \$ <sub>0</sub> , S <sub>1</sub><br>"1" Input Current | -0.1 |      | -3.2 | mA    |                 |      |                | 0.4∨           | 0.4V           |              |                  |         |       |  |  |  |  |

| An                                                    |      |      | 40   | μА    | 4.5V            |      | 1              | ov             | 0V             |              |                  |         |       |  |  |  |  |

| B <sub>n</sub>                                        |      |      | 40   | μА    |                 | 4.5V |                |                | ov.            |              |                  |         | •     |  |  |  |  |

| c <sub>n</sub>                                        |      |      | 40   | μΑ    |                 |      | 4.5V           | ov             |                | l            |                  | 1       |       |  |  |  |  |

| OE, DC                                                |      |      | 40   | μΑ    |                 |      |                | 1              | 1              | 4.5V         | 4.5V             |         |       |  |  |  |  |

| s <sub>0</sub> , s <sub>1</sub>                       |      |      | 40   | μА    |                 |      |                | 4.5∨           | 4.5V           |              |                  |         |       |  |  |  |  |

## $T_A = 25^{\circ} C$ and $V_{CC} = 5.0 V$

|                                                   | i        | LIF  | VITS     |       | TEST CONDITIONS |                |                |                |                |              |                  |         |       |  |  |  |  |

|---------------------------------------------------|----------|------|----------|-------|-----------------|----------------|----------------|----------------|----------------|--------------|------------------|---------|-------|--|--|--|--|

| CHARACTERISTICS                                   | MIN.     | TYP. | MAX.     | UNITS | An              | B <sub>n</sub> | C <sub>n</sub> | s <sub>o</sub> | s <sub>1</sub> | DATA<br>COMP | OUTPUT<br>ENABLE | OUTPUTS | NOTES |  |  |  |  |

| Propagation Delay (8263)                          |          |      |          |       |                 |                |                |                |                |              |                  |         |       |  |  |  |  |

| A <sub>n</sub> to f <sub>n</sub>                  |          | 17   | 26       | ns    |                 |                | Ì              |                |                |              |                  |         | 10    |  |  |  |  |

| S <sub>0</sub> , S <sub>1</sub> to f <sub>n</sub> |          | 25   | 36       | ns    |                 |                |                |                |                | ŀ            |                  |         | 10    |  |  |  |  |

| DC to f <sub>n</sub>                              |          | 17   | 26       | ns    |                 |                |                |                |                | 1            |                  |         | 10    |  |  |  |  |

| Propagation Delay (8264)                          | <b>\</b> |      | <b>\</b> | \     |                 |                |                | 1              |                |              |                  |         |       |  |  |  |  |

| A <sub>n</sub> to f <sub>n</sub>                  |          | 25   | 36       | ns    |                 |                | 1              |                |                |              |                  |         | 10    |  |  |  |  |

| S <sub>0</sub> , S <sub>1</sub> to f <sub>n</sub> | i l      | 25   | 36       | ns    |                 |                |                |                | 1              |              |                  |         | 10    |  |  |  |  |

| DC to f                                           |          | 20   | 30       | ns    |                 |                |                |                |                |              |                  |         | 10    |  |  |  |  |

| OE to f <sub>n</sub>                              | l        | 20   | 30       | ns    |                 |                |                | }              | }              |              |                  |         | 10    |  |  |  |  |

| Input Latch Voltage                               |          |      |          |       |                 |                | l              |                |                |              |                  |         |       |  |  |  |  |

| Rating                                            |          |      |          |       |                 |                |                | ļ              |                |              |                  |         |       |  |  |  |  |

| An                                                | 5.5      |      | }        | v     | 10mA            |                |                | ov             | ov             |              |                  |         | 12    |  |  |  |  |

| B <sub>n</sub>                                    | 5.5      |      | <b>,</b> | v     |                 | 10mA           | ļ              | ļ              | ov             |              |                  |         | 12    |  |  |  |  |

| c <sub>n</sub>                                    | 5.5      |      |          | v     |                 |                | 10mA           | ov             |                |              |                  |         | 12    |  |  |  |  |

| s <sub>0</sub>                                    | 5.5      |      | ļ        | V     |                 |                |                | 10mA           |                |              |                  |         | 12    |  |  |  |  |

| s <sub>1</sub> ,                                  | 5.5      |      |          | v     |                 |                |                |                | 10mA           |              |                  |         | 12    |  |  |  |  |

| DC                                                | 5.5      |      | Į        | v     |                 |                | [              |                |                | 10mA         |                  |         | 12    |  |  |  |  |

| OE                                                | 5.5      |      |          | v     |                 |                |                | 1              | 1              | i            | 10mA             |         | 12    |  |  |  |  |

| Output Short Circuit Current                      | -20      |      | -70      |       |                 |                | 1              |                | 1              |              |                  | ov.     |       |  |  |  |  |

| Power/Current Consumption                         |          |      | l        |       |                 |                |                |                | 1              |              |                  |         | 14    |  |  |  |  |

|                                                   |          | 378/ | 420/     | mW/   |                 |                | -              | ov             | -              |              |                  |         |       |  |  |  |  |

| (8263)                                            | ]        | 72   | 80       | mA    |                 |                | -              | 1              | 1              | 1            |                  | Ì       |       |  |  |  |  |

|                                                   | ]        | 400/ | 475/     | mW/   |                 | 1              |                | ov             |                |              |                  |         |       |  |  |  |  |

| (8264)                                            |          | 76   | 90.4     | mA    |                 |                |                | 1              |                | ł            |                  |         |       |  |  |  |  |

#### NOTES:

- All voltage measurements are referenced to the ground termi-1. nal. Terminals not specifically referenced are left electrically

- 2. All measurements are taken with ground pin tied to zero voits.

- Positive current flow is defined as into the terminal referenced.

- Positive NAND Logic Definition: "UP" Level = "1", "DOWN" Level = "0".

- Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased,

- Measurements apply to each gate element independently.

- 7. Capacitance as measured on Boonton Electric Corporation

- Model 75A-S8 Capacitance Bridge or equivalent. f = 1 MHz, Vac = 25m Vrms. All pins not specifically referenced are tied to ground for capacitance tests. Output pins are left open. Output source current is supplied through a resistor to

- ground. Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 10. Refer to AC Test Figure.

- 11. Connect an external 1k  $\pm$  1% resistor from  $V_{CC}$  to the output for this test.

- 12. This test guarantees operation free of input latch-up over the specified operating supply voltage range.

- 13. Manufacturer reserves the right to make design and process changes and improvements.

- V<sub>CC</sub> = 5.25 volts. 14.

8.

## **SCHEMATIC DIAGRAMS**

, A ...

# SCHEMATIC DIAGRAMS (Cont'd)

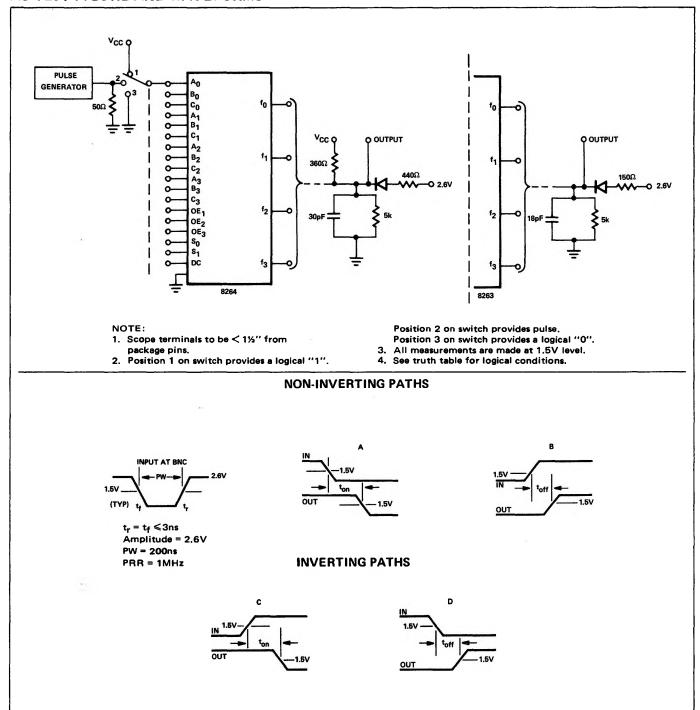

### **AC TESTING**

| Step | Delay                             | Switching Positions |                |    |                |                |                |                |                |                |                |    | Waveform       |    |    |    |    |                |                |    |       |

|------|-----------------------------------|---------------------|----------------|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|----------------|----|----|----|----|----------------|----------------|----|-------|

| No.  |                                   | Driven              |                |    |                |                |                |                |                |                |                |    |                |    |    |    |    | Types          |                |    |       |

|      |                                   | Inputs              | A <sub>0</sub> | В0 | c <sub>0</sub> | A <sub>1</sub> | B <sub>1</sub> | C <sub>1</sub> | A <sub>2</sub> | B <sub>2</sub> | C <sub>2</sub> | А3 | B <sub>3</sub> | C3 | OE | OE | OE | S <sub>0</sub> | S <sub>1</sub> | DC | Types |

| 1    | A <sub>n</sub> to f <sub>n</sub>  | 2                   | 2              | 1  | 1              | 2              | 1              | 1              | 2              | 1              | 1              | 2  | 1              | 1  | 1  | 1  | 1  | 1              | 1              | 1  | C, D  |

| 2    | S <sub>O</sub> to f <sub>n</sub>  | 2                   | 3              | 1  | 1              | 3              | 1              | 1              | 3              | 1              | 1              | 3  | 1              | 1  | 1  | 1  | 1  | 2              | 1              | 1  | A, B  |

| 3    | S <sub>0</sub> to f <sub>n</sub>  | 2                   | 1              | 3  | 1              | 1              | 3              | 1              | 1              | 3              | 1              | 1  | 3              | 1  | 1  | 1  | 1  | 2              | 1              | 1  | C, D  |

| 4    | S <sub>1</sub> to f <sub>n</sub>  | 2                   | 1              | 1  | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1  | 1              | 1  | 1  | 1  | 1  | 1              | 2              | 1  | C, D  |

| 5    | DC to f <sub>n</sub>              | 2                   | 1              | 1  | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1  | 1              | 1  | 1  | 1  | 1  | 1              | 1              | 2  | C, D  |

| 6    | OE <sub>n</sub> to f <sub>n</sub> | 2                   | 1              | 1  | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1  | 1              | 1  | •  | *  | *  | 1              | 1              | 1  | C, D  |

NOTE: Step number 6 is for 8264 only.

### **AC TEST FIGURE AND WAVEFORMS**

<sup>\*</sup> Test one input at a time - others remain at "1".

#### TYPICAL APPLICATIONS

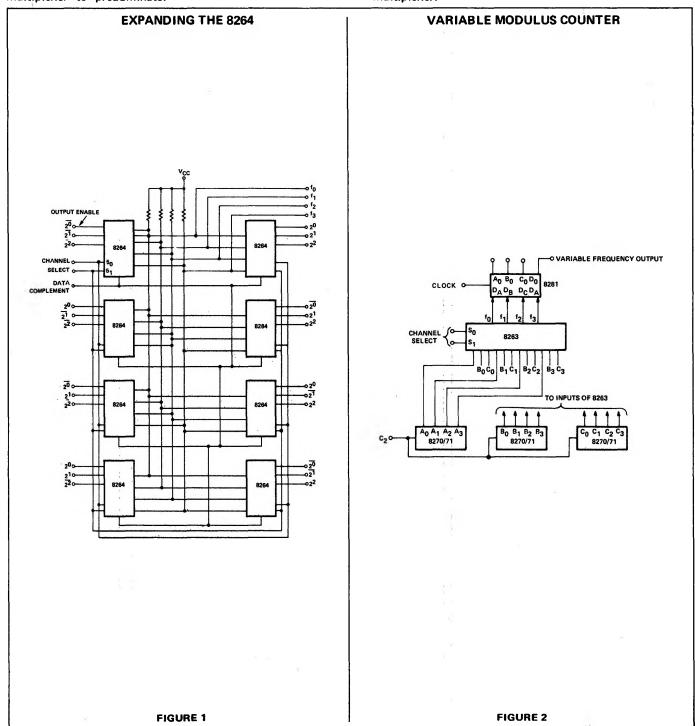

An approach to expanding the 8264 (bare collector output) is shown in Figure 1. The idea is to use common collectors with external pull-up resistors (one resistor for each of the four outputs) and make use of the output enable code.

As can be seen, the channel select lines are tied common, while a different enable code would be used to select a particular 8264. All non-selected 8264's have their outputs in the logic "1" condition, thus allowing the selected multiplexer to predominate.

Figure 2 illustrates a typical example using the 8263 (totem pole output) along with the 8281 (4-bit binary counter) and the 8270/71 (4-bit shift register), to implement a variable modulus counter. The 8270's act as a 3-register memory. The outputs of the 8270's are fed to the corresponding inputs of the 8263. Now there are three different presettable 4-bit words that can be chosen by the 8264. By alternating the channel select codes, the 8281 counter is preset with one of three words and produces an output whose repetition rate is dependent on the inputs from the multiplexer.