# DIGITAL 8000 SERIES TTL/MSI

#### **DESCRIPTION**

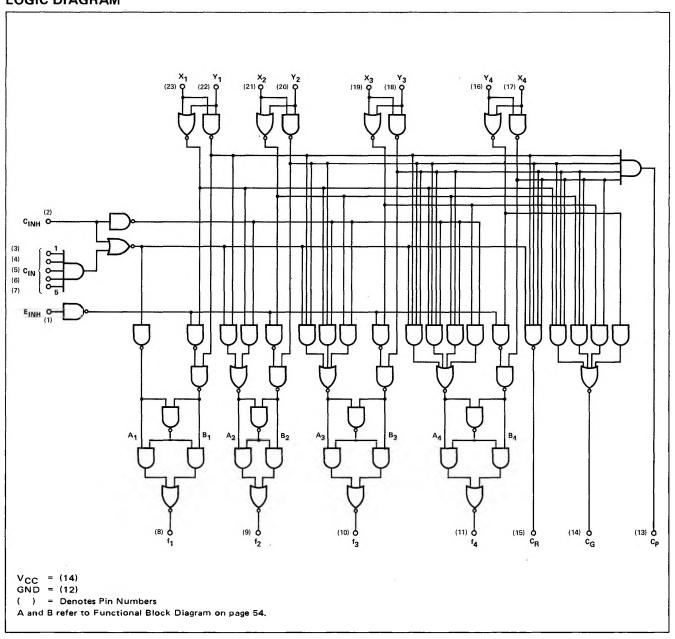

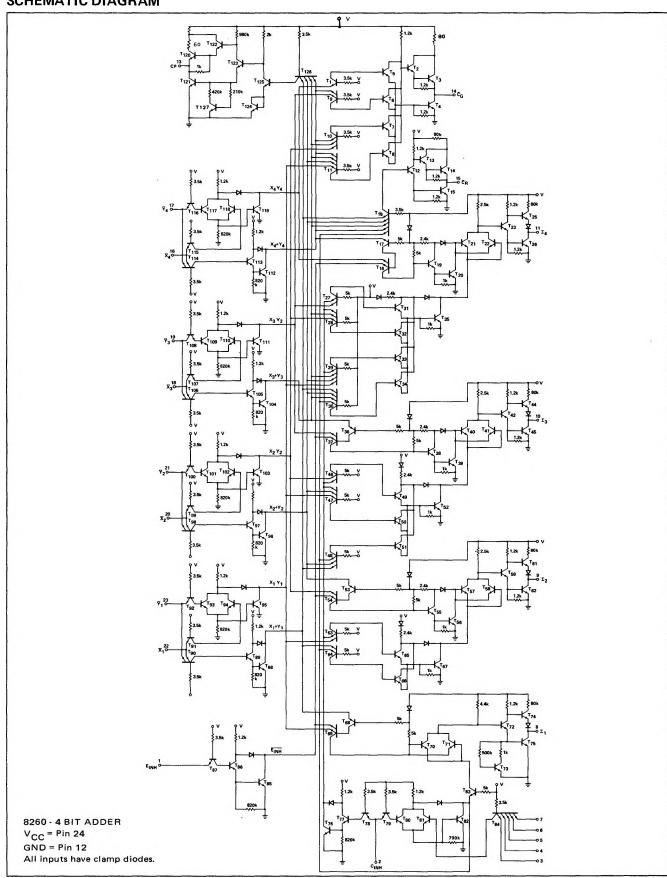

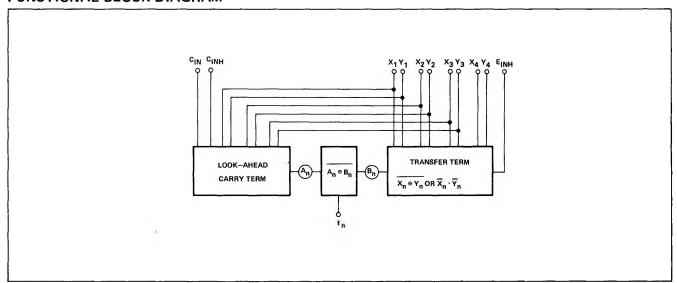

The 8260 Arithmetic Logic Element is a monolithic gate array incorporating four full-adders structured in a look-ahead mode. The device may be used as four mutually independent exclusive NOR or AND gates by proper addressing of the inhibit lines.

As a four-bit adder, the 8260 permits high speed parallel addition of four sets of data and features both simultaneous addition on a character to character and on a bit to bit basis

within the package.

When true input variables are used, the true sum is formed at the f output. Inverted input variables produce the complement of the sum of the true variables.

The carry-outs available are: Internally Generated ( $C_G$ ); Propagated ( $C_p$ ); and Ripple ( $C_R$ ). This gives the 8260 complete flexibility when used in Ripple Carry or Anticipated Carry Adder Systems.

#### **LOGIC DIAGRAM**

#### **ELECTRICAL CHARACTERISTICS** (Over Recommended Operating Temperature And Voltage)

| CHARACTERISTICS                                                |      | Ĺ    | IMITS        |               | TEST CONDITIONS INPUT TERMINALS |      |      |      |      | TE | NOTES          |      |      |    |

|----------------------------------------------------------------|------|------|--------------|---------------|---------------------------------|------|------|------|------|----|----------------|------|------|----|

|                                                                | MIN. | TYP. | MAX.         | UNITS         | x <sub>n</sub>                  | Yn   | CIN  | CINH | EINH | Cp | C <sub>G</sub> | CR   | fn   |    |

| "1" Output Voltage                                             | 2.6  | 3.5  |              | ٧             | 2.0                             | 2.0  | 2.0  | 2.0  | 2.0  |    | -0.8           | -0.8 | -0.8 | 1  |

| "0" Output Voltage                                             |      |      |              |               |                                 |      |      |      |      |    |                |      |      |    |

| f <sub>n</sub> , C <sub>G</sub> and C <sub>R</sub>             |      |      | 0.4          | ٧             | 0.8                             | 0.8  | 0.8  | 0.8  | 0.8  |    | 9.6            | 9.6  | 9.6  | 2  |

| "0" Input Current                                              |      |      |              | •             |                                 |      |      | Ì    |      |    |                |      |      |    |

| X <sub>n</sub> and C <sub>INH</sub>                            | -0.1 |      | -3.2         | mA            | 0.4                             | 5.25 | }    | 0.4  |      |    |                |      |      |    |

| Yn                                                             | -0.1 |      | -3.2         | mA            | 5.25                            | 0.4  |      |      |      |    |                |      |      |    |

| E <sub>INH</sub> & C <sub>IN1</sub> , through C <sub>IN5</sub> | -0.1 |      | -1.6         | mA            |                                 |      | 0.4  |      | 0.4  |    |                |      |      | 3  |

| "1" Input Current                                              |      |      |              |               |                                 |      |      |      |      |    |                |      |      |    |

| X <sub>n</sub> and C <sub>INH</sub>                            |      |      | 80           | μΑ            | 4.5                             | ov   |      | 4.5  |      |    |                |      |      |    |

| Yn                                                             |      |      | 80           | μΑ            | ov                              | 4.5  |      |      |      |    |                |      |      |    |

| $E_{INH}$ & $C_{IN1}$ , through $C_{IN5}$                      |      |      | 40           | μΑ            | ,                               |      | 4.5  |      | 4.5  |    |                |      |      | 4  |

| Input Latch Voltage                                            |      |      |              |               |                                 |      |      |      |      |    |                |      |      |    |

| X <sub>n</sub> and C <sub>INH</sub>                            | 5.5  |      |              | V             | 10mA                            | ov   |      | 10mA |      |    |                |      |      |    |

| Yn                                                             | 5.5  |      |              | ٧             | 0∨                              | 10mA |      |      |      |    |                |      |      |    |

| E <sub>INH</sub> & C <sub>IN1</sub> , through C <sub>IN5</sub> | 5.5  |      |              | V             |                                 |      | 10mA | 1    | 10mA |    |                |      |      | 4  |

| Power/Current Consumption                                      |      |      | 400/<br>76.2 | 600/<br>114.1 | mW/<br>mA                       |      |      |      |      |    |                |      |      | 15 |

## $T_A = 25^{\circ} C$ and $V_{CC} = 5.0 V$

| CHARACTERISTICS                                       |      | L    | IMITS |       | TEST CONDITIONS INPUT TERMINALS |     |     |      |      | OUTPUT<br>TERMINALS (mA) |                |    |    | NOTES |

|-------------------------------------------------------|------|------|-------|-------|---------------------------------|-----|-----|------|------|--------------------------|----------------|----|----|-------|

|                                                       | MIN. | TYP. | MAX.  | UNITS | x <sub>n</sub>                  | Yn  | CIN | CINH | EINH | С <sup>р</sup>           | C <sub>G</sub> | CR | fn |       |

| Propagation Delay                                     |      |      |       |       |                                 |     |     |      |      |                          | 1              |    |    | }     |

| $X_n$ , $Y_n$ and $C_{IN}$ to $C_R$                   |      | 14   | 20    | ns    | !                               |     |     |      |      |                          | 1              |    |    | 14    |

| $X_n$ and $Y_n$ to Cp and $C_G$                       | -    | 14   | 20    | ns    |                                 |     |     | 1    |      |                          |                |    |    | 14    |

| $X_n$ and $Y_n$ to $f_n$                              |      | 24   | 33    | ns    |                                 |     |     |      |      |                          |                |    |    | 14    |

| C <sub>IN</sub> to f <sub>n</sub>                     |      | 14   | 22    | ns    | 1                               |     |     |      |      |                          | ļ              |    | }  | 14    |

| Output Short Circuit Current                          |      |      |       |       |                                 | ļ   |     |      |      |                          | }              |    |    | j     |

| $f_{\sf n}$ , ${\sf C}_{\sf G}$ and ${\sf C}_{\sf R}$ | -20  |      | -70   | mA    | 5.0                             | 5.0 | 5.0 | 5.0  | 5.0  |                          | ov             | 0∨ | 0∨ | 13    |

| Ср                                                    | -40  |      | -90   | mA    | ٥٧                              |     |     |      |      | 0٧                       |                |    |    |       |

### NOTES:

- Output source current is supplied through a resistor to around.

- Output sink current is supplied through a resistor to  $V_{CC}$ . When testing for separate  $C_{1N}$  inputs, tie the remaining

- $c_{1N}$  inputs to  $v_{CC}.$  When testing for separate  $c_{1N}$  inputs, tie the remaining C<sub>IN</sub> inputs to ground.

- Keep unused inputs tied to V<sub>CC</sub> unless otherwise specified. All voltage and capacitance measurements are referenced to 6. the ground terminal.

- All measurements are taken with ground pin tied to  $^{\prime\prime}0^{\prime\prime}$  volts. 7.

- Positive current flow is defined as into the terminal referenced.

- 9. Positive logic definition:

- "UP" Level = "1", "DOWN" Level = "0".

- Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased.

- Manufacturer reserves the right to make design and process changes and improvements.

- 12. Input latch voltage test guarantees operation free of input latch-up over the specified operating power supply voltage range.

- 13. Ground one output at a time.

- 14. Measure switching times at 1.5 volt level.

- $V_{CC} = 5.25V.$ 15.

### **SCHEMATIC DIAGRAM**

### **MODE OF OPERATION**

|                                        | Least Significant  | CONT | ROLS |                                                      |             |

|----------------------------------------|--------------------|------|------|------------------------------------------------------|-------------|

| INPUTS                                 | CIN Inputs to be * | CINH | EINH | 1                                                    |             |

| X <sub>n</sub> , Y <sub>n</sub>        | 0                  | 0    | 0    | $\Sigma_{n}$                                         | Add         |

|                                        | 0                  | 0    | 1    |                                                      | Not Used    |

|                                        | 0                  | 1    | 0    | $X_nY_n + \overline{X}_n\overline{Y}_n$              | Coincidence |

|                                        | 0                  | 1    | 1    | $X_nY_n$                                             | AND         |

| $\overline{X}_{n'}$ $\overline{Y}_{n}$ | 1                  | 0    | 0    | $\overline{\Sigma}_n$                                | Add         |

| 1                                      | 1                  | 0    | 1    |                                                      | Not Used    |

|                                        | 1                  | 1    | 0    | $\overline{X}_{n}\overline{Y}_{n}$<br>+ $X_{n}Y_{n}$ | Coincidence |

|                                        | 1                  | 1    | 1    | $\overline{X}_n\overline{Y}_n$                       | AND         |

<sup>\*</sup>Least significant of a "Multiple Package" adder system.

### **FUNCTIONAL BLOCK DIAGRAM**

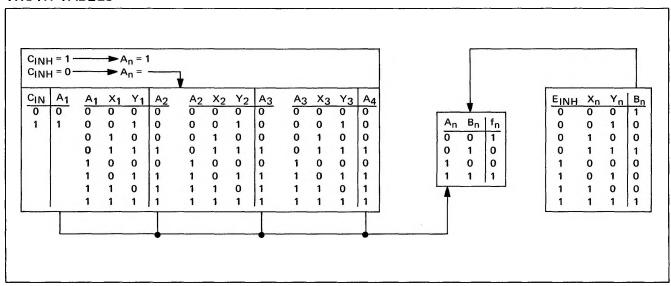

### TRUTH TABLES

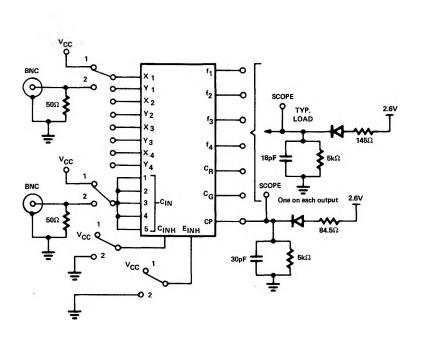

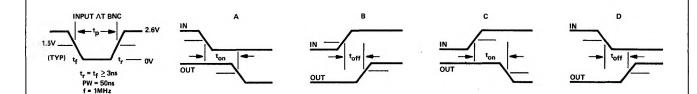

### **AC TEST FIGURE AND WAVEFORMS**

NOTE: Scope terminals to be ≤ ½" from Package Pins.

| STEP DELAY<br>NO. FROM-TO |                                                  | SWITCH POSITION |                |                  |                |    |                |                |                |                |     |      |      |      |

|---------------------------|--------------------------------------------------|-----------------|----------------|------------------|----------------|----|----------------|----------------|----------------|----------------|-----|------|------|------|

|                           | DRIVEN                                           |                 |                | WAVEFORM<br>TYPE |                |    |                |                |                |                |     |      |      |      |

|                           |                                                  | INPUTS          | X <sub>1</sub> | Υ <sub>1</sub>   | x <sub>2</sub> | Y2 | х <sub>3</sub> | Y <sub>3</sub> | X <sub>4</sub> | Y <sub>4</sub> | CIN | EINH | CINH |      |

| 1                         | X <sub>n</sub> to C <sub>R</sub>                 | 2               | 2              | 1                | 2              | 1  | 2              | 1              | 2              | 1              | 2   | 2    | 2    | A, B |

|                           | X <sub>n</sub> to Cp                             |                 |                |                  |                |    |                |                | L              |                |     |      |      | C, D |

| 2                         | Yn to CR                                         | 2               | Ι,             | 2                | ,              | 2  |                | 2              | ,              | 2              | 2   | 2    | 2    | А, В |

| •                         | Yn to Cp                                         | _               | ١.             | -                | •              | _  | •              |                | l '            |                | 1   | 1    |      | C, D |

| 3                         | X <sub>n</sub> ,Y <sub>n</sub> to f <sub>n</sub> | 2               | 1              | 1                | 1              | 1  | 1              | 1              | 1              | 1              | 1   | 1    | 1    | A, B |

| 4                         | CIN to CR                                        | 2               | 2              | 2                | 2              | 2  | 2              | 2              | 2              | 2              | 2   | 2    | 2    | A, B |

| 5                         | C <sub>IN</sub> to f <sub>n</sub>                | 2               | 1              | 2                | 1              | 2  | 1              | 2              | 1              | 2              | 2   | 2    | 2    | C, D |

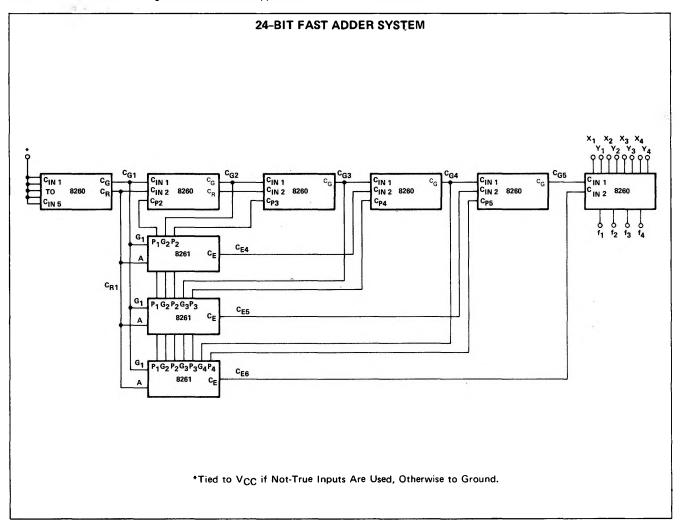

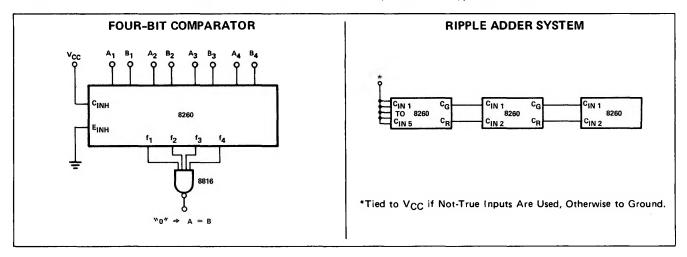

### TYPICAL APPLICATIONS

The 8260 contains the control logic necessary to allow operation as a general purpose arithmetic logic device. Below, the internal carries are inhibited to effect Exclusive-NOR or coincidence operation. The 8260 may also be operated as four independent

AND gates to implement masking and similar requirements of micro-programming.

The Ripple Adder System is the simplest but also the slowest application of the 8260. The typical total addition time (input to sum output for 12-bit ripple adder is 42ns.).

The Fast Adder System provides complete carry look-ahead addition for words to 24 bits in length and is the fastest application of

the 8260 units. The typical total addition time for a 24 bit fast adder is 42ns.