# 8224

# CLOCK GENERATOR AND DRIVER FOR 8080A CPU

- Single Chip Clock Generator/Driver for 8080A CPU

- Power-Up Reset for CPU

- Ready Synchronizing Flip-Flop

- Advanced Status Strobe

- Oscillator Output for External System Timing

- Crystal Controlled for Stable System Operation

- Reduces System Package Count

The 8224 is a single chip clock generator/driver for the 8080A CPU. It is controlled by a crystal, selected by the designer, to meet a variety of system speed requirements.

Also included are circuits to provide power-up reset, advance status strobe and synchronization of ready.

The 8224 provides the designer with a significant reduction of packages used to generate clocks and timing for 8080A.

#### PIN CONFIGURATION

15> XTAL1 OSCILLATO 12> osc 14> XTAL2 13> TANK 11> CLOCK GEN. ÷9 10> \$2(TTL) 6> \$2D \$1 STSTB 7> 5> SYNC RESIN  $|2\rangle$ Ð SCHMITT RESET 1> 3> RDYIN READY 4>

#### **PIN NAMES**

| RESIN | RESET INPUT  | XTAL 1    | ( CONNECTIONS                  |  |  |

|-------|--------------|-----------|--------------------------------|--|--|

| RESET | RESET OUTPUT | XTAL 2    | FOR CRYSTAL                    |  |  |

| RDYIN | READY INPUT  | TANK      | USED WITH OVERTONE XTAL        |  |  |

| READY | READY OUTPUT | OSC       | OSCILLATOR OUTPUT              |  |  |

| SYNC  | SYNC INPUT   | \$2 (TTL) | φ <sub>2</sub> CLK (TTL LEVEL) |  |  |

| STSTB | STATUS STB   | Vcc       | +5V                            |  |  |

|       | (ACTIVE LOW) | VDD       | +12V                           |  |  |

| ¢1    | 8080         | GND       | ov                             |  |  |

| ¢2    | CLOCKS       | L         |                                |  |  |

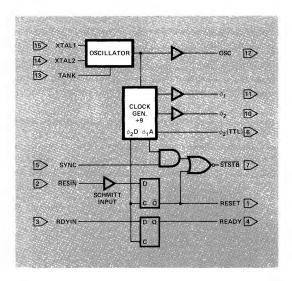

#### **BLOCK DIAGRAM**

# intel

#### FUNCTIONAL DESCRIPTION

#### General

The 8224 is a single chip Clock Generator/Driver for the 8080A CPU. It contains a crystal-controlled oscillator, a "divide by nine" counter, two high-level drivers and several auxiliary logic functions.

#### Oscillator

The oscillator circuit derives its basic operating frequency from an external, series resonant, fundamental mode crystal. Two inputs are provided for the crystal connections (XTAL1, XTAL2).

The selection of the external crystal frequency depends mainly on the speed at which the 8080A is to be run at. Basically, the oscillator operates at 9 times the desired processor speed.

A simple formula to guide the crystal selection is:

| Crystal Frequency = $\frac{1}{t_{CY}}$ times 9 |                                                        |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| Example 1:                                     | (500ns t <sub>CY</sub> )<br>2mHz times 9 = 18mHz*      |  |  |  |  |

| Example 2:                                     | (800ns t <sub>CY</sub> )<br>1.25mHz times 9 = 11.25mHz |  |  |  |  |

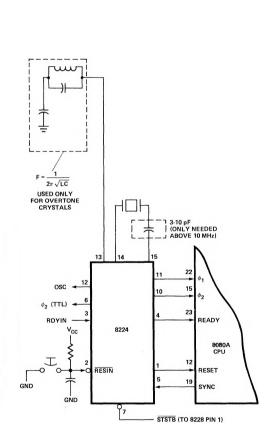

Another input to the oscillator is TANK. This input allows the use overtone mode crystals. This type of crystal generally has much lower "gain" than the fundamental type so an external LC network is necessary to provide the additional "gain" for proper oscillator operation. The external LC network is connected to the TANK input and is AC coupled to ground. See Figure 4.

The formula for the LC network is:

$$F = \frac{1}{2\pi \sqrt{LC}}$$

The output of the oscillator is buffered and brought out on OSC (pin 12) so that other system timing signals can be derived from this stable, crystal-controlled source.

\*When using crystals above 10mHz a small amount of frequency "trimming" may be necessary to produce the exact desired frequency. The addition of a small selected capacitance (3pF - 10pF) in series with the crystal will accomplish this function.

#### **Clock Generator**

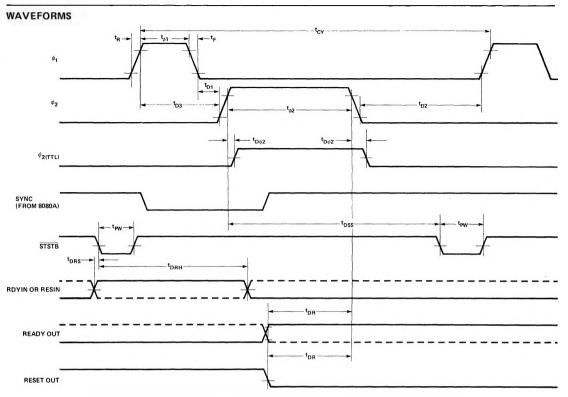

The Clock Generator consists of a synchronous "divide by nine" counter and the associated decode gating to create the waveforms of the two 8080A clocks and auxiliary timing signals.

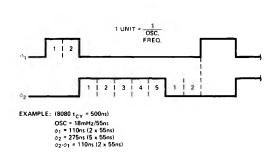

The waveforms generated by the decode gating follow a simple 2-5-2 digital pattern. See Figure 2. The clocks generated; phase 1 and phase 2, can best be thought of as consisting of "units" based on the oscillator frequency. Assume that one "unit" equals the period of the oscillator frequency. By multiplying the number of "units" that are contained in a pulse width or delay, times the period of the oscillator frequency, the approximate time in nanoseconds can be derived.

The outputs of the clock generator are connected to two high level drivers for direct interface to the 8080A CPU. A TTL level phase 2 is also brought out  $\phi_2$  (TTL) for external timing purposes. It is especially useful in DMA dependant activities. This signal is used to gate the requesting device onto the bus once the 8080A CPU issues the Hold Acknowledgement (HLDA).

Several other signals are also generated internally so that optimum timing of the auxiliary flip-flops and status strobe (STSTB) is achieved.

#### **STSTB** (Status Strobe)

At the beginning of each machine cycle the 8080A CPU issues status information on its data bus. This information tells what type of action will take place during that machine cycle. By bringing in the SYNC signal from the CPU, and gating it with an internal timing signal ( $\phi$ 1A), an active low strobe can be derived that occurs at the start of each machine cycle at the earliest possible moment that status data is stable on the bus. The STSTB signal connects directly to the 8228 System Controller.

The power-on Reset also generates  $\overline{\text{STSTB}}$ , but of course, for a longer period of time. This feature allows the 8228 to be automatically reset without additional pins devoted for this function.

#### Power-On Reset and Ready Flip-Flops

A common function in 8080A Microcomputer systems is the generation of an automatic system reset and start-up upon initial power-on. The 8224 has a built in feature to accomplish this feature.

An external RC network is connected to the  $\overline{\text{RESIN}}$  input. The slow transition of the power supply rise is sensed by an internal Schmitt Trigger. This circuit converts the slow transition into a clean, fast edge when its input level reaches a predetermined value. The output of the Schmitt Trigger is connected to a "D" type flip-flop that is clocked with  $\phi$ 2D (an internal timing signal). The flip-flop is synchronously reset and an active high level that complies with the 8080A input spec is generated. For manual switch type system Reset circuits, an active low switch closing can be connected to the RESIN input in addition to the power-on RC netnetwork.

The READY input to the 8080A CPU has certain timing specifications such as "set-up and hold" thus, an external synchronizing flip-flop is required. The 8224 has this feature built-in. The RDYIN input presents the asynchronous "wait request" to the "D" type flip-flop. By clocking the flip-flop with  $\phi$ 2D, a synchronized READY signal at the correct input level, can be connected directly to the 8080A.

The reason for requiring an external flip-flop to synchronize the "wait request" rather than internally in the 8080 CPU is that due to the relatively long delays of MOS logic such an implementation would "rob" the designer of about 200ns during the time his logic is determining if a "wait" is necessary. An external bipolar circuit built into the clock generator eliminates most of this delay and has no effect on component count.

#### **D.C. Characteristics**

|                    | Parameter                                                      | Limits     |      |      |       |                                                                      |

|--------------------|----------------------------------------------------------------|------------|------|------|-------|----------------------------------------------------------------------|

| Symbol             |                                                                | Min.       | Тур. | Max. | Units | Test Conditions                                                      |

| ۱ <sub>F</sub>     | Input Current Loading                                          |            |      | 25   | mA    | V <sub>F</sub> = .45V                                                |

| IR                 | Input Leakage Current                                          |            |      | 10   | μA    | V <sub>R</sub> = 5.25V                                               |

| V <sub>C</sub>     | Input Forward Clamp Voltage                                    |            |      | 1.0  | V     | I <sub>C</sub> = -5mA                                                |

| VIL                | Input "Low" Voltage                                            |            |      | .8   | V     | V <sub>CC</sub> = 5.0V                                               |

| VIH                | Input "High" Voltage                                           | 2.6<br>2.0 |      |      | V     | Reset Input<br>All Other Inputs                                      |

| VIH-VIL            | REDIN Input Hysteresis                                         | .25        |      |      | m∨    | V <sub>CC</sub> = 5.0V                                               |

| VOL                | Output "Low" Voltage                                           |            |      | .45  | V     | $(\phi_1, \phi_2)$ , Ready, Reset, STSTB<br>$I_{OL} = 2.5 \text{mA}$ |

|                    |                                                                |            |      | .45  | V     | All Other Outputs<br>I <sub>OL</sub> = 15mA                          |

| VOH                | Output "High" Voltage                                          |            |      |      |       |                                                                      |

|                    | $\phi_1, \phi_2$                                               | 9.4        |      |      | V     | I <sub>OH</sub> = -100μA                                             |

|                    | READY, RESET                                                   | 3.6        |      |      | V     | I <sub>OH</sub> = -100μA                                             |

|                    | All Other Outputs                                              | 2.4        |      |      | V     | I <sub>OH</sub> = -1mA                                               |

| lsc <sup>[1]</sup> | Output Short Circuit Current<br>(All Low Voltage Outputs Only) | -10        |      | -60  | mA    | V <sub>O</sub> = 0V<br>V <sub>CC</sub> = 5.0V                        |

| lcc                | Power Supply Current                                           |            |      | 115  | mA    |                                                                      |

| IDD                | Power Supply Current                                           |            |      | 12   | mA    |                                                                      |

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ;  $V_{CC} = +5.0V \pm 5\%$ ;  $V_{DD} = +12V \pm 5\%$ .

Note: 1. Caution,  $\phi_1$  and  $\phi_2$  output drivers do not have short circuit protection

#### CRYSTAL REQUIREMENTS

Tolerance: .005% at 0°C -70°C Resonance: Series (Fundamental)\* Load Capacitance: 20-35pF Equivalent Resistance: 75-20 ohms Power Dissipation (Min): 4mW

\*With tank circuit use 3rd overtone mode.

## A.C. Characteristics

$V_{CC}$  = +5.0V ± 5%;  $V_{DD}$  = +12.0V ± 5%;  $T_A$  = 0°C to 70°C

|                  | Parameter                            | Limits                  |          |                              |       | Test                                                                                 |

|------------------|--------------------------------------|-------------------------|----------|------------------------------|-------|--------------------------------------------------------------------------------------|

| Symbol           |                                      | Min.                    | Тур.     | Max.                         | Units | Conditions                                                                           |

| t <sub>ø1</sub>  | $\phi_1$ Pulse Width                 | 2tcy<br>9 - 20ns        | ·        |                              |       |                                                                                      |

| t <sub>ø2</sub>  | $\phi_2$ Pulse Width                 | <u>5tcy</u> - 35ns      |          |                              |       |                                                                                      |

| t <sub>D1</sub>  | $\phi_1$ to $\phi_2$ Delay           | 0                       |          |                              | ns    |                                                                                      |

| t <sub>D2</sub>  | $\phi_2$ to $\phi_1$ Delay           | $\frac{2tcy}{9}$ - 14ns |          |                              | ]     | C <sub>L</sub> = 20pF to 50pl                                                        |

| t <sub>D3</sub>  | $\phi_1$ to $\phi_2$ Delay           | 2tcy<br>9               |          | $\frac{2tc\gamma}{9}$ + 20ns | ]     |                                                                                      |

| tR               | $\phi_1$ and $\phi_2$ Rise Time      |                         |          | 20                           | ]     |                                                                                      |

| tF               | $\phi_1$ and $\phi_2$ Fall Time      |                         |          | 20                           | 1     |                                                                                      |

| t <sub>Dφ2</sub> | $\phi_2$ to $\phi_2$ (TTL) Delay     | -5                      |          | +15                          | ns    | φ <sub>2</sub> TTL,CL=30<br>R <sub>1</sub> =300Ω<br>R <sub>2</sub> =600Ω             |

| t <sub>DSS</sub> | $\phi_2$ to STSTB Delay              | <u>6tcy</u> - 30ns<br>9 |          | 6tcy<br>9                    |       |                                                                                      |

| tpw              | STSTB Pulse Width                    | <u>tcy</u> - 15ns       |          |                              |       | STSTB, CL=15pl<br>R <sub>1</sub> = 2K                                                |

| tDRS             | RDYIN Setup Time to<br>Status Strobe | 50ns - <u>4tcy</u><br>9 |          |                              |       | $R_2 = 4K$                                                                           |

| tDRH             | RDYIN Hold Time<br>After STSTB       | 4tcy<br>9               | ·        |                              | ]     |                                                                                      |

| t <sub>DR</sub>  | RDYIN or RESIN to $\phi_2$ Delay     | 4tcγ<br>9 - 25ns        |          |                              |       | Ready & Reset<br>CL=10pF<br>R <sub>1</sub> =2K<br>R <sub>2</sub> =4K                 |

| tCLK             | CLK Period                           |                         | tcy<br>9 |                              |       |                                                                                      |

| f <sub>max</sub> | Maximum Oscillating<br>Frequency     | 18.432                  |          |                              | MHz   |                                                                                      |

| C <sub>in</sub>  | Input Capacitance                    |                         |          | 8                            | pF    | V <sub>CC</sub> =+5.0V<br>V <sub>DD</sub> =+12V<br>V <sub>BIAS</sub> =2.5V<br>f=1MHz |

VOLTAGE MEASUREMENT POINTS:  $\phi_1$ ,  $\phi_2$  Logic "0" = 1.0V, Logic "1" = 8.0V. All other signals measured at 1.5V.

## EXAMPLE:

## A.C. Characteristics (For t<sub>CY</sub> = 488.28 ns)

| $T_A = 0^\circ C t$ | o 70°C; V <sub>CC</sub> | = +5V ± 5%; | V <sub>DD</sub> = +12V ± 5% |

|---------------------|-------------------------|-------------|-----------------------------|

|---------------------|-------------------------|-------------|-----------------------------|

|                  | Parameter                                | Limits |      |        |       |                                        |

|------------------|------------------------------------------|--------|------|--------|-------|----------------------------------------|

| Symbol           |                                          | Min.   | Тур. | Max.   | Units | Test Conditions                        |

| t <sub>ø1</sub>  | $\phi_1$ Pulse Width                     | 89     |      |        | ns    | t <sub>CY</sub> =488.28ns              |

| t <sub>ø2</sub>  | $\phi_2$ Pulse Width                     | 236    |      |        | ns    |                                        |

| t <sub>D1</sub>  | Delay $\phi_1$ to $\phi_2$               | 0      |      |        | ns    |                                        |

| t <sub>D2</sub>  | Delay $\phi_2$ to $\phi_1$               | 95     |      |        | ns    | $\phi_1 \& \phi_2$ Loaded to           |

| t <sub>D3</sub>  | Delay $\phi_1$ to $\phi_2$ Leading Edges | 109    |      | 129    | ns    | C <sub>L</sub> = 20 to 50pF            |

| t <sub>r</sub>   | Output Rise Time                         |        |      | 20     | ns    |                                        |

| t <sub>f</sub>   | Output Fall Time                         |        |      | 20     | ns    |                                        |

| tDSS             | $\phi_2$ to STSTB Delay                  | 296    |      | 326    | ns    |                                        |

| t <sub>Dφ2</sub> | $\phi_2$ to $\phi_2$ (TTL) Delay         | -5     |      | +15    | ns    |                                        |

| tpw              | Status Strobe Pulse Width                | 40     |      |        | ns    | Ready & Reset Loaded                   |

| t <sub>DRS</sub> | RDYIN Setup Time to STSTB                | -167   |      |        | ns    | to 2mA/10pF                            |

| tDRH             | RDYIN Hold Time after STSTB              | 217    |      |        | ns    | All measurements                       |

| tDR              | READY or RESET<br>to $\phi_2$ Delay      | 192    |      |        | ns    | referenced to 1.5V<br>unless specified |

| f                | Oscillator Frequency                     |        |      | 18.432 | MHz   | otherwise.                             |