## Schottky Bipolar 8210

# TTL-TO-MOS LEVEL SHIFTER AND HIGH VOLTAGE CLOCK DRIVER

- Four Low Voltage Drivers

- One High Voltage Driver

- TTL and DTL Compatible Inputs

- Outputs Compatible with 8107A MOS Memories

- Operates from Standard Bipolar and MOS Power Supplies

- Maximum MOS Device Protection Output Clamp Diodes

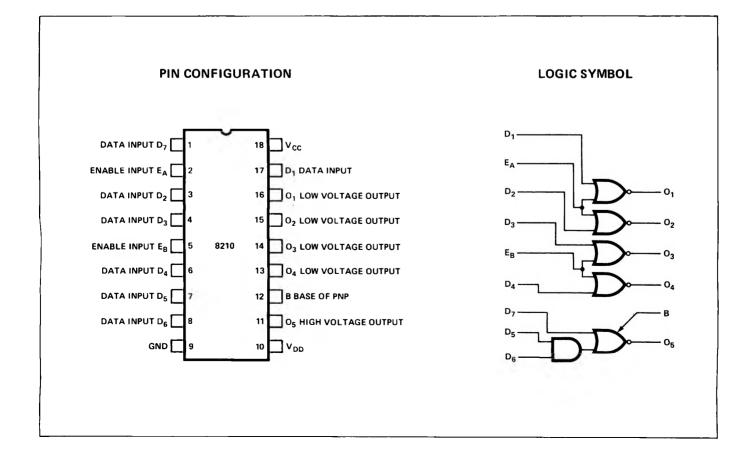

The Intel®8210 is a Bipolar-to-MOS level shifter and high voltage driver which accepts TTL and DTL inputs. It contains four (4) low voltage drivers and one high voltage driver, each with current driving capabilities suitable for driving N-channel MOS memory devices. The 8210 is particularly suitable for driving the 8107A N-channel MOS memory chips. The 8210 operates from the 5 volt and 12 volt power supplies used to bias the memory devices.

The four low voltage drivers feature two common enable inputs per pair of drivers which permits address or data decoding. The high voltage driver swings the 12 volts required to drive the chip enable (clock) input for the 8107A.

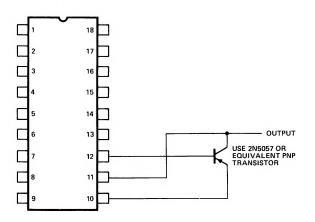

The 8210 high voltage driver requires an externally connected PNP transistor. The PNP base is connected to pin 12, the collector to pin 11, and the emitter to pin 10 or  $V_{DD}$ . The use of a fast switching, high voltage, high current gain PNP, like the 2N5057 is recommended.

## **A.C. Characteristics** $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = 5.0V \pm 5\%$ , $V_{DD} = 12V \pm 5\%$

| Symbol            | Parameter                                                     | Min. | Тур. | Max. | Unit |  |

|-------------------|---------------------------------------------------------------|------|------|------|------|--|

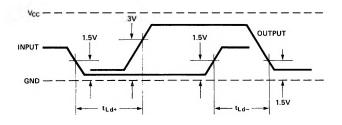

| t <sub>Ld+</sub>  | t <sub>Ld+</sub> Delay Plus Rise Time for Low Voltage Drivers |      | 13   | 20   | ns   |  |

| t <sub>Ld</sub> _ | Delay Plus Fall Time for Low Voltage Drivers                  | 5    | 13   | 20   | ns   |  |

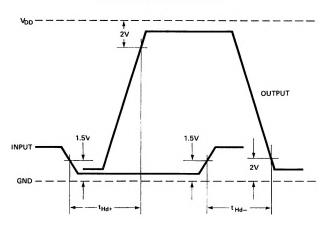

| t <sub>Hd+</sub>  | Delay Plus Rise Time for High Voltage Driver                  | 10   | 30   | 40   | ns   |  |

| t <sub>Hd</sub> _ | Delay Plus Fall Time for High Voltage Driver                  | 10   | 30   | 40   | ns   |  |

## Capacitance\* T<sub>A</sub> = 25°C

| Symbol          | Test              | Тур. | Max. |  |

|-----------------|-------------------|------|------|--|

| C <sub>IN</sub> | Input Capacitance | 6pF  | 12pF |  |

<sup>\*</sup>This parameter is periodically sampled and is not 100% tested. Condition of measurement is  $f=1\,\text{MHz}$ ,  $V_{bias}=2V$ ,  $V_{CC}=0V$ , and  $T_A=25^{\circ}C$ .

#### A.C. CONDITIONS OF TEST

Test Load: C<sub>L</sub> = 200 pF for Low Voltage Drivers,

C<sub>L</sub> = 350 pF for High Voltage Drivers Input Pulse Amplitudes: 3.0V

Input Pulse Rise and Fall Times: 5 ns between

1 volt and 2 volts

Measurement Points: See Waveforms

## **Waveforms**

#### HIGH VOLTAGE DRIVER

#### LOW VOLTAGE DRIVER

## **Application**

#### HIGH VOLTAGE OUTPUT CONNECTIONS

## **Absolute Maximum Ratings\***

| Temperature Under Bias                     | All Input Voltages −1.0 to +5.5V          |

|--------------------------------------------|-------------------------------------------|

| Storage Temperature65°C to +150°C          | Outputs for Low Voltage Drivers0.5 to +7V |

| Supply Voltage, V <sub>CC</sub> 0.5 to +7V | Outputs for Clock Driver1.0 to +13V       |

| Supply Voltage, V <sub>DD</sub>            | Power Dissipation at 25°C 2W              |

<sup>\*</sup>COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **D.C. Characteristics** $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = 5.0V \pm 5\%$ , $V_{DD} = 12V \pm 5\%$

| Symbol           | Parameter                                            | Min.                  | Max.                  | Unit | Test Conditions                                   |

|------------------|------------------------------------------------------|-----------------------|-----------------------|------|---------------------------------------------------|

| I <sub>FD</sub>  | Data Input Load Current                              |                       | -0.25                 | mA   | V <sub>F</sub> = 0.45V                            |

| IFE              | Enable Input Load Current                            |                       | -0.50                 | mA   | V <sub>F</sub> = 0.45V                            |

| I <sub>RD</sub>  | Data Input Leakage Current                           |                       | 10                    | μΑ   | V <sub>R</sub> = 12.6V                            |

| I <sub>RE</sub>  | Enable Input Leakage Current                         |                       | 20                    | μΑ   | V <sub>R</sub> = 12.6V                            |

| - V-             | Output Low Voltage                                   |                       | 0.45                  | V    | I <sub>OL</sub> = 3mA, V <sub>IH</sub> = 2V       |

| VOL              | for all Drivers                                      | -1.0                  |                       | V    | I <sub>OL</sub> = -5mA                            |

| V.               | Output High Voltage                                  | V <sub>CC</sub> -1.0  |                       | V    | $I_{OH} = -1 \text{ mA}, V_{IL} = 0.8 \text{ V}$  |

| V <sub>OH1</sub> | for Low Voltage Drivers                              | - 6                   | V <sub>CC</sub> +1.0  | V    | I <sub>OH</sub> = 5mA                             |

| · · · · · ·      | Output High Voltage for High Voltage Driver          | V <sub>DD</sub> -0.75 |                       | V    | $I_{OH} = -1  \text{mA},  V_{IL} = 0.8  \text{V}$ |

| V <sub>OH2</sub> |                                                      |                       | V <sub>DD</sub> + 0.5 | V    | I <sub>OH</sub> = 5mA                             |

| I <sub>01</sub>  | Pulsed Output Sink Current for Low Voltage Drivers   | 75                    |                       | mA   | V <sub>O</sub> = 2V, V <sub>IH</sub> = 2V         |

| I <sub>O2</sub>  | Pulsed Output Sink Current for High Voltage Driver   | 100                   |                       | mA   | V <sub>O</sub> = 3V, V <sub>IH</sub> = 2V         |

| l <sub>O3</sub>  | Pulsed Output Source Current for Low Voltage Drivers | -75                   |                       | mA   | Vo = Vcc -1.5V,<br>V <sub>IL</sub> = 0.8V         |

| l <sub>O4</sub>  | Pulsed Output Source Current for High Voltage Driver | -100                  |                       | mA   | $V_{O} = V_{DD} - 3V,$<br>$V_{IL} = 0.8V$         |

| VIL              | Input Low Voltage, All Inputs                        |                       | 0.8                   | V    |                                                   |

| V <sub>IH</sub>  | Input High Voltage, All Inputs                       | 2                     |                       | V    |                                                   |

#### POWER SUPPLY CURRENT DRAIN AND POWER DISSIPATION

All driver outputs are in the state indicated

| Symbol           | Parameter                    | Тур. <sup>[1]</sup> | Max. | Unit | Test Conditions Input states to ensure the following output states: |                        | Additional Test                                     |

|------------------|------------------------------|---------------------|------|------|---------------------------------------------------------------------|------------------------|-----------------------------------------------------|

|                  |                              |                     |      |      | All Low Voltage Outputs                                             | High Voltage<br>Output | Conditions                                          |

| I <sub>CC1</sub> | Current from V <sub>CC</sub> | 26                  | 35   | mA   | Low                                                                 | Low                    |                                                     |

| I <sub>DD1</sub> | Current from V <sub>DD</sub> | 12                  | 16   | mA   | Low                                                                 | Low                    |                                                     |

| P <sub>D1</sub>  | Power Dissipation            | 290                 | 390  | mW   | Low                                                                 | Low                    |                                                     |

| I <sub>CC2</sub> | Current from V <sub>CC</sub> | 21                  | 28   | mA   | Low                                                                 | High                   |                                                     |

| $I_{DD2}$        | Current from V <sub>DD</sub> | 26                  | 35   | mA   | Low                                                                 | High                   |                                                     |

| P <sub>D2</sub>  | Power Dissipation            | 450                 | 600  | mW   | Low                                                                 | High                   | V <sub>CC</sub> = 5.25V,<br>V <sub>DD</sub> = 12.6V |

| Іссз             | Current from V <sub>CC</sub> | 19                  | 25   | mA   | High                                                                | Low                    |                                                     |

| I <sub>DD3</sub> | Current from V <sub>DD</sub> | 12                  | 16   | mA   | High                                                                | Low                    |                                                     |

| P <sub>D3</sub>  | Power Dissipation            | 260                 | 340  | mW   | High                                                                | Low                    |                                                     |

| I <sub>CC4</sub> | Current from V <sub>CC</sub> | 14                  | 18   | mA   | High                                                                | High                   |                                                     |

| I <sub>DD4</sub> | Current from V <sub>DD</sub> | 26                  | 35   | mA   | Ḥigh                                                                | High                   |                                                     |

| $P_{D4}$         | Power Dissipation            | 410                 | 550  | mW   | High                                                                | High                   |                                                     |

<sup>[1]</sup> This parameter is periodically sampled and is not 100% tested. Condition of measurement is  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V$ ,  $V_{DD} = 12V$ .

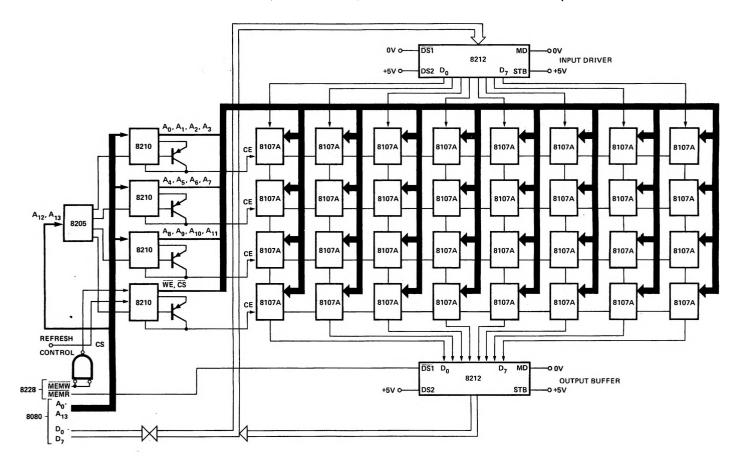

#### Typical System

Below is an example of a 16K x 8 bit memory circuit. Device decoding is done with the CE input. All devices are unselected during refresh with CS input. The 8210, 8205 and 8212 are standard Intel products.